Fターム[5J055DX56]の内容

Fターム[5J055DX56]の下位に属するFターム

DEPP (5)

Fターム[5J055DX56]に分類される特許

141 - 160 / 596

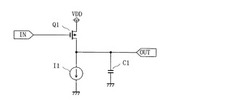

閾値回路

【課題】閾値回路を低消費電力化する。

【解決手段】閾値回路は、ゲート端子が入力端子INに接続され、ソース端子が電源電位VDDに接続され、ドレイン端子が出力端子OUTに接続された第1のPMOSトランジスタQ1と、第1の端子が第1のPMOSトランジスタQ1のドレイン端子および出力端子OUTに接続され、第2の端子が接地された電流制限部I1と、第1の端子が第1のPMOSトランジスタQ1のドレイン端子および出力端子OUTに接続され、第2の端子が接地された電荷蓄積部C1とから構成される。電流制限部I1の電流値は、サブマイクロアンペア以下に設定される。

(もっと読む)

内燃機関制御装置

【課題】電磁負荷を駆動する内燃機関制御装置において、電磁負荷の駆動周期が短い場合でも、該電磁負荷の故障診断精度を向上させ、ノイズに影響されない高速制御を安定して行う。逆起エネルギーの回生回路に対しても、信頼度の高い故障診断を行う。

【解決手段】内燃機関における燃料噴射装置などの電磁負荷の駆動周期が短くなった場合でも高い故障診断精度を確保するため、診断部位の電位を調整するための電流源あるいは電圧源を設ける。加えて、ノイズのような突発的な外乱に影響されない診断精度を確保するため、診断タイミングを最適に設定したり、平均化のための判定回数を増やしたりする。更に、該昇圧回路に回生させる回路の故障診断については、該電磁負荷の駆動用スイッチ素子の入出力電圧もしくは回生電流を検出する。

(もっと読む)

半導体集積回路、半導体集積回路の駆動方法、表示装置および電子機器

【課題】高耐圧化可能な半導体集積回路を提供する。

【解決手段】本発明に係る半導体集積回路は、電源電位と接続された出力ノードと、出力ノードと電源電位より低電位である接地電位との間に直列に接続された第1のnチャネル型トランジスター、第2のnチャネル型トランジスターおよび第3のnチャネル型トランジスターを有し、第1のnチャネル型トランジスターの一端は、接地電位に接続され、他端は、第2のnチャネル型トランジスターの一端に接続され、ゲート端子は、入力ノードに接続され、第2のnチャネル型トランジスターの他端は、第3のnチャネル型トランジスターに接続され、ゲート端子は、電源電位と接地電位との間に位置する第1中間電位に接続され、第3のnチャネル型トランジスターの他端は出力ノードに接続され、ゲート端子は電源電位に接続されている。

(もっと読む)

入力回路および半導体集積回路

【課題】電磁波による誤動作を低減することのできる入力回路および半導体集積回路の提供を図る。

【解決手段】入力端子2に供給される入力信号を受け取る入力回路10aであって、一端が前記入力端子に接続された容量42と、前記入力信号を、当該入力信号と同じ正論理の信号に変換し、前記容量の他端に供給して駆動する容量駆動回路51,52,41と、を有するように構成する。

(もっと読む)

負荷制御装置及びコンデンサのインピーダンス調整方法

【課題】フィルタを構成する部品の大型化や部品点数を増やすことなく、リップルの発生及びノイズの抑制を図る。

【解決手段】FET3がスイッチング動作する場合に発生するノイズを低減するため、電源とグランドとの間,若しくは負荷の一端と電源又はグランドとの間にコンデンサ10〜12を接続し、これらのコンデンサ10〜12について、インピーダンスが最低になる周波数共振点が、前記ノイズの影響を低減する対象となる周波数帯の中心に一致するように、回路に接続されるリード部分のインダクタンスを調整した構成とする。この場合、ディスクリート素子であるコンデンサ10〜12のリードの長さによってリードインダクタンスを調整する。

(もっと読む)

スピーカ駆動システム

【課題】スピーカにスイッチを直列接続し、PWM回路のパルス出力によってスイッチに流す電流を制御するスピーカ駆動システムを提供する。

【解決手段】スピーカのボイスコイルの一方の駆動端子にスイッチ素子の一方の電流端子を接続し、スイッチ素子の制御端子にマイクロコンピュータを接続し、ボイスコイルの他方の駆動端子とスイッチ素子の他方の電流端子との内の一方を回路のグランド端子に、他方を電源端子に接続する。マイクロコンピュータは、PWM回路によってパルス信号のデューティ比を制御し、PWM回路から出力されるパルス信号のデューティ比に応じてスイッチ素子に電流を流すスイッチ制御信号を出力回路から前記制御端子に出力するデータ処理ユニットを有する。データ処理ユニットは無音時のパルス信号のデューティ比を第1値とし、発生させる音に応じて、第1値を中心にパルス信号のデューティ比を変化させるようにPWM回路を制御する。

(もっと読む)

電力用素子の故障検出装置

【課題】電力用素子の故障を簡単な構成で検出可能な故障検出装置を提供する。

【解決手段】故障検出装置1Dは、カソードがIGBTQ1のコレクタに接続される整流素子D7と、一端が整流素子D7のアノードに接続され、他端にエミッタに対して正の電圧が印加される抵抗素子R4と、IGBTQ1の劣化を判定するための劣化判定部2Dとを備える。劣化判定部2Dは、主電流の大きさが予め定める基準電流に一致するときに検出された、整流素子D7のアノードとIGBTQ1のエミッタとの間の監視電圧が、基準電圧V5を超えるか否かを判定する。基準電流は、主電流の大きさが第1の領域と第2の領域との境界である大きさに設定される。第1の領域はコレクタ・エミッタ間の電圧が負の温度依存性を有する領域であり、第2の領域はコレクタ・エミッタ間の電圧が正の温度依存性を有する領域である。

(もっと読む)

ドライバ回路

【課題】出力信号の立ち下がりのスロープ特性をその場で可変できる機能を有するドライバ回路を提供する。

【解決手段】入力信号TXDを受け、駆動出力ノードN1、N2から駆動信号V1、V2を出力する駆動制御回路11、12と、駆動信号V1、V2を受けて駆動されるMOSトランジスタM7、M8を有し、差動出力信号Vdiffを外部負荷に送出する出力バッファ回路13と、駆動制御回路11、12に付加され、入力信号TXDを受け、該入力信号の論理レベルが所定の方向に変化した時にMOSトランジスタM7、M8がオン状態からオフ状態に変化する動作の開始時間を短縮する動作開始加速回路14、15と、動作開始加速回路14、15に付加され、選択信号Vselに応じてMOSトランジスタM7、M8がオン状態からオフ状態に変化する動作の終了時間を可変する動作終了可変回路16、17と、を具備する。

(もっと読む)

半導体素子の駆動装置

【課題】

動作時間の短縮と回路の小型化を図った半導体素子の駆動装置を提供することを課題とする。

【解決手段】

ハイサイド駆動回路は、最終段ハイサイド素子の制御端子に駆動制御信号を供給するためにプッシュプル接続される第1ハイサイド素子及び第1ロウサイド素子を有し、ロウサイド駆動回路は、最終段ロウサイド素子の制御端子に駆動制御信号を供給するためにプッシュプル接続される第2ハイサイド素子及び第2ロウサイド素子を有し、第1ハイサイド素子は、入力信号と第1ロウサイド駆動回路の出力に基づいて駆動され、第1ロウサイド素子は、入力信号とロウサイド駆動回路の出力に基づいて駆動され、第2ハイサイド素子は、入力信号とハイサイド駆動回路の出力に基づいて駆動され、第2ロウサイド素子は、入力信号と第2ハイサイド駆動回路の出力に基づいて駆動される。

(もっと読む)

表示パネルドライバ及びそれを用いた表示装置

【課題】低電圧動作が可能でありながら、中間電源電圧の供給の有無に関わらず動作可能である表示パネルドライバを提供する。

【解決手段】データ線ドライバ3が、出力アンプ回路14と出力端子16A、16Bとを具備する。出力アンプ回路14は、電源電圧VDDと電圧VMLとの供給を受けて、正の駆動電圧を出力する正専用出力段24Aと、電源電圧と接地電圧の間の駆動電圧を出力可能な正負共用出力段28とを備えている。正専用出力段24Aのプルダウン出力トランジスタは、ディプレッション型であり、正負共用出力段28のプルダウン出力トランジスタは、エンハンスメント型である。電圧VMLがVDD/2に設定されたときは、正専用出力段24Aが正の駆動電圧を出力端子16A又は16Bに出力する。電圧VMLが接地電圧VSSに設定されたときは、正負共用出力段28が正の駆動電圧を出力端子16A又は16Bに出力する。

(もっと読む)

二重ゲート電界効果トランジスタを用いたMOSトランジスタ回路およびCMOSトランジスタ回路

【課題】回路を構成する二重ゲート電界効果トランジスタの動作モードを、回路組み上げ後に適宜変更できるようにした二重ゲート電界効果トランジスタを用いたMOSトランジスタ回路およびCMOSトランジスタ回路を提供する。

【解決手段】二重ゲート電界効果トランジスタを用いたMOSトランジスタ回路は、二重ゲート電界効果トランジスタX1(21)の第1ゲートG1に第1の入力信号in1を加え、第2ゲートG2に選択回路11aを接続し、その選択回路11aに第1の入力信号in1と第2の入力信号in2を加え、選択回路11aにより第1の入力信号in1または第2の入力信号in2を選択して第2ゲートG2に加える。第2ゲートG2に切り替えて入力される入力信号に応じて、3端子動作又は4端子動作を行わせる。

(もっと読む)

出力バッファ回路

【課題】出力バッファ回路の出力ノイズを低減し、かつ、応答速度を速くする。

【解決手段】出力電圧VOUTが接地電圧VSSからNORの反転電圧VLに変化する場合、及び、電源電圧VDDからNANDの反転電圧VHに変化する場合、2個のMOSトランジスタの両方が出力電圧VOUTを制御するので、出力電圧VOUTのスルーレートが急峻になる。よって、出力バッファ回路の応答速度が速くなる。また、出力電圧VOUTが電圧(VDD/2)付近で変化する上記以外の場合、1個のMOSトランジスタだけが出力電圧VOUTを制御するので、出力電圧VOUTのスルーレートが緩やかになる。よって、出力バッファ回路の応答速度が遅くなるので、出力ノイズが低減する。

(もっと読む)

半導体集積回路装置

【課題】電圧パルスで振動子を駆動する送信回路において、誤送信や波形オーバーシュートを改善するため出力がハイインピーダンス状態にならない回路構成を提供し、且つ複数チャネルを集積化した半導体集積回路装置を実現する。

【解決手段】最も絶対値の大きい正電圧VPP1及び負電圧VNN1が供給された従来のパルス発生回路部10と、2番目に絶対値が大きい正電圧VPP2が供給されたP型アナログスイッチタイプのパルス発生回路部20と、2番目に絶対値が大きい負電圧VNN2が供給されたN型アナログスイッチタイプのパルス発生回路部30と、接地電位が供給されたN型アナログスイッチタイプの接地レベルダンピング回路部40とを備える送信回路において、10、20、30、及び40がそれぞれ出力端子OUTに接続される。スイッチ制御信号S1〜S5によって10、20、30、及び40を各別にオンオフして超音波振動子50を駆動する。

(もっと読む)

半導体装置

【課題】Pチャンネル型MOSトランジスタをOFFさせる時に、駆動信号生成回路内のプルアップトランジスタと他の素子に流れる貫通電流を抑制できる半導体装置を提供する。

【解決手段】本実施形態の半導体装置は、従来の半導体装置のプルアップトランジスタ20に代えて、NAND素子7を設けた。その結果、プルアップトランジスタ20を排除したことから、プルアップトランジスタ20に起因する従来の半導体装置において課題であった、Pチャンネル型MOSトランジスタ1のOFF時に駆動信号生成回路内のプルアップトランジスタ20と他の論理素子とに生じる貫通電流を抑制できる。

(もっと読む)

半導体集積回路および電源装置

【課題】電源線や接地線に重畳されるスイッチングノイズを低減することのできる半導体集積回路および電源装置の提供を図る。

【解決手段】第1電源線VINと第2電源線GNDとの間に直列に設けられた複数組の第1スイッチ素子Tp1〜Tp3および第2スイッチ素子Tn1〜Tn3を有し、基準電圧Vrに基づいて前記第1および第2スイッチ素子をオン/オフ制御する半導体集積回路であって、前記各第1スイッチ素子を、それぞれ遅延時間を設けて順に制御する制御回路14を有するように構成する。

(もっと読む)

出力バッファ回路および固体撮像素子

【課題】消費電力を低減させることができるようにする。

【解決手段】出力バッファ回路31において、PチャネルMOSトランジスタM4のソースは、プッシュプル回路15のNチャネルMOSトランジスタM6のゲートと接続され、PチャネルMOSトランジスタM4のソース出力によって、NチャネルMOSトランジスタM6が駆動される。また、NチャネルMOSトランジスタM5のソースは、プッシュプル回路15のPチャネルMOSトランジスタM7のゲートと接続され、NチャネルMOSトランジスタM5のソース出力によって、PチャネルMOSトランジスタM7が駆動される。PチャネルMOSトランジスタM4とNチャネルMOSトランジスタM5は、電流源Q11を介して直列に接続されている。本発明は、例えば、固体撮像素子に用いられる出力バッファ回路に適用できる。

(もっと読む)

半導体装置、出力回路、及び、半導体装置における入出力バッファ回路の制御方法

【課題】異なる電源電圧で使用されることが考えられる半導体装置において、好適な出力回路を有する半導体装置を提供する。

【解決手段】少なくとも出力端子の機能を有する信号端子と、電源端子と、電源端子から電源電圧が供給され内部出力信号を受けて信号端子を駆動する第一及び第二の出力バッファ回路を備えた出力回路と、電源電圧を判定し出力回路の動作を制御する電源電圧判定回路と、を備え、電源電圧判定回路が、第1の電位にあると判定したときには、第1の出力バッファ回路を活性化させると共に、第2の出力バッファ回路を非活性化させ、第2の電位にあると判定したときには、前記第1、第2の出力バッファ回路を共に活性化させる。

(もっと読む)

出力バッファ回路

【課題】駆動能力が切替可能であると共に、ESD耐性が高い出力バッファ回路。

【解決手段】出力バッファ回路100において、第1の電源電圧と、第1の電源電圧より低い第2の電源電圧との間に直列に接続された第1導電型トランジスタTRA1と第2導電型トランジスタTRB1は、出力トランジスタを構成する。制御回路110は、トランジスタTRA1とトランジスタTRB1を相補的にオン/オフさせ、かつトランジスタTRA1とトランジスタTRB1をオンさせるときに与えるゲート電圧を複数の値間で切替可能である。

(もっと読む)

ゲート駆動回路

【課題】信頼性を損なうことなくゲート駆動の高速化を実現することができるゲート駆動回路を得る。

【解決手段】インダクタL1にプリチャージした電流を、スイッチ素子S1,S6〜S9及びボディダイオードBDiを備えたスイッチ素子S2〜S5をスイッチングさせることによってNMOSトランジスタQ1及びQ2の各ゲートHVG及びLVGに供給することにより、NMOSトランジスタQ1をオン又はオフさせるゲート遷移と、NMOSトランジスタQ2をオフ又はオンさせるゲート遷移とを連続して行うようにした。

(もっと読む)

出力バッファ回路、入出力バッファ回路及び半導体装置

【課題】出力レベルのスイッチング時に電源電位に発生され得るノイズを低減することのできる出力バッファ回路、入出力バッファ回路及び半導体装置を提供する。

【解決手段】駆動回路2aは、駆動能力が同一のトランジスタTP1,TN1を含む第1駆動部E1と、駆動能力が同一のトランジスタTP2,TN2を含む第2駆動部E2と、駆動能力が同一のトランジスタTP3,TN3を含む第3駆動部E3を備える。これら駆動部E1〜E3内のプルアップ側のトランジスタTP1,TP2,TP3同士の駆動能力及びプルダウン側のトランジスタTN1,TN2,TN3同士の駆動能力は互いに異なる。制御回路3aは、データ信号Aと、駆動能力制御信号B1,B2と、駆動能力選択信号DSとに応じて、駆動能力が異なるプルアップ側のトランジスタとプルダウン側のトランジスタとを相補的にオンさせる信号を生成する第1制御回路40を備える。

(もっと読む)

141 - 160 / 596

[ Back to top ]