Fターム[5J055DX56]の内容

Fターム[5J055DX56]の下位に属するFターム

DEPP (5)

Fターム[5J055DX56]に分類される特許

61 - 80 / 596

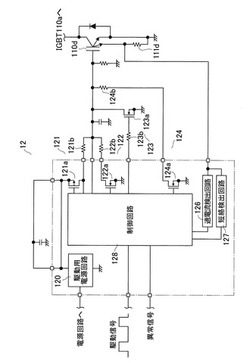

電子装置

【課題】オン駆動用スイッチング素子がオン故障等してスイッチング素子をオフできない異常状態になっても、スイッチング素子の熱破壊を防止することができる電子装置を提供する。

【解決手段】制御回路128は、オン駆動用抵抗121bの端子間電圧に基づいてオン駆動用FET121aに流れる電流を検出する。そして、駆動信号がIGBT110dのオフを指示しているにもかかわらず、オン駆動用FET121aに電流が流れているとき、駆動用電源回路120の動作を停止させ、駆動用電源回路120からの電圧の供給を遮断する。その結果、ゲート電圧がオン、オフする閾値電圧より低くなり、IGBT110dがオフする。従って、オン駆動用スイッチング素子がオン故障等した場合であっても、スイッチング素子の熱破壊を防止することができる。

(もっと読む)

半導体集積回路

【課題】 内部回路の内部ノードが初期状態に設定されたことを精度よく検出し、内部回路が動作を開始するまでの復帰時間を短縮する。

【解決手段】 第1電源スイッチは、内部電源電圧を受けて動作する内部回路の動作を開始させるための第1電源オン信号の活性化中に、外部電源線を内部電源電圧が供給される内部電源線に接続する。第2電源スイッチは、第2電源オン信号の活性化中に、外部電源線を内部電源線に接続する。検知部は、第1電源スイッチのオンにより上昇する内部電源電圧を受けて動作する回路を含む。検知部は、内部電源電圧が第1電圧を超えることにより、内部回路の内部ノードが初期状態に設定されたことを検出したときに第2電源オン信号を活性化する。

(もっと読む)

表示装置の駆動回路

【課題】一導電型のTFTのみを用いて回路を構成することにより工程削減が可能であり

、かつ出力信号の電圧振幅が正常に得られる表示装置の駆動回路を提供する。

【解決手段】出力ノードに接続されているTFT203のゲート−ソース間に容量205

を設け、TFT201、202からなる回路は、ノードαを浮遊状態とする機能を有する

。ノードαが浮遊状態のとき、容量205によるTFT203のゲート−ソース間の容量

結合を利用してノードαの電位をVDDよりも高い電位とし、これによって、TFTのし

きい値に起因する振幅減衰が生ずることなく、正常にVDD−GND間の振幅を持った出

力信号を得ることが出来る。

(もっと読む)

プリドライバ回路、および、駆動回路

【課題】回生電流がモータ等の負荷から駆動回路を構成するプリドライバ回路側に流れても、駆動回路の制御に影響を与えないようにすること。

【解決手段】第1の電源電圧(VM)に接続された第1の駆動トランジスタと、接地に接続された第2の駆動トランジスタとの間の負荷に接続される接続ノード(N1)を出力端子とするブリッジ回路に接続されたプリドライバ回路において、接続ノード(N1)である出力端子に接続された出力モニタ回路を有し、該出力モニタ回路を用いて、出力端子に現れる電圧(Vout)に基づいて電圧のみをフィードバックさせる第1のフィードバック信号(S1)を生成し、第1のフィードバック信号(S1)に基づいて第2のフィードバック信号(S2)を生成して、出力端子に現れる電圧(Vout)が第1の電源電圧(VM)に近づくように、第1の駆動トランジスタを駆動制御する。

(もっと読む)

保護装置、相補型保護装置、信号出力装置、ラッチアップ阻止方法、及びプログラム

【課題】保護対象のスイッチング素子のラッチアップを阻止することができる保護装置、相補型保護装置、信号出力装置及びプログラムを提供する。

【解決手段】PMOSトランジスタ106に対して過電流が流れていない状態でPMOSトランジスタ106を非導通状態にする場合、PMOSトランジスタ20A及びPMOSトランジスタ22の各々を導通状態とするように制御し、PMOSトランジスタ106に対して過電流が流れている状態でPMOSトランジスタ106を非道通状態にする場合、PMOSトランジスタ20Aを導通状態にすると共にPMOSトランジスタ22を非導通状態にするように制御する。

(もっと読む)

CMOS回路及び半導体装置

【課題】しきい電圧VTが小さくてもリーク電流が小さく、また高速にかつ小さな電圧振幅で動作するCMOS回路さらには半導体装置を提供することである。

【解決手段】ゲートとソースを等しい電圧にしたときにドレインとソース間に実質的にサブスレショルド電流が流れるようなMOST(M)を含む出力段回路において、その非活性時には、前記MOST(M)のゲートとソース間を逆バイアスするように該MOST(M)のゲートに電圧を印加する。すなわち、MOST(M)がpチャンネル型の場合にはp型のソースに比べて高い電圧をゲートに印加し、また、MOST(M)がnチャンネル型の場合にはn型のソースに比べて低い電圧をゲートに印加する。活性時には、入力電圧に応じて該逆バイアス状態を保持するかあるいは順バイアス状態に制御する。

(もっと読む)

表示パネルドライバ及びそれを用いた表示装置

【課題】駆動電圧の極性切替(極性反転)が可能な表示パネルドライバの消費電力を低減する表示パネルドライバを提供する。

【解決手段】本発明による表示パネルドライバは、表示パネルの画素に接続された第1データ線及び第2データ線を駆動する出力段として、第1電源範囲で駆動する第1出力段24A及び第4出力段24Bを利用する第1モードと、第1電源範囲よりも広い第2電源範囲で駆動する第2出力段73A及び第3出力段73Bを利用する第2モードとを切替える第1スイッチ回路50と、第2モードの間に、正極性駆動電圧と負極性駆動電圧の出力先となるデータ線6を切替える第2スイッチ回路30とを備える。又、第1出力段24Aは、ウェルが他のNMOSトランジスタから分離され、バックゲートがソースに接続された第1プルダウン出力トランジスタMN18を備える。

(もっと読む)

スイッチ回路装置

【課題】従来技術によるスイッチ回路装置では、ドライバ回路がアンテナ端子とポートとの間に振幅の大きい高周波信号を入力した際に、ドライバ回路内部でリーク電流が発生し、スイッチ回路装置の消費電力が増大する、という問題がある。

【解決手段】ドライバ回路の出力部に、リーク電流抑制回路部を設ける。本発明のスイッチ回路装置によれば、リーク電流抑制回路部が高周波信号の侵入を抑制するので、ドライバ回路は出力状態を保持することが出来て、リーク電流の問題が解決される。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】出力信号遅延を抑制し、消費電流の増大を抑制する出力回路の提供。

【解決手段】入力端子101と出力端子102の電圧を差動入力する差動入力段110からなる差動増幅回路と、第1及び第2の電源端子VDD、VSSに接続された第1及び第2のカレントミラー130、140と、前記第1及び第2のカレントミラーの入力間、出力間に接続される第1、第2の連絡回路150L、150Rと、第1導電型の第1のトランジスタ121と第2導電型の第2のトランジスタ122とからなる出力増幅回路と、前記第1、第2の電源端子VDD、VSSの電源電圧の間の電圧が供給される第3の電源端子VMLの電圧に応じたバイアス信号を受ける第1導電型の第3のトランジスタ161からなる制御回路160と、を備えている。

(もっと読む)

半導体素子の駆動装置及び方法

【課題】半導体素子のスイッチング時において、スイッチング損失の増加を抑制しつつ、サージ電圧を低減すること。

【解決手段】di/dt帰還部23は、IGBT11Uがターンオフするときに、IGBT11のコレクタ電流Icの時間変化に基づいて、帰還電圧VFBを生成する。また、di/dt帰還部23は、IGBT11がターンオンするときに、図示せぬFWDの転流電流IFWDに基づいて、帰還電圧VFBを生成する。このようなdi/dt帰還部23は、帰還電圧VFBを駆動信号の電圧の一部として印加するタイミングを遅延させる遅延フィルタとして、LPF回路201を備えている。LPF201の遅延量、即ちインダクタンスLdを適度に調整することで、還流ダイオードの電圧におけるサージ電圧を低減させることができる。

(もっと読む)

ドライブ制御回路、制御装置、スイッチング電源装置、および、制御方法

【課題】入力電圧の急変や負荷短絡時等における共振外れにより、中間電位VSが急変した場合にも、ハイサイドドライブ信号SDHとローサイドドライブ信号SDLに応じて、所定の動作をすることが可能なドライブ制御回路を提供する。

【解決手段】ドライブ制御回路101は、ハイサイドスイッチ素子Q1とローサイドスイッチ素子Q2との間の中間端子Xに接続された共振回路の状態を検出することにより得られた状態検出信号Desに応じて、第1のMOSトランジスタM1の他端と第2の電位線9との間の抵抗値を下げる抵抗制御回路2を備える。

(もっと読む)

ドライブ信号生成回路、制御装置、スイッチング電源装置、および、制御方法

【課題】発振信号にノイズが発生してデッドタイムパルスが短くなる場合でも、ハイサイドドライブ信号およびローサイドドライブ信号を切り替えて出力することが可能なドライブ信号生成回路を提供する。

【解決手段】ドライブ信号生成回路1は、第1のパルス信号を出力するデッドタイムパルス生成回路1aと、第2のパルス信号Aを出力するデッドタイム調整回路1bと、第3のパルス信号Bを出力する補償パルス生成回路1cと、第2のパルス信号Aと第3のパルス信号Bとの論理和を演算し、この演算結果に応じた第4のパルス信号Zを出力するOR回路1dと、第4のパルス信号Zに応じて、ハイサイドドライブ信号SHおよびローサイドドライブ信号SLを出力する論理回路1eと、を備える。

(もっと読む)

バッファ回路

【課題】TFT特性のばらつきにかかわらず画像ムラがなく、高精細・高解像度の良好な画像を得ることができる半導体表示装置の駆動回路および半導体表示装置を提供する。

【解決手段】半導体表示装置はソース信号線側駆動回路と、ゲイト信号線側駆動回路とを有し、駆動回路はシフトレジスタ回路からのタイミング信号をバッファする複数のインバータ回路を有するバッファ回路を有し、インバータ回路は複数のインバータ回路を並列に接続して構成される。

(もっと読む)

切替回路及び受信回路

【課題】2つのクロック信号を切り替えて出力する切替回路において、出力信号のデューティ比を、入力されるクロック信号のデューティ比に保つこと。

【解決手段】切替回路100は、制御信号CONTに応じて、入力信号IN1,IN2を切り替えて出力信号OUTとして出力する。具体的には、制御信号CONTが「Lレベル」のときには、クロックドインバーターX2が動作し、信号IN1が信号OUTとして出力され、制御信号CONTが「Hレベル」のときには、クロックドインバーターX4が動作し、信号IN2が信号OUTとして出力される。

(もっと読む)

電流制御用半導体素子、およびそれを用いた制御装置

【課題】センス比の温度分布依存性を除去し、センスMOSFETによる電流検出の精度を向上できる電流制御用半導体素子、およびそれを用いた制御装置を提供することにある。

【解決手段】電流制御用半導体素子1は、同一半導体チップ上に、電流を駆動するメインMOSFET7と、メインMOSFET7に並列に接続し、メインMOSFETの電流を分流して電流検出を行うためのセンスMOSFET8とを有する。メインMOSFETは、複数のチャネルを有し、一列に配列されたマルチフィンガーMOSFETを使用して形成される。マルチフィンガーMOSFET7の中心から、最も遠いチャネルまでの距離をLとすると、マルチフィンガーMOSFETの中心から(L/(√3))の位置に最も近いチャネルを、センスMOSFET8のチャネルとして使用する。

(もっと読む)

ゲート駆動回路

【課題】トランジスタの遮断遅延を抑制し、絶縁ゲート型トランジスタ(IGBT)の保護動作を向上できるゲート駆動回路を提供する。

【解決手段】絶縁ゲート型トランジスタ31のゲートに、相補型の対のトランジスタ41A,41Bを接続し、対のトランジスタ41A,41Bのベースライン42の電流制御により絶縁ゲート型トランジスタ31を駆動するゲート駆動回路25において、トランジスタ41A,41Bのベースライン42に、ターンオン時にベースライン電流で充電されるコンデンサCsと、ターンオフ時にコンデンサCsに充電された電荷を消費すると共に、絶縁ゲート型トランジスタ31のゲート電位上昇によりトランジスタ41Aのベースに供給された電荷を消費する抵抗Rb2とを並列接続した電荷消費回路43Aを設けた。

(もっと読む)

負荷容量の駆動回路

【課題】2相クロックによる負荷容量の駆動において、負荷容量間の電荷の再利用を行うと共に、出力クロックの高速化を容易にする。

【解決手段】第1クロック信号とその逆位相の第2クロック信号とに対してそれぞれ遅延した第1及び第2遅延クロック信号が生成される。インバータ回路は第1クロック信号と第1遅延クロック信号とが逆位相である逆転期間において第1クロック信号と逆位相の第1電位を第1出力ノードに生成し且つ第2クロック信号と逆位相の第2電位を第2出力ノードに生成し、第1クロック信号と第1遅延クロック信号とが同位相である一致期間において第1出力ノードと第2出力ノードとをハイインピーダンスとする。スイッチ回路は、逆転期間において第1出力ノードと第2出力ノードとを接続するオン状態とする。第1出力ノードと第2出力ノードとは、駆動対象回路の負荷容量に接続される。

(もっと読む)

スイッチング素子駆動回路

【課題】電力伝送効率が良く、より小型化できるスイッチング素子駆動回路を提供する。

【解決手段】スイッチング素子102のゲート信号を発生させる制御演算装置101と、スイッチング素子と制御演算装置との絶縁を確保するトランス110と、第1の周波数とより速い第2の周波数の信号を発生する発振装置105,107と、ゲート信号の立ち上がり及び立ち下りの瞬間に一定時間だけ第1の周波数から第2の周波数に変化させた交流信号を出力する交流周波数変更手段111と、第1の周波数を第1のゲインにて変圧し、第2の周波数をより大きな第2のゲインで変圧して出力する共振回路110,109と、交流信号の振幅変化に従ってゲート信号の立ち上がり及び立ち下がりを復調して復調ゲート信号を出力する復調回路132,133,134と、復調ゲート信号によりスイッチング素子のゲートをオン/オフ駆動するゲートドライブ回路142,143を備えている。

(もっと読む)

駆動装置

【課題】駆動回路やトランジスタにおいてばらつきがあっても、PWM駆動信号の駆動デューティ成分が小さい場合にも、上側トランジスタと下側トランジスタのシュート・スルー(貫通状態)を防止する。

【解決手段】入力端子の第2レベルまたは第1レベル信号に応じてスイッチングデバイスの制御端子に駆動電流をシンク出力するシンク回路と、スイッチングデバイスのオフ期間中に制御端子を経て容量性の電流をシンクする電流シンクトランジスタと、入力端子の信号に応じてソース回路の入力駆動信号と、シンク回路あるいは前記シンクトランジスタへの入力駆動信号とを生成するI/F回路と、シンク回路または前記シンクトランジスタへの入力駆動信号をシンク回路かあるいはシンクトランジスタのどちらに入力駆動信号として出力するかを選択するセレクタと、この選択動作を制御するセレクタへの選択信号を受ける入力端子とを備える。

(もっと読む)

電子回路、パワーオンリセット回路、集積回路装置及び電子機器

【課題】電源投入時に初期状態を確実に設定できる電子回路、パワーオンリセット回路、集積回路装置及び電子機器等を提供すること。

【解決手段】電子回路は、各回路素子がトランジスターで構成される複数の回路素子XA1〜XB2と、第1の高電位電源電圧VDDが供給され、VDDが所定の電圧レベルになるまでは、低電位電圧レベルに設定され、VDDが所定の電圧レベルを越えると、VDDに追従して電圧レベルが上昇する第2の高電位電源電圧VINTを出力する電源出力回路100とを含む。複数の回路素子のうち、初期状態においてその出力ノードが高電位電圧レベルになる回路素子である第1のグループの回路素子XA1、XA2には、VDDが供給され、初期状態においてその出力ノードが低電位電圧レベルになる回路素子である第2のグループの回路素子XB1、XB2には、VINTが供給される。

(もっと読む)

61 - 80 / 596

[ Back to top ]