Fターム[5J055DX56]の内容

Fターム[5J055DX56]の下位に属するFターム

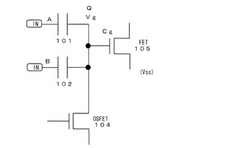

DEPP (5)

Fターム[5J055DX56]に分類される特許

21 - 40 / 596

半導体装置

【課題】半導体を用いた半導体装置として、論理回路がある。論理回路にはダイナミック論理回路とスタティック論理回路とがあり、トランジスタ等を用いて構成される。ダイナミック論理回路は情報を一定期間保持することができる。そのため、ダイナミック論理回路は、スタティック論理回路と比較して、トランジスタからのリーク電流が問題となる。

【解決手段】論理回路は、オフ電流が小さい第1のトランジスタと、ゲートが電気的に接続された第2のトランジスタと、を有し、第2のトランジスタのゲートのノードには第1のトランジスタを介して電荷が供給される。ノードに対して、第1及び第2の容量を介して電荷を供給する。電荷の状態に応じて、第2のトランジスタのオン、オフが制御される。第1のトランジスタは、チャネル形成領域に酸化物半導体を有する。

(もっと読む)

CMOSインバータを用いたマルチプレクサ、デマルチプレクサ、ルックアップテーブルおよび集積回路

【課題】CMOSインバータのP形MOSトランジスタのボディバイアスを変化させても、入力信号の立ち上がりと立ち下がりの伝搬遅延時間の差を、従来のものより小さく保てるマルチプレクサ、デマルチプレクサ、ルックアップテーブルおよび集積回路を提供する。

【解決手段】パスゲートM1、M2の出力に初段出力バッファとして低しきい値CMOSインバータINV1を接続したセレクター回路を基本構成とし、それを用いたマルチプレクサ、デマルチプレクサ、ルックアップテーブルおよび集積回路であって、パスゲートはそのボディ端子が可変電位をとるボディバイアス電源VBNに接続し、INV1のP形MOSトランジスタM3のしきい値電圧を可変にできるようにそのボディ端子は可変電位をとるボディバイアス電源VBPに接続し、そのN形MOSトランジスタM4はそのしきい値電圧を固定するためにそのボディ端子が固定電位をとる電源VSSに接続する。

(もっと読む)

電力変換装置

【課題】本発明の課題は、電力変換装置における温度検出素子の時間変化率を検出し、温度上昇の事前予測によりフェールセーフをかけることで、発熱半導体素子の発熱抑制とモジュールケースの冷却構造最適化を実現することである。

【解決手段】上記課題を解決するために、前記半導体素子のモジュールケースまたは素子自体の温度の時間変化率を検出する検出手段と、素子のゲート抵抗値を可変にする抵抗可変回路とを設け、前記検出温度の時間変化率が所定の設定値以上になったと判断されたときは、ゲート抵抗値を前記抵抗可変回路により低減することを特徴とする電力変換装置を提供する。

(もっと読む)

表示装置、表示モジュール及び電子機器

【課題】回路を構成するトランジスタ数を少なくし、且つレベルシフタを配置することな

くシフトレジスタとして正確に動作を行う半導体回路の提供することを課題とする。

【解決手段】第1端子が高電位電源に接続されたpチャネル型トランジスタと、第1端子

が低電位電源に接続されたnチャネル型トランジスタと、を含む回路群と、インバータ回

路と、をm段(mは任意の正の整数であり、m≧3)有し、第2n−1段目(nは任意の

整数であり、m≧2n≧2)の回路群の前記nチャネル型トランジスタのゲートにはクロ

ック信号が入力され、第2n段目(nは任意の整数であり、m≧2n≧2)の回路群の前

記nチャネル型トランジスタのゲートには反転クロック信号が入力される。

(もっと読む)

半導体装置

【課題】貫通電流を少なくできる半導体装置を提供する。

【解決手段】データを出力する出力部を各々備えた複数の半導体チップと、出力部の各々と接続された配線と、配線を介して複数の半導体チップの各々からデータを受け付ける受付部と、を含み、出力部が順番に駆動する半導体装置にて、出力部の各々は、オン状態時の抵抗値を変更可能であり、自己の駆動開始時から自己の次に駆動を開始する出力部の駆動開始時の前のタイミングまでの第1期間の間は、オン状態時の抵抗値を第1抵抗値にしてデータを配線に出力し、第1期間が経過した時点から自己の駆動終了時までの第2期間の間は、オン状態時の抵抗値を第1抵抗値よりも大きい第2抵抗値にしてデータを配線に出力する。

(もっと読む)

スイッチング回路

【課題】半導体スイッチの寄生容量の充放電時間を短縮する回路を提供する。

【解決手段】スイッチング回路10の入力端子21と出力端子22との間、入力端子21と共通端子23との間及び出力端子22と共通端子23との間の少なくとも一つに接続される容量抑制素子部50を備え、容量抑制素子部50は、容量抑制素子部が接続される半導体スイッチ素子20の端子間の寄生容量を、パルス状信号のクロック周波数のN倍(Nは1以上の整数)の周波数において、容量抑制素子部が接続されていない場合より低減する。

(もっと読む)

スイッチング回路

【課題】半導体スイッチの寄生容量の充放電時間を短縮し、オーバドライブによらず速度の向上と電力効率の向上を図り得るスイッチング回路を提供する。

【解決手段】半導体スイッチ素子20a、20dがON(OFF)のとき残りの半導体スイッチ素子がOFF(ON)となるように、各半導体スイッチ素子の入力端子にパルス状信号が印加される。スイッチング回路は、半導体スイッチ素子20bの出力端子と半導体スイッチ素子20dの入力端子の間に接続されるキャパシタンス素子60と、半導体スイッチ素子20bの入力端子と半導体スイッチ素子の出力端子20dの間に接続されるキャパシタンス素子61とを備える。キャパシタンス素子60,61は、半導体スイッチ素子20b、20dの各々の入力端子と出力端子間の寄生容量を、半導体スイッチ素子20b、20dに供給されるパルス状信号のクロック周波数のN倍の周波数において低減する容量を有する。

(もっと読む)

ゲートタイミング制御回路

【課題】半導体スイッチ,負荷電流,温度,主回路構成等によるサージ電圧の波形に応じて半導体スイッチの動作タイミングを調整することなく、各半導体スイッチの電圧分担を均等化させる。

【解決手段】直列接続された複数の半導体スイッチA,Bに出力されるゲート信号のタイミングを調整するゲートタイミング制御回路3において、コンパレータ4,4により、各半導体スイッチA,BのVce検出(A),(B)と、予め設定されたしきい値とを比較してVce検出における立ち上がりのタイミングを示すVce信号(A),(B)を出力する。そして、時間差制御部8において、ゲート信号に基づいて、前記各Vce信号(A),(B)の変化のタイミングが整合するように生成されたゲート出力(A),(B)をゲートドライバ2に出力する。

(もっと読む)

電圧レギュレータ

【課題】ノーマリオン型のトランジスタをオンオフ駆動できるようにする。

【解決手段】電圧レギュレータは,入力電圧に接続されたノーマリオン型の第1のトランジスタと,第1のトランジスタと出力端子との間に設けられたインダクタと,第1のトランジスタとインダクタとの接続ノードとグランド電圧との間に設けられた還流回路と,第1のトランジスタのゲートに駆動信号を供給する駆動回路と,グランド電圧に接続され,第1のトランジスタのオンオフ動作により接続ノードに生成されるパルス信号に基づいて負電圧を生成し,負電圧を駆動回路に供給する負電圧生成回路とを有する。

(もっと読む)

絶縁ゲート型スイッチング素子のゲートの電位を制御する半導体装置、及び、回路

【課題】 絶縁ゲート型スイッチング素子のゲートの電位を制御する半導体装置であって、低速スイッチング用と高速スイッチング用とで共通して使用可能な半導体装置を提供する。

【解決手段】 絶縁ゲート型スイッチング素子のゲートの電位を制御する信号を出力する半導体装置であって、第1信号出力端子を有しており、第1電位と第1電位よりも高い第2電位の間で変動する基準信号の入力を受けるか、または、内部で前記基準信号を生成することが可能であり、前記基準信号が第1電位にあるときには第3電位となり、前記基準信号が第2電位にあるときには第3電位よりも高い第4電位となる信号を第1信号出力端子に出力する第1動作と、前記基準信号が第1電位にあるときには第4電位となり、前記基準信号が第2電位にあるときには第3電位となる信号を第1信号出力端子に出力する第2動作とを切り換えて実行することができる。

(もっと読む)

スイッチングアンプ

【課題】 2つの出力素子の入力が共にハイレベルになり次に電源オン状態に移行する際に動作を開始することができないとい問題を解決する。

【解決手段】 電源制御手段16は、スイッチングアンプ10が電源オフ状態に移行する場合に、スイッチSWがオフ状態になり、コンデンサC102を強制的に放電させ、第2電源電圧V2に対する基準電位V3を強制的に低下させる。基準電位V3に対するロジック電源電圧Vddは、基準電位V3と同じだけ低下していくので、基準電位V3から見たロジック電源電圧Vddは固定される。定電流回路は、第2電源電圧V2に対する基準電位V3の低下に伴い、定電流Iを減少させ、第1の電流I1および第2の電流I2を減少させる。従って、基準電位V3から見たロジック電源電圧Vddが低下しないうちに、第1の電流I1、第2の電流I2を減少させ、パルス発生手段の動作を正常な状態で終了できる。

(もっと読む)

半導体集積回路

【課題】絶縁ゲート型半導体素子を駆動する半導体集積回路内において、貫通電流の発生を抑制することが可能な技術を提供することを目的とする。

【解決手段】半導体集積回路は、制御信号Vinを遅延させて得られる遅延信号を、PMOS1及びNMOS2のゲート端子に出力する遅延回路19を備える。NMOS4が、第2出力信号の変化に応じてオンからオフに切り替えられるタイミング(t2)は、PMOS1が、遅延信号の変化に応じてオフからオンに切り替えられるタイミング(t2)よりも遅くなく、かつ、PMOS3が、第1出力信号の変化に応じてオンからオフに切り替えられるタイミング(t7)は、NMOS2が、遅延信号の変化に応じてオフからオンに切り替えられるタイミング(t7)よりも遅くない。

(もっと読む)

スイッチング回路及び半導体モジュール

【課題】スイッチング制御する制御回路の負担を軽減するスイッチング回路を提供する。

【解決手段】第1のスイッチング素子の制御電極と第1のスイッチング素子をスイッチング制御する制御回路との間に接続される抵抗と、第1のスイッチング素子の制御電極と第1のスイッチング素子の低電位側電極との間に接続される第1のコンデンサと、第1のコンデンサと直列に接続される第2のスイッチング素子とを備え、第2のスイッチング素子の高電位側電極は、第1のスイッチング素子の制御電極に電気的に接続され、第2のスイッチング素子の低電位側電極は第1のスイッチング素子の低電位側電力端子に電気的に接続され、第2のスイッチング素子の制御電極は、抵抗と制御回路の間に接続されている。

(もっと読む)

半導体装置

【課題】充電対象素子へ充電電流を効率的に供給することが可能な半導体装置を提供する。

【解決手段】充電対象素子Cに充電電流を供給する半導体装置1は、第1導電型の半導体層1と、充電対象素子Cの第1電極に結合される第1ノードN1を有し、半導体層1の主表面上に形成される第2導電型の第1の半導体領域2と、電源電圧が供給される電源電位ノードNL1に結合される第2ノードN3および第3ノードN4を有し、第1の半導体領域2の表面において半導体層1と間隔をあけて形成される第1導電型の第2の半導体領域3と、第2ノードN3および第3ノードN4から半導体層1への電荷キャリアの移動を制限する電荷キャリア移動制限部とを備える。

(もっと読む)

高周波スイッチモジュール

【課題】スイッチポート切替時間が短く、かつ低消費電力、低面積を同時に満たす高周波スイッチモジュールを提供する。

【解決手段】デコーダ3は、前記スイッチポートを切替える制御信号CNTに応答し、スイッチ7を制御するためのスイッチ制御信号SWCNTを生成して、スイッチ切替タイミング検出器は、スイッチ制御信号SWCNTに応答し、スイッチ切替え検出信号t_swを生成し、周波数制御信号生成器は、スイッチ切替え検出信号t_swに応答し、周波数制御信号ICONT、CCONTを生成し、負電圧発生回路は、周波数制御信号ICONT、CCONTに応答し、前記負電圧発生回路内で生成したクロック信号の周波数を2つ以上のそれぞれ異なる周波数に切替つつ、負電圧出力信号NVG_OUTを生成し、スイッチ7は、スイッチ制御信号SWCNTと前記負電圧出力信号NVG_OUTに応答し、複数の高周波信号ポート間の経路を切替える。

(もっと読む)

パルス生成回路、パルス生成方法、走査回路、表示装置、及び、電子機器

【課題】自身の回路動作によって所望の遷移速度のパルス信号を生成可能なパルス生成回路、その生成方法、パルス生成回路を用いる走査回路、当該走査回路を用いる表示装置、及び、当該表示装置を有する電子機器を提供する。

【解決手段】2つの電源の間に直列に接続され、入力パルスの論理に応じて相補的にオン/オフ動作を行う2つのスイッチ素子を有し、パルス消滅時に所望の遷移速度のパルス信号を生成するパルス生成回路において、2つの電源のうち、入力パルスと同じ極性側の一方の電源を固定の電源電圧とし、他方の電源を複数の電源電圧間で切り換え可能とする。

(もっと読む)

出力バッファー回路

【課題】出力バッファーの面積・体積・部品点数の増加を抑制するとともに、ドライブ能力を向上させることが可能な出力バッファー回路を提供する。

【解決手段】第一駆動信号LINを伝達する第一入力経路4a、第二駆動信号RINを伝達する第二入力経路4b、第一入力経路4aと対応する第一出力バッファー6a及び第二入力経路4bと対応する第二出力バッファー6bを備える出力バッファー回路1において、入力経路切り替え手段8が、ステレオモード及びモノラルモードのうち、モノラルモードでは、第一入力経路4aと第一出力バッファー6a及び第二出力バッファー6bとを電気的に接続させ、出力経路切り替え手段10が、第一出力バッファー6a及び第二出力バッファー6bと、第一入力経路4a及び第一出力バッファー6aと対応する第一負荷2aとを、電気的に接続させる。

(もっと読む)

出力回路および出力制御システム

【課題】回路面積の縮小を図りつつ、待機電流をカットオフすることが可能な出力回路を提供する。

【解決手段】出力回路は、第1の電源にソースが接続された出力pMOSトランジスタを備える。出力回路は、第1の出力pMOSトランジスタのドレインと接地との間に接続された出力nMOSトランジスタを備える。出力回路は、出力pMOSトランジスタのドレインと前記出力nMOSトランジスタのドレインとの間に接続された出力端子を備える。出力回路は、前記出力pMOSトランジスタのオン/オフを制御するための第1のゲート制御信号を第1のゲート制御端子から出力する第1のレベルシフタ回路を備える。出力回路は、前記出力nMOSトランジスタのオン/オフを制御するための第2のゲート制御信号を第2のゲート制御端子から出力する第2のレベルシフタ回路と、を備える。

(もっと読む)

ゲート駆動回路、およびパワー半導体モジュール

【課題】 スイッチング素子を誤動作させずに高速低損失動作が可能なゲート駆動回路を部品点数の少ない簡易な回路構成で実現する。

【解決手段】 トランス15の1次側をローサイドゲート駆動回路2の出力端子に接続し、トランス15の2次側をハイサイドスイッチング素子5のゲート入力側に接続する。ローサイド駆動回路2から正極性のゲート駆動電圧が出力されるとハイサイドスイッチング素子5のゲート‐ソース間には負極性の電圧が印加されてゲート電圧は閾値以下に抑えられるため、ローサイドスイッチング素子がターンオンする際にハイサイドスイッチング素子はオフ状態を維持する。

(もっと読む)

半導体装置

【課題】入力信号が有する2値の電位に関わらず、正常に動作させることが可能なデジタ

ル回路の提案を課題とする。

【解決手段】半導体装置の一態様は、入力端子、容量素子、スイッチ、トランジスタ、配

線、及び出力端子を有し、前記入力端子は、前記容量素子の第1の電極に電気的に接続さ

れ、前記配線は、前記スイッチを介して前記容量素子の第2の電極に電気的に接続され、

前記トランジスタのゲートは、前記容量素子の第2の電極に電気的に接続され、前記トラ

ンジスタのソース又はドレインの一方は、前記配線に電気的に接続され、前記トランジス

タのソース又はドレインの他方は、前記配線に電気的に接続されていることを特徴とする

。

(もっと読む)

21 - 40 / 596

[ Back to top ]