Fターム[5J055DX56]の内容

Fターム[5J055DX56]の下位に属するFターム

DEPP (5)

Fターム[5J055DX56]に分類される特許

41 - 60 / 596

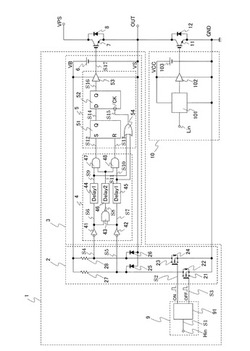

半導体回路

【課題】 高電位側スイッチング素子の導通を示す第1状態から前記高電位側スイッチングデバイスの非導通を示す第2状態への遷移、または前記第2状態から前記第1状態への遷移に伴い発生する過渡的な電圧ノイズに曝された場合に発生する誤信号を確実に除去する半導体回路を提供する。

【解決手段】 高電位側スイッチング素子駆動回路1は、スイッチング素子7の導通状態を変化させる場合に第1、第2のレベルシフト素子21、24のオン/オフ状態を必ず同一状態にするためのフリップフロップ52と、マスク信号S11が確実にセット信号S9、リセット信号S10を覆うようにするための第1、2、3の遅延回路44、45、46を有する。

(もっと読む)

出力バッファ回路

【課題】 誘導性負荷を駆動する出力バッファ回路の電力損失を低減する。

【解決手段】 誘導性負荷2から出力バッファ回路100に電流が流入している場合、スルーレート制御部140は、出力バッファ回路100の出力信号VOUTの立ち上がり過程において低いスルーレートから高いスルーレートへ変化させる制御を行うとともに、出力信号VOUTの立ち下がり過程において高いスルーレートから低いスルーレートに変化させる制御を行う。また、出力バッファ回路100から誘導性負荷2に電流が流出している場合に、スルーレート制御部140は、出力信号VOUTの立ち上がり過程において高いスルーレートから低いスルーレートに変化させる制御を行うとともに、出力信号VOUTの立ち下がり過程において低いスルーレートから高いスルーレートに変化させる制御を行う。

(もっと読む)

負荷駆動装置

【課題】スイッチ素子のオンオフ制御によって負荷を駆動する負荷駆動装置に関し、特に高いデューティ比のときに出力制御を高速に行い得る構成を実現する。

【解決手段】負荷駆動回路1には、外部からの駆動信号及び非駆動信号に応じて通電路10を流れる電流を制御するゲートドライバ6が設けられ、外部入力が非駆動信号から駆動信号に変化した直後には、コンデンサCBSからの放電に基づき、スイッチ素子M1がオン状態となるように通電路10を所定の大電流状態とし、その後の所定時期に、通電路10を流れる電流をスイッチ素子M1のオン状態が継続可能な所定の低レベルに変化させている。更に、駆動信号のデューティ比が所定値以上の場合には、ゲートドライバ6に駆動信号が入力されている間、チャージポンプ回路4によってコンデンサCBSに対する電流供給状態が維持されるようになっている。

(もっと読む)

スイッチング回路

【課題】電力効率を低下させずに高速動作可能なスイッチング回路を提供する。

【解決手段】スイッチング回路は、入力電圧を第1の電圧に変換する第1のDC/DCコンバータB1と、制御信号に応じて第1の電圧を出力するか否か切り替える第1のスイッチ回路C1と、第1のスイッチ回路からの電圧の過渡特性を制御する第1の制御回路D1と、高圧側電源に一端が、出力端子に他端が接続され、第1の制御回路からの電圧に応じてオンオフされる第1の能動素子A1と、入力電圧を第2の電圧に変換する第2のDC/DCコンバータB2と、制御信号に応じて第1のスイッチ回路とは相補的に第2の電圧を出力するか否か切り替える第3のスイッチ回路C3と、第3のスイッチ回路からの電圧の過渡特性を制御する第2の制御回路D2と、出力端子に一端が、低圧側電源に他端が接続され、第2の制御回路からの電圧に応じてオンオフされる第2の能動素子A2とを備える。

(もっと読む)

半導体回路、半導体装置、及び電池監視システム

【課題】過大電流による素子の破壊を防止することができる、半導体回路、半導体装置、及び電池監視システムを提供する。

【解決手段】短絡保護回路30のPMOSトランジスタMP3により短絡状態の場合は、電源電圧VDDからFETゲート電圧出力端子FET_PAD(外部FET0)に電流が流れる経路をPMOSトランジスタMP0及び短絡電流検出用抵抗素子R0を経由する経路から、PMOSトランジスタMP1及び抵抗素子Rpuを経由する抵抗値が大きい経路に切り替えるため、短絡電流を制限することができ、従って、短絡により、電池監視IC14が破壊されるのを防止することができる。

(もっと読む)

電圧識別装置及び時計制御装置

【課題】回路規模及び消費電流の増大を抑制しながら識別対象電圧の大きさを精度良く識別することができる電圧識別装置及び時計用制御装置を提供する。

【解決手段】基準電圧生成回路12と、被印加線18並びに電圧線VSH及び接地線GNDが導通可能となるように電圧線VSHと接地線GNDとの間に挿入されると共に、被印加線18に印加された識別対象電圧の大きさに応じてスイッチングを行うスイッチング回路20を備え、被印加線18に印加された識別対象電圧の大きさと閾値とを比較することにより識別対象電圧の大きさを識別する識別回路14と、識別回路14に対して識別対象電圧の大きさを識別させる間、電圧線VSHと接地線GNDとの間に流れる電流の大きさが所定の大きさに保たれるようにスイッチング回路20と接地線GNDとの間の抵抗22を制御可能とする制御部16と、を含む。

(もっと読む)

過電流保護装置

【課題】IGBT素子の短絡耐量を向上させ得る過電流保護装置を提供する。

【解決手段】過電流保護装置20では、各IGBT11a〜11fにゲート電圧Vgを印可するゲート駆動回路15に対してオフ信号を出力することで当該ゲート電圧Vgの印可を停止可能な保護回路22と、直流電源Eの電源電圧を制御可能な電源電圧制限回路23と、電源電圧を平滑化する平滑コンデンサCに蓄積された電荷を放電可能な放電回路24と、が設けられている。そして、電流検出部21により過電流が検出されると、保護回路22によりゲート電圧Vgの印可が停止され、電源電圧制限回路23により電源電圧が低減され、放電回路24により平滑コンデンサCに蓄積された電荷が放電される。

(もっと読む)

ドライバ回路

【課題】単電源駆動で、歪が小さく、大振幅の信号出力電圧が得られるドライバ回路を提供する。

【解決手段】1は入力端子、2、3は出力端子、4は第1の反転型オペアンプ、5は第2の反転型オペアンプ、6は非反転型オペアンプ、7はトランス、8は正電源電圧VCC、9はアナロググランドAGND(VCC/2)、10はグランドGND(0V)を示す。第1の反転型のドライバ用オペアンプの出力を第2の反転型のドライバ用オペアンプと非反転型のドライバ用オペアンプで受け、それらの出力を差動構成とすることで、低電圧での単電源駆動でも大振幅で、歪の小さい出力信号電圧が得られる構成とした。

(もっと読む)

出力回路

【課題】回路規模が小さく、出力トランジスタのしきい値電圧がばらついてもノイズを抑えつつターンオフ時間を短縮する。

【解決手段】駆動信号SdがLの時、トランジスタT1がオン、T2がオフしてVGS(T3)がほぼ電源電圧Vccに等しくなりトランジスタT3がオンする。駆動信号SdがHになるとトランジスタT1がオフ、T2がオンする。トランジスタT4がオンするので抵抗R2がバイパスされ、トランジスタT3のゲート電荷はトランジスタT4、T2を通して急速に放電する。VGS(T3)がVth(T4)+VDS(T2)よりも低下すると、トランジスタT4はオフとなり、以後はトランジスタT3のゲート電荷が抵抗R2とトランジスタT2を通して緩やかに放電する。トランジスタT3、T4のしきい値電圧は一致する傾向があるので、VGS(T3)がVTH(T3)に低下した時点でトランジスタT4をオフできる。

(もっと読む)

クロックバッファ回路及びクロック分配回路

【課題】クロック源の消費電力を増大させることなく、動作クロック周波数に応じて駆動能力を変化させることにより消費電力低減可能なクロックバッファ回路を提供すること。

【解決手段】クロック信号を伝達するバッファ部102と、クロック信号の参照クロック信号に対する逓倍数をカウントし、バッファ部102に対して逓倍数に基づいたイネーブル信号を出力する駆動能力切替部101と、を備え、バッファ部102は、当該バッファ部102の入力に接続された入力インバータ7と、イネーブル信号によりオンオフが可能であって、それぞれの出力が当該バッファ部の出力に共通に接続された複数の出力インバータ13〜28と、を備え、入力インバータ7が1個のCMOSインバータからなるクロックバッファ回路。

(もっと読む)

内燃機関制御装置

【課題】電磁負荷を駆動する内燃機関制御装置において、電磁負荷の駆動周期が短い場合でも、該電磁負荷の故障診断精度を向上させ、ノイズに影響されない高速制御を安定して行う。

【解決手段】電磁負荷制御装置において、前記電圧異常を検出する手段をマスクするためのマスク手段を備え、前記マスク手段は、前記電圧異常の検出タイミングを、電磁負荷遮断と電磁負荷の通電とが繰り返される電磁負荷の通電開始タイミングに合わせて設定してあり、電磁負荷の通電遮断時より一定時間を内部タイマによってカウントすることにより、前記一定時間内に検出された電圧異常の誤検出をマスクするように構成する。

(もっと読む)

負荷駆動装置

【課題】パワー素子にクランプ回路を接続してパワー素子の駆動端子に印加される電圧を所定電圧にクランプするに際し、スイッチング素子を駆動するための定電流の消費電流を削減できる負荷駆動装置を提供する。

【解決手段】クランプ回路50は駆動端子41に接続されており、ドライバ回路30が駆動端子41に定電流を流すことにより駆動端子41に印加される電圧が所定電圧に達すると、駆動端子41に印加される電圧を所定電圧にクランプする。また、ドライバ回路30は、パワー素子40の駆動端子41に定電流を流すことでパワー素子40をオン駆動する。さらに、ドライバ回路30は、駆動端子41に印加される電圧が所定電圧に達した後、駆動端子41に流す定電流の電流量を、駆動端子41に印加される電圧が所定電圧に達するまでに駆動端子41に流す定電流の電流量よりも低減する可変定電流回路32を備えている。

(もっと読む)

集積回路装置、電子機器及び集積回路装置の製造方法

【課題】 出力端子から出力される電圧値に応じて複数種の中から選択される耐圧に設定される集積回路装置等の提供すること。

【解決手段】 第1の耐圧を有する第1の出力トランジスター構造Tr_M1,Tr_M2と、第1の耐圧よりも高い第2の耐圧を有する第2の出力トランジスター構造Tr_H1,Tr_H2とが形成された半導体基板に、マスクを変えて配線して所定の耐圧に設定される集積回路装置である。配線により第1の耐圧が選択されると、第1,第2の出力トランジスター構造の双方が出力端子OUTと接続され、第2の出力トランジスター構造は、ダイオード接続されて静電気保護素子D1,D2を形成する。配線により第2の耐圧が選択されると、第1の出力トランジスター構造は出力端子OUTに非接続とされ、第2の出力トランジスター構造が出力端子OUTと接続される第2耐圧出力段トランジスターを形成する。

(もっと読む)

リセット回路およびシステム

【課題】 パワーオンまたはパワーダウンを検出するリセット回路を誤動作することなく動作させ、パワーオン時にリセット信号を正常に出力する。

【解決手段】 電源検出回路は、電源電圧が第1電圧を超えたときにパワーオン状態を示すパワーオン信号を活性化するとともに、初期化信号の活性化中に初期化される。スタータ回路は、電源電圧線と接地線の間に直列に配置された抵抗素子、遮断スイッチおよびキャパシタを有し、抵抗素子と遮断スイッチとを接続する第1接続ノードから初期化信号を出力する。遮断スイッチは、パワーオン信号の活性化中にオフする。このため、パワーオン状態中に、抵抗素子を介してキャパシタが充電されることを防止できる。この結果、キャパシタのTDDBの劣化を確実に防止でき、リセット回路を搭載する半導体装置およびシステムの誤動作を防止できる。

(もっと読む)

半導体装置及び電子機器

【課題】トランジスタを用いたスイッチ回路を有するデジタル回路において、電源電圧、入力信号の振幅、トランジスタのしきい値電圧の関係に応じて適切に入力信号を補正し、好適な回路動作を可能とする。

【解決手段】電源電位(VDD、VSS)が供給される第1のトランジスタ(32、33)を有するスイッチ回路(31)と、入力信号が印加される入力端(IN)と第1のトランジスタの制御端子(ゲート)との間に接続された補正回路(34、36)とを有し、前記制御端子と入力端との間に接続された容量(C2、C3)と、該容量と前記制御端子との間のノード(N5、N6)と電源電位との間に設けられた、第1のトランジスタと概ね同じしきい値を有するダイオード接続された第2のトランジスタ(35、37)と、第2のトランジスタに直列に接続されたスイッチ(SW2、SW3)とを有するデジタル回路(30)を提供する。

(もっと読む)

半導体装置

【課題】マルチプレクサとクロック分割回路との間における相互の電源ノイズの影響を低減する。

【解決手段】外部クロック信号CKに基づいて内部クロック信号LCLK1を生成するDLL回路100と、内部クロック信号LCLK1に基づいて、互いに位相の異なる内部クロック信号LCLK2,LCLK2Bを生成するクロック分割回路200と、内部データ信号CD,CEに基づいて、クロック信号LCLK2,LCLK2Bにそれぞれ同期した内部データ信号DQP,DQNを出力するマルチプレクサ300とを備える。クロック分割回路200に供給される内部電源電圧VPERI2とマルチプレクサ300に供給される内部電源電圧VPERI3は、互いに異なる電源回路82,83によって生成され、且つ、該半導体装置内で分離されている。これにより、相互にノイズの影響を及ぼし合うことがなくなる。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】出力期間の切替時における出力信号の遅延発生を抑制する出力回路、データドライバと表示装置の提供。

【解決手段】出力回路は差動増幅回路110、105,出力増幅回路120と第1の制御回路160、入力端子101、出力端子104、第1乃至第3の電源端子VDD、VSS、VMLを備える。差動増幅回路は前記入力端子の入力信号と前記出力端子の出力信号を入力する差動入力段110と第1及び第2のカレントミラー130、140を備える。出力増幅回路120は第1の電源端子VDDと出力端子104との間に接続された第1導電型の第1のトランジスタ121と出力端子104と第3の電源端子VMLとの間に接続された第2導電型の第2のトランジスタ122とを備える。第1の制御回路160は、第1導電型の第3のトランジスタ161と第1のスイッチ162を備える。

(もっと読む)

駆動回路

【課題】電源部品を減らし、安価な構成の駆動回路。

【解決手段】一次巻線Npと第1の二次巻線S1と第1の二次巻線の極性とは逆極性を持つ第2の二次巻線を有する2以上の二次巻線とを有し一次巻線に駆動信号が印加されるトランスDT1、第1の二次巻線からの信号によりオンオフ制御される第1スイッチング素子Qh、第2の二次巻線からの信号によりオンオフ制御される第2スイッチング素子Ql、第1の二次巻線の一端と第1スイッチング素子の制御端子との間に接続され第1スイッチング素子を駆動する第1駆動部Q11,Q12、第2の二次巻線の一端と第2スイッチング素子の制御端子との間に接続され第2スイッチング素子を駆動する第2駆動部Q21,Q22、第1の二次巻線電圧を倍電圧整流平滑して第1駆動部に供給する倍電圧整流平滑回路D11,D12,C11,C12、第2の二次巻線電圧を倍電圧整流平滑して第2駆動部に供給する倍電圧整流平滑回路D21,D22,C21,C22を有する。

(もっと読む)

電源回路

【課題】電源回路を備える装置の低消費電力化と、電源回路が発生させる出力電圧の安定化とを両立させる。

【解決手段】負荷へ供給するための出力電圧を入力電圧に基づいて発生させる一対のMOSトランジスタで構成された電圧発生部と、入力電圧および出力電圧の電圧値を検出する検出部と、検出された電圧値に応じて電圧発生部の駆動を制御する駆動部とを有する電源回路において、負荷の動作状態に応じて駆動部を制御することにより、一対のMOSトランジスタの不感帯の幅を変化させる制御部を有する。

(もっと読む)

モータ駆動装置

【課題】モータ駆動装置内で駆動信号経路のオープン故障が発生した場合にも、モータ駆動回路のトランジスタを安全、確実にオフ状態とする。

【解決手段】モータ駆動回路3のトランジスタQ1〜Q6に駆動信号を供給してトランジスタをオン・オフ制御するトランジスタ駆動回路5を備えたモータ駆動装置において、トランジスタQ1〜Q6のゲート・ソース間(またはベース・エミッタ間)に、トランジスタ駆動回路5からトランジスタQ1〜Q6への駆動信号経路上にオープン故障が発生した場合に、トランジスタQ1〜Q6をオフさせるための抵抗体Rgs及び/又はコンデンサCgsを接続すると共に、抵抗体、コンデンサをトランジスタの内部に配置したもの。

(もっと読む)

41 - 60 / 596

[ Back to top ]