Fターム[5J055DX56]の内容

Fターム[5J055DX56]の下位に属するFターム

DEPP (5)

Fターム[5J055DX56]に分類される特許

161 - 180 / 596

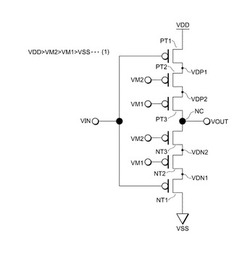

半導体集積回路、半導体集積回路の駆動方法、電子機器および電子機器の駆動方法

【課題】高耐圧化可能な半導体集積回路を提供する。

【解決手段】本発明に係る半導体集積回路は、第1電位ノード〔VDD〕と接続された第1ノード〔VOUT〕と、第1ノード〔VOUT〕と第1電位ノードより低電位である第2電位ノード〔VSS〕との間に直列に接続された第1のnチャネル型トランジスタ〔NT1〕および第2のnチャネル型トランジスタ〔NT2〕を有し、第1のnチャネル型トランジスタ〔NT1〕の一端は、第2電位ノード〔VSS〕に接続され、他端は、第2のnチャネル型トランジスタの一端に接続され、ゲート端子は、第2ノード〔VIN〕に接続され、第2のnチャネル型トランジスタ〔NT2〕の他端は、第1ノード〔VOUT〕に接続され、ゲート端子は、第1電位ノード〔VDD〕と第2電位ノード〔VSS〕との間に位置する第1中間電位〔VM1〕に接続されている。第2のnチャネル型トランジスタにより分圧され、各トランジスタに印加される電圧を低減できる。

(もっと読む)

ラッチ型コンパレータ及びこれを用いた多値論理復調回路

【課題】製造プロセスのマージンを削ることなく、オフセットの補正が可能なラッチ型コンパレータ、及びこれを用いた、オフセットの補正が可能な多値論理の復調回路を提供する

【解決手段】本発明によるラッチ型コンパレータは、クロスカップルされた2つのCMOSインバータからなるフリップフロップを含み、フリップフロップの4個のトランジスタの各々のソースと電源/接地間には伝達トランジスタを介して抵抗と設定電流可変の定電流源が接続され、フリップフロップの差動出力は各々伝達トランジスタを介して差動入力に接続され、全ての伝達トランジスタのゲートは、差動クロック入力のいずれかに接続されていることを特徴とする。

(もっと読む)

IGBTのサージ電圧抑制回路

【課題】電力変換装置のスイッチング素子として用いられるIGBTの、安全動作領域が欠けているような場合でも、サージ電圧の抑制ができるようにする。

【解決手段】IGBTモジュールIGBT1,2の主回路用エミッタ端子E1,E2と制御用ゲート端子との間に、複数のツェナーダイオードZD11,12,21,22を相互に逆直列接続し、この逆直列接続回路とコンデンサCg1,2との並列接続回路を挿入することで、コレクタ電流Icの変化率を緩和し、サージ電圧を抑制する。

(もっと読む)

容量性負荷の充放電回路

【課題】ブートストラップ型の容量性負荷充放電回路における動作を安定させること。

【解決手段】容量性負荷の充放電回路は、充放電部と、蓄電素子と、基準電位設定部と、電荷放出部とを有する。充放電部は、容量性負荷の電位がアナログ信号の電位変化パターンに倣って変化するように容量性負荷に対する充放電を行う。蓄電素子は、電源部からの電流によって充電されるとともに容量性負荷に対する充電時の電流源となる。基準電位設定部は、アナログ信号の電位が閾値よりも高い場合に、蓄電素子が有する低電位側端子の電位を、第1基準電位から第1基準電位よりも高い第2基準電位に設定する。電荷放出部は、容量性負荷から充放電部を通じて流れ出た電荷を、低電位側端子を介さずに放出する。

(もっと読む)

容量性負荷の充放電回路

【課題】容量性負荷の充放電回路における省電力効果を高めること。

【解決手段】容量性負荷の充放電回路は、充放電部と、蓄電素子と、電位調整部と、経路選択部とを有する。充放電部は、容量性負荷の電位がアナログ信号の電位変化パターンに倣って変化するように容量性負荷に対する充放電を行う。蓄電素子は、電源部からの電流によって充電されるとともに容量性負荷に対する充電時の電流源となる。電位調整部は、蓄電素子が有する低電位側端子の電位を、アナログ信号の電位よりも所定量低くするように調整する。経路選択部は、容量性負荷からの電荷を電源部と蓄電素子の少なくとも一方に流す回生経路と、容量性負荷からの電荷をグランド側に流す放電経路とを、アナログ信号の電位に応じて選択する。

(もっと読む)

レベルシフト回路

【課題】外的要因による誤動作を防止して確実な信号伝達を行うレベルシフト回路。

【解決手段】第1電圧レベルを第1電圧レベルとは異なる第2電圧レベルに変換するレベルシフト回路であって、第2電圧レベルの論理電圧状態をセットするセット信号を送信するセットレベル回路21と、第2電圧レベルの論理電圧状態をリセットするリセット信号を送信するリセットレベル回路22と、第2電圧レベルでセット信号及びリセット信号を検出するための基準値を設定する基準レベル回路C3とを有し、セットレベル回路とリセットレベル回路と基準レベル回路との各々は、それぞれコンデンサC1〜C3を介して第1電圧レベルから第2電圧レベルに信号を伝達する。

(もっと読む)

シュミットトリガ型インバータ

【課題】さらに入力ノイズ耐性を有するシュミットトリガ型インバータを提供すること。

【解決手段】入力側ノードへの供給電圧が増加して第1の基準電圧に達するに従い出力側ノードから出る電圧が比較高電圧レベルから比較低電圧レベルに遷移し、入力側ノードへの供給電圧が減少して第1の基準電圧より低い第2の基準電圧まで減少するに従い出力側ノードから出る電圧が比較低電圧レベルから比較高電圧レベルに遷移するインバータと、インバータの入力側ノードに一方端が接続された第1の抵抗素子と、インバータの入力側ノードに一方端が接続された、該一方端の電圧が上昇するほどに抵抗値が減じる可変抵抗素子と、可変抵抗素子の他方端に一方端が接続された第2の抵抗素子と、ドレインが第2の抵抗素子の他方端に接続され、ゲートがインバータの出力側ノードに接続され、ソースが接地電位に接続されたnチャネルMOSトランジスタとを具備する。

(もっと読む)

リセット信号生成回路及び半導体装置

【課題】ヒステリシス特性を持たないシンプルな回路構成で専有面積を抑え、かつノイズに強く、確実にパワーオンリセット信号を生成することの出来るリセット信号生成回路及びこれを備える半導体装置を提供することを課題とする。

【解決手段】第1のバッファ回路と、ローパスフィルタと、抵抗素子と、第2のバッファ回路と、を有し、第1のバッファ回路の出力端子は、ローパスフィルタの入力端子に電気的に接続され、ローパスフィルタの出力端子は、抵抗素子の一方の端子、及び第2のバッファ回路の入力端子に電気的に接続され、抵抗素子の他方の端子には一定の電位が供給されている。

(もっと読む)

二重絶縁ゲート型電界効果トランジスタを用いたゲート回路、SRAMセル回路、多入力CMOSゲート回路、CMOS−SRAMセル回路、集積回路

【課題】高速動作と消費電力の減少を両立させた二重絶縁ゲート型電界効果トランジスタを用いた回路を提供する。

【解決手段】第一の四端子二重絶縁ゲート電界効果トランジスタは、一方のゲートを入力端子、ソースを第一の電源に接続し、ドレインを出力端子、該ドレインを負荷素子を介して第四の電源に接続し、他方のゲートに第一の三端子絶縁ゲート電界効果トランジスタのドレインを接続し、前記第一の三端子絶縁ゲート電界効果トランジスタは、ソースを第二の電源に接続し、ゲートを第三の電源に接続し、前記三端子絶縁ゲート電界効果トランジスタのドレインとソースの間の抵抗と前記四端子二重絶縁ゲート電界効果トランジスタの一方のゲートと他方のゲートの間のゲート絶縁膜容量と前記両ゲートに挟まれた半導体の容量で微分回路を構成したゲート回路で、前記第一の四端子二重絶縁ゲート電界効果トランジスタの一方のゲートと他方のゲート間を容量で接続する。

(もっと読む)

ドライバ回路およびDC−DCコンバータ

【課題】デッドタイムを設けることなく貫通電流を抑制することができるとともに、貫通電流を抑制しつつ高周波化を図ることができるドライバ回路およびDC/DCコンバータを提供する。

【解決手段】電源端子と接地端子との間に直列形態に接続され、デッドタイムのない相補的な一対の制御信号によってオン、オフ駆動される第1のスイッチング素子(SW1)と第2のスイッチング素子(SW2)を備えるドライバ回路において、少なくとも前記第1のスイッチング素子の制御端子に、オン状態での制御電圧を制限するリミッタ回路(LMT1)を接続するようにした。

(もっと読む)

出力ドライバ回路

【課題】本発明の目的は、被駆動部の確実な駆動を維持しつつも、より高速に被駆動部を駆動することができる、出力信号を得ることができる、出力ドライバ回路を提供することにある。

【解決手段】本発明の一態様にかかる出力ドライバ回路は、入力信号が加えられる入力端子と、前記入力信号を受けてバッファ信号を出力する、第1電源から給電されて動作する、入力バッファと、前記バッファ信号を受けて出力信号を出力端子から出力する、第2電源から給電されて動作する、出力バッファと、前記出力バッファに、前記第2電源の電位が前記第1電源の電位と同等である第1状態時に、前記バッファ信号をそのまま前記出力バッファに加えさせる第1の動作と、前記第2電源の電位が前記第1電源の電位に比して高くなった第2状態時に、前記バッファ信号を前記第2電源の電位に対応するレベルまでレベルシフトしてレベルシフト済信号として前記出力バッファに加えさせる第2の動作とを、切り替えて行わせる、制御部と、を備える。

(もっと読む)

半導体集積回路及びLSIシステム

【課題】CMOS論理回路を小さいスイッチで高速動作させることができ、サブスレッショルドリーク電流を効果的に低減可能な半導体集積回路及びLSIシステムを提供すること。

【解決手段】半導体集積回路は、CMOS論理回路と、CMOS論理回路の電圧供給源とCMOS論理回路の電源端の間に設けられた、第1のMOSFETを有するスイッチ回路と、第1のMOSFETと逆チャネルの第2のMOSFETと、第2のMOSFETのドレインに接続された第1の抵抗と、第1の抵抗及び第1のMOSFETのソースに接続された第2の抵抗と、を有するデジタルアナログ変換回路とを備える。第1のMOSFETのバックゲートと、第1の抵抗と第2の抵抗の接続点が接続される。また、第1のMOSFETのゲートに供給される制御信号と第2のMOSFETのゲートに供給される制御信号が共通である。

(もっと読む)

DC−DCコンバータ及び電源供給システム

【課題】効率の低下を抑えつつ、輻射ノイズの低下をすることができるDC−DCコンバータ及びシステム電源を提供すること。

【解決手段】第1DC−DCコンバータ20aは、ワンセグ受信機、無線通信機に第4、第5電源電圧を供給する第4、第5DC−DCコンバータが動作する場合、第1DC−DCコンバータ20aは、スイッチング回路38を駆動するドライバ部37の駆動能力を小さくている。また、第1DC−DCコンバータ20aは、この駆動能力を3段階で大きくしている。これにより、第1DC−DCコンバータ20aのスイッチングの立ち上げ時間及び立ち下げ時間を長くする。

(もっと読む)

スイッチング制御回路

【課題】ハーフブリッジ回路を構成する2つのスイッチング素子を共にオンさせるような2つのパルス信号が入力された場合であっても、2つのスイッチング素子が同時にオンすることを確実に防止すること。

【解決手段】第1パルス信号と第2パルス信号に基づいて、第1出力端子(DRV1)4からP型MOSFET(MOS1)10に第1駆動信号が出力され、第1パルス信号と第2パルス信号に基づいて、第2出力端子(DRV2)5から第2スイッチング素子であるN型MOSFET(MOS2)11に第2駆動信号が出力されるように構成され、保護回路20によりP型MOSFET(MOS1)10及びN型MOSFET(MOS2)11のうちの少なくとも一方がオフされるようにした。

(もっと読む)

PLL回路

【課題】ノイズの抑圧を効果的に行うことができるPLL回路を提供する。

【解決手段】位相比較器10と、チャージポンプ回路20と、ループフィルタ30と、VCO40と、N分周器50とを備える。チャージポンプ回路20の一実施形態は、アップ信号UP1によりスイッチ22をオンした後、アップ信号UP1を遅延させたアップ信号UP2により再度スイッチ22をオンする。同様に、ダウン信号DN1によりスイッチ23をオンした後、ダウン信号DN1を遅延させたダウン信号DN2により再度スイッチ23をオンする。

(もっと読む)

半導体装置

【課題】入力信号が有する2値の電位に関わらず、正常に動作させることが可能なデジタル回路の提案を課題とする。

【解決手段】半導体装置の一態様は、入力端子、容量素子、スイッチ、トランジスタ、配線、及び出力端子を有し、前記入力端子は、前記容量素子の第1の電極に電気的に接続され、前記配線は、前記スイッチを介して前記容量素子の第2の電極に電気的に接続され、前記トランジスタのゲートは、前記容量素子の第2の電極に電気的に接続され、前記トランジスタのソース又はドレインの一方は、前記配線に電気的に接続され、前記トランジスタのソース又はドレインの他方は、前記配線に電気的に接続されていることを特徴とする。

(もっと読む)

液晶表示装置

【課題】トランジスタを用いたスイッチ回路を有するデジタル回路において、電源電圧、入力信号の振幅、トランジスタのしきい値電圧の関係に応じて適切に入力信号を補正し、好適な回路動作を可能とする。

【解決手段】電源電位(VDD、VSS)が供給される第1のトランジスタ(32、33)を有するスイッチ回路(31)と、入力信号が印加される入力端(IN)と第1のトランジスタの制御端子(ゲート)との間に接続された補正回路(34、36)とを有し、前記制御端子と入力端との間に接続された容量(C2、C3)と、該容量と前記制御端子との間のノード(N5、N6)と電源電位との間に設けられた、第1のトランジスタと概ね同じしきい値を有するダイオード接続された第2のトランジスタ(35、37)と、第2のトランジスタに直列に接続されたスイッチ(SW2、SW3)とを有するデジタル回路(30)を提供する。

(もっと読む)

電気的に画素化された発光素子

電気的に画素化された発光素子、電気的に画素化された発光素子を形成するための方法、電気的に画素化された発光素子を含むシステム、電気的に画素化された発光素子の使用方法。 (もっと読む)

ドライバ回路

【課題】高速なデータパターンの時のみ周波数特性を改善して、所望の振幅を得ることが可能な送信側ドライバ回路を提供する。

【解決手段】第1のプルアップ抵抗回路P41、第3のプルアップ抵抗回路P43、第1のプルダウン抵抗回路N41、第3のプルダウン抵抗回路N43の抵抗値を第1の制御信号(SDATAP、SDATAM、DEMPHPP、DEMPHMN、DEMPHPN、DEMPHMP)に応じて変化させ、第2のプルアップ抵抗回路P42、第4のプルアップ抵抗回路P44、第2のプルダウン抵抗回路N42、第4のプルダウン抵抗回路N44の抵抗値を第2の制御信号(EMPHPP、EMPHPMN、EMPHPN、EMPHMP)に応じて変化させる

(もっと読む)

デューティ可変回路

【課題】低電力、小面積で実現するデューティ可変回路を提供する。

【解決手段】それぞれ一対の相補型のトランジスタを有する第1のCMOSインバータ回路と、第2のCMOSインバータ回路と、前記第1のCMOSインバータ回路と第2のCMOSインバータ回路の間に直列接続され、ゲートがグランドに接続されたPMOSトランジスタと、前記第2のCMOSインバータ回路に接続された第3のインバータ回路と、前記第2のCMOSインバータ回路への電源及びグランドの供給がそれぞれ制御できる第1及び第2のスイッチを有する。前記第3のインバータ回路の出力信号を用いて前記第1、第2のスイッチの開閉を切り替えることによって、前記第2のCMOSインバータ回路の入力信号の論理が遷移する際の前記第2のCMOSインバータ回路の貫通電流を低減する。

(もっと読む)

161 - 180 / 596

[ Back to top ]