Fターム[5J055DX56]の内容

Fターム[5J055DX56]の下位に属するFターム

DEPP (5)

Fターム[5J055DX56]に分類される特許

201 - 220 / 596

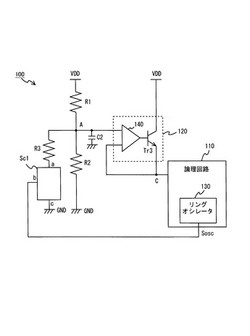

半導体集積回路装置

【課題】遅延を有する論理回路から検出した信号を直接利用して、その論理回路の電源電圧の制御を行うような機構が求められている。

【解決手段】本発明は、本発明は、論理回路と、前記論理回路の遅延の変化に応じた周波数の検出信号を出力する遅延特性検出回路と、前記検出信号に応じて抵抗値が変化する抵抗素子と、前記抵抗素子の抵抗値の変化に応じて参照電圧を出力する参照電圧生成回路と、前記参照電圧を前記論理回路及び遅延特性検出回路に出力する電圧供給回路とを有する半導体集積回路装置である。

(もっと読む)

半導体装置及びその動作モード設定方法

【課題】モードパッドの配置に関して、レイアウト的な制限がかかっていた。

【解決手段】本発明に係る半導体装置は、第1内部端子と、第2内部端子と、前記第2内部端子に接続され、第2内部端子が第1参照電位に電気的に接続される状態と接続されない状態とを切り替える第1スイッチ回路と、第2内部端子に接続され、第2内部端子が第2参照電位に電気的に接続される状態と接続されない状態とを切り替える第2スイッチ回路と、第1及び第2内部端子に接続され、第1内部端子の電位と第2内部端子の電位とを比較する比較器と、を備える半導体装置であって、第1及び第2スイッチ回路は、第1内部端子の電位に応じて排他的に動作することを特徴とする。

(もっと読む)

半導体集積回路

【課題】 出力回路の発生する電源ノイズを低減する電源ノイズキャンセル回路において、出力回路に接続される負荷に基づいてキャンセルタイミングを設定する。

【解決手段】 電源VDD0と接地GND0との間に接続されその入力端が入力端子にその出力端が出力端子に接続された出力回路と、入力端子と出力端子とに接続され、入力端子と出力端子との電位差に基づいて出力端子に電源VDD0から流れ込む電流又は出力端子から接地GND0に流れ出す電流をキャンセルする電流を発生させる電源ノイズキャンセル回路とを備える。

(もっと読む)

入力バッファ回路及びこれを用いた入力装置

【課題】高速低消費電力で閾値制御が可能な入力バッファ回路及び入力装置を提供する。

【解決手段】入力バッファ回路30は、バイアス電圧生成回路100で生成されたバイアス電圧PLV及びこれよりもレベルの高いバイアス電圧NLVにより動作する回路である。この回路30は、バイアス電圧PLVよりも低い第1の電圧が入力されると、オン状態になってその第1の電圧をノードN32から出力するNMOS32と、バイアス電圧NLVよりも高い第2の電圧が入力されると、オン状態になってその第2の電圧をノードN33へ出力するPMOS33と、ノードN32から出力される第1の電圧をラッチして第1の論理の電圧をノードN34へ出力するラッチ回路34と、ノードN33から出力される第2の電圧をラッチして第2の論理の電圧をノードN34へ出力するラッチ回路35とを有している。

(もっと読む)

駆動能力調節回路及びデータ出力回路

【課題】ヒューズのカッティング有無によってスペックで定められた駆動力以外の駆動力にデータドライバの駆動力を調節できるようにすることによって、使用者の要求に合わせてデータドライバの駆動力を容易に調節できるようにした駆動能力調節回路及びデータ出力回路を提供する。

【解決手段】ヒューズのカッティング有無によってヒューズ信号を生成するヒューズ信号生成部と、前記ヒューズ信号に応答して選択信号を生成する選択信号生成部と、設定信号を受信し、前記選択信号に応答して駆動制御信号を生成する駆動制御信号生成部と、前記駆動制御信号をデコーディングして駆動信号を生成する駆動信号生成部と、を含む駆動能力調節回路を構成する。

(もっと読む)

駆動回路、駆動方法、固体撮像装置および電子機器

【課題】電源電圧の低電圧側の電圧と高電圧側の電圧との間の中間電圧での駆動を、トランジスタのゲート酸化膜に高耐圧素子構造を適用することなく実現できるようにする。

【解決手段】第1,第2出力バッファ回路20,30Aを用いた駆動回路10において、当該駆動回路10を構成するトランジスタのゲート酸化膜にその耐圧ΔVlimを超える電圧を印加することなく、第1出力バッファ回路20の作用によって耐圧ΔVlimを超えた電圧振幅VL−VHで駆動する。これに加えて、第2出力バッファ回路30Aにおいて、出力端子35側のトランジスタMp32,Mn32を、バイアス電圧の定常印加でなく、耐圧範囲内の電圧(VL〜VD,VS〜VH)で駆動するとともに、ノードN31,N32側のトランジスタMp31,Mn31を、耐圧範囲内の電圧でなく、範囲外の電圧VL〜VHで駆動することで、中間電圧VMでの駆動を実現する。

(もっと読む)

電力変換装置

【課題】 電力変換用スイッチング素子を異常電流から保護する際、当該スイッチング素子の制御端子に印加する電圧制御信号のレベルを下げることなく、またバラつきも少ないスイッチング素子を保護する機能を有する電力変換装置を提供する。

【解決手段】 本発明の電力変換装置1は、一対の主端子と主端子対に流れる電流を制御する制御端子とをもち、主端子の低電位側端子が低電位側に接続される電力変換用スイッチング素子134〜139と、主端子対に流れる主電流を検出する電流検出回路4と、制御端子と低電位側との間に位置する主コンデンサ5と、電流検出回路4によって検出された主電流がスイッチング素子134〜139の所定値を超えた場合に、制御端子と低電位側との間に主コンデンサ5が電気的に接続されるようにスイッチング動作する保護用スイッチング素子6と、を有することを特徴とする。

(もっと読む)

電気回路、電気光学装置、電子機器、および電気回路の制御方法

【課題】入力信号に必要な振幅を低減する。

【解決手段】電源線L1と出力部N2との間のトランジスタTA1のゲートG1は容量素子C1を介して入力部N1に結合する。電源線L2と出力部N2との間のトランジスタTA2のゲートG2は容量素子C2を介して入力部N1に結合する。トランジスタTB3は、電源線L1からみてゲートG1の方向を順方向として電源線L1とゲートG1との間にダイオード接続される。トランジスタTB4は、ゲートG1からみて電源線L1の方向を順方向として電源線L1とゲートG1との間にダイオード接続される。トランジスタTB3の閾値電圧VT3がトランジスタTA1の閾値電圧VT1を上回り、かつ、トランジスタTB3の閾値電圧VT3とトランジスタTB4の閾値電圧VT4との加算が減少するように、トランジスタTB3およびトランジスタTB4の各々のバックゲートBの電位VBが設定される。

(もっと読む)

走査電極用容量性負荷駆動回路及びプラズマディスプレイパネル

【課題】回路規模及び制御配線の増大を回避し、走査線駆動の一斉動作時の雑音やそれに伴う電磁輻射妨害を低減する。

【解決手段】容量性負荷駆動回路は、複数の駆動信号を一斉に動作させる入力制御信号を遅延させる少なくとも1つの遅延素子と、入力制御信号を受けるものと、遅延信号を受けるものとからなる複数のタイミング回路と、複数のタイミング回路からの対応する出力信号を受け、駆動信号を出力する複数の高電圧出力回路とを備える。複数の高電圧出力回路は、入力される出力信号に応じて分類分けされており、分類毎に異なる複数の位相で変化する複数の駆動信号を出力する。

(もっと読む)

パワーデバイスドライブ装置

【課題】ソフトシャットダウン機能を有するパワーデバイスドライブ装置の出力端子とパワーデバイスを接続する信号線を短縮化する。

【解決手段】パワーデバイスドライブ装置50には、光結合部1とパワーデバイスドライブ回路部2が設けられる。パワーデバイスドライブ回路部2には、ドライバ部21、ディセイブル回路22、I/V変換回路23、サンプルホールド回路24、ソフトシャットダウン回路25、制御端子PDisb、Vcc端子PVcc、Vo端子PVo、及びVss端子PVssが設けられる。IGBT4の短絡等の異常事態が発生したとき、制御信号Ssetがディセイブル状態となる。ディセイブル状態の制御信号Ssetがディセイブル回路22に入力され、出力部から出力される信号がHz状態となり、ソフトシャットダウン回路25のNch MOSトランジスタNMT3が“ON”しIGBT4をソフトシャットダウン状態にする。

(もっと読む)

インバータ回路、シフトレジスタ回路、否定論理和回路、否定論理積回路

【課題】出力の最大振幅の幅が狭まることを軽減することができるインバータ回路を提供する。

【解決手段】第1トランジスタの一方のソース/ドレイン領域は第2トランジスタの一方のソース/ドレイン領域に、第2トランジスタの他方のソース/ドレイン領域は一方の電圧供給線に、ゲート電極は第3トランジスタの一方のソース/ドレイン領域に、第3トランジスタのゲート電極は他方のソース/ドレイン領域に、第3トランジスタの他方のソース/ドレイン領域は一方の電圧供給線に接続され、第2トランジスタのゲート電極と第3トランジスタの一方のソース/ドレイン領域とが接続されたノード部には第4トランジスタの一方のソース/ドレイン領域が、第1トランジスタ及び第4トランジスタの他方のソース/ドレイン領域は他方の電圧供給線に接続され、第1トランジスタのゲート電極及び第4トランジスタのゲート電極には入力信号が印加される。

(もっと読む)

PDP駆動回路及びPDP駆動用半導体集積回路

【課題】回路規模及び制御配線の増大を回避し、PDP駆動回路の一斉動作時の雑音やそれに伴うEMIを低減する。

【解決手段】PDP駆動用半導体集積回路は、入力信号を入力信号の振幅よりも大きい振幅を有する高電圧パルスに変換して出力するPDP駆動回路を複数備える。複数のPDP駆動回路の各々が、互いに異なるタイミングで動作して高電圧パルスを順次出力する順次動作機能と、複数のPDP駆動回路の各々が全て同じタイミングで動作して高電圧パルスを一斉に出力する一斉動作機能とを有する。順次動作時及び一斉動作時の双方において、高電圧パルスの電圧レベルがロウレベルからハイレベルに変化する速度及びロウレベルからハイレベルに変化する速度のうちの少なくとも1つを制御する。

(もっと読む)

ブートストラップ回路

【課題】飛び込みによる影響を軽減できるブートストラップ回路を提供する。

【解決手段】同一導電型の第1乃至第3トランジスタから構成され、第1トランジスタにおいて、一方のソース/ドレイン領域は第2トランジスタの一方のソース/ドレイン領域に接続され、他方のソース/ドレイン領域には2相のクロックの一方が印加され、ゲート電極は第3トランジスタの一方のソース/ドレイン領域に接続され、第2トランジスタにおいて、他方のソース/ドレイン領域は電圧供給線に接続され、第3トランジスタにおいて、他方のソース/ドレイン領域には入力信号が印加され、ゲート電極には2相のクロックの他方が印加され、第1トランジスタのゲート電極と第3トランジスタの一方のソース/ドレイン領域とはノード部を構成し、第2トランジスタのゲート電極には2相のクロックの他方が印加され、ノード部と電圧供給線との間に、容量部が接続されている。

(もっと読む)

インバータ回路、シフトレジスタ回路、否定論理和回路、否定論理積回路

【課題】同一導電型のトランジスタから成るインバータ回路を提供する。

【解決手段】インバータ回路は否定論理構成部と出力回路部とから構成されており、出力回路部は同一導電型の2つのトランジスタから構成されており、出力回路部を構成する2つのトランジスタを、第1出力トランジスタ、及び、第2出力トランジスタと表すとき、第1出力トランジスタの一方のソース/ドレイン領域と第2出力トランジスタの一方のソース/ドレイン領域とは接続されており、第2出力トランジスタのゲート電極は、否定論理構成部の出力側に接続されており、第1出力トランジスタの他方のソース/ドレイン領域には第1電圧が印加され、第2出力トランジスタの他方のソース/ドレイン領域には第2電圧が印加され、第1出力トランジスタのゲート電極、及び、否定論理構成部の入力側には、入力信号が印加される。

(もっと読む)

電源回路

【課題】アクティブモードとスタンバイモードとの切替えが実行されても、出力電圧の変動が小さい電源回路を提供する。

【解決手段】電源回路は、第1のノードM1と出力端子20との間に接続された第1のトランジスタN1と、電圧源10と第2のノードM2との間に接続された第2のトランジスタN2と、電圧源10と第1のノードM1との間に接続された第1のスイッチング素子P1と、第2のノードM2と出力端子との間に接続され、ゲートが第1のスイッチング素子P1のゲートに接続された第2のスイッチング素子P2と、第1および第2のトランジスタN1、N2のそれぞれのゲートに一定電圧を印加するレギュレータAとを備え、スタンバイ状態の場合に第1および第2のスイッチング素子は導通し、アクティブ状態の場合に第1および第2のスイッチング素子は非導通となる。

(もっと読む)

アクティブゲート回路

【課題】自己のアームの半導体スイッチング素子のターンオン時のコレクタ・エミッタ過電圧の抑制のみならず、他方のアームの半導体スイッチング素子の還流ダイオードのリカバリ電圧の過電圧の抑制も可能とすることである。

【解決手段】アクティブゲート回路12aのリカバリ過電圧抑制手段16aは、電力変換器のレグを形成する一対のアームのうちの一方のアームの半導体スイッチング素子S1のターンオン時に他方のアームの還流ダイオードD2のリカバリ電圧の過電圧を抑制するように一方のアームの半導体スイッチング素子S1のゲート電流を調整する。

(もっと読む)

電気回路、電気光学装置、電子機器、および電気回路の駆動方法

【課題】ヒステリシス特性を示すインバータ回路の構成を簡素化しながら消費電力を低減する。

【解決手段】インバータ回路Q1は、Pチャネル型のトランジスタTR1とNチャネル型のトランジスタTR2とで構成される。トランジスタTR1およびトランジスタTR2の各々のバックゲートには閾値制御信号C1が供給される。閾値制御信号C1は、インバータ回路Q1からの出力信号SOUT1のレベルが低下し始める時点にてローレベルに設定されるとともに当該時点の経過後にハイレベルに設定され、かつ、出力信号SOUT1のレベルが上昇し始める時点にてハイレベルに設定されるとともに当該時点の経過後にローレベルに変化する。

(もっと読む)

出力回路、出力方法、および電子機器

【課題】 簡易な構造を有する出力回路等を提供する。

【解決手段】 出力回路(14)は、ゲートを有する出力トランジスタ(OD)と、画素データ(LT)に応じて、第1のストローブ信号(STB)の波形をゲートに伝えるスイッチング素子(42)と、を備える。出力回路(14)は、第2のストローブ信号(XSTB)を入力し、第2のストローブ信号に基づく第3のストローブ信号(STB)を生成する信号生成回路(44)を、さらに備えることができる。第3のストローブ信号(STB)の立ち上がり時間(72)は、第2のストローブ信号(XSTB)の立ち上がり時間より長く、かつ/または、第3のストローブ信号(STB)の立ち下がり時間(74)は、第2のストローブ信号(XSTB)の立ち下がり時間より長い。スイッチング素子(42)は、画素データ(LT)に応じて、第3のストローブ信号(STB)の波形をゲートに伝えることができる。

(もっと読む)

電気回路、電気光学装置、電子機器、および電気回路の駆動方法

【課題】ヒステリシス特性を示すインバータ回路の構成を簡素化しながら消費電力を低減する。

【解決手段】インバータ回路Q1は、Pチャネル型のトランジスタTR1と、Nチャネル型のトランジスタTR2とで構成される。信号供給点R1とトランジスタTR1のチャネルコンタクト領域Aとの間には容量C1が介在し、信号供給点R1とトランジスタTR2のチャネルコンタクト領域Aとの間には容量C2が介在する。信号供給点R1には閾値制御信号SC1が供給される。閾値制御信号SC1は、インバータ回路Q1からの出力信号SOUT1のレベルが低下し始める時点にてローレベルに設定されるとともに当該時点の経過後にハイレベルに設定され、かつ、出力信号SOUT1のレベルが上昇し始める時点にてハイレベルに設定されるとともに当該時点の経過後にローレベルに変化する。

(もっと読む)

演算増幅器及び駆動回路、液晶表示装置の駆動方法

【課題】立ち上がりと立ち下がりのスルーレートを対称とすることができ、2H反転駆動時の駆動電流を確保すること。

【解決手段】本発明の一態様に係る演算増幅器は、第1電源及び第2電源との間に直列に接続された第1出力トランジスタ及び第2出力トランジスタと、前記第1出力トランジスタ及び第2出力トランジスタの間のノードに接続された出力端子と、前記第1出力トランジスタのゲートと前記出力端子との間、及び、前記第2出力トランジスタのゲートと前記出力端子との間の一方のみに設けられた位相補償素子と、記第1出力トランジスタのゲート及び前記第2出力トランジスタのゲートとの間に接続された浮遊電流源とを備えたものである。

(もっと読む)

201 - 220 / 596

[ Back to top ]