Fターム[5J055EX21]の内容

Fターム[5J055EX21]に分類される特許

1 - 15 / 15

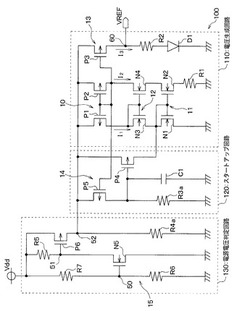

電圧検出回路

バンドギャップ基準電圧回路及びこれを用いたパワーオンリセット回路

【課題】バンドギャップ基準電圧回路100を確実に起動させることができる。

【解決手段】電源電圧がpMOSトランジスタP1のゲート電圧の閾値に到達する前には、pMOSトランジスタP6により電源VddとpMOSトランジスタP4のソース端子との間を開放させている。このため、電源電圧がpMOSトランジスタP1のゲート電圧の閾値に到達する前に、抵抗素子R3aによってコンデンサC1から電荷を放出させて、コンデンサC1のプラス電極の電位をpMOSトランジスタP4のゲート端子の電位の閾値よりも低くすることができる。電源電圧が上昇してpMOSトランジスタP6が電源VddとpMOSトランジスタP4のソース端子との間を接続すると、pMOSトランジスタP4がオンして、電源VddからpMOSトランジスタP6、P4を通してスタートアップ電流をnMOSトランジスタN1、N2のゲート端子に流すことができる。

(もっと読む)

半導体素子制御装置

【課題】駆動用半導体素子が意図せずに導通することを防止できる半導体素子制御装置を提供する。

【解決手段】駆動用トランジスタTr11は、一対の直流電源線13、14間に直流モータ12とともに直列に接続される。抵抗素子R13は、直流電源線13と駆動用トランジスタTr11のゲート端子との間に接続される。コンデンサC11および開路用トランジスタTr14の直列回路は、駆動用トランジスタTr11のゲート端子と直流電源線14との間に接続される。駆動制御回路15は、通常状態に設定されると、開路用トランジスタTr14をオンし、制御用トランジスタTr12、Tr13を通じて駆動用トランジスタTr11の導通状態を制御する。駆動制御回路15は、制御用トランジスタTr12、Tr13の双方がオフのとき、開路用トランジスタTr14をオフする。

(もっと読む)

出力回路および出力制御システム

【課題】回路面積の縮小を図りつつ、待機電流をカットオフすることが可能な出力回路を提供する。

【解決手段】出力回路は、第1の電源にソースが接続された出力pMOSトランジスタを備える。出力回路は、第1の出力pMOSトランジスタのドレインと接地との間に接続された出力nMOSトランジスタを備える。出力回路は、出力pMOSトランジスタのドレインと前記出力nMOSトランジスタのドレインとの間に接続された出力端子を備える。出力回路は、前記出力pMOSトランジスタのオン/オフを制御するための第1のゲート制御信号を第1のゲート制御端子から出力する第1のレベルシフタ回路を備える。出力回路は、前記出力nMOSトランジスタのオン/オフを制御するための第2のゲート制御信号を第2のゲート制御端子から出力する第2のレベルシフタ回路と、を備える。

(もっと読む)

表示装置の駆動回路

【課題】一導電型のTFTのみを用いて回路を構成することにより工程削減が可能であり

、かつ出力信号の電圧振幅が正常に得られる表示装置の駆動回路を提供する。

【解決手段】出力ノードに接続されているTFT203のゲート−ソース間に容量205

を設け、TFT201、202からなる回路は、ノードαを浮遊状態とする機能を有する

。ノードαが浮遊状態のとき、容量205によるTFT203のゲート−ソース間の容量

結合を利用してノードαの電位をVDDよりも高い電位とし、これによって、TFTのし

きい値に起因する振幅減衰が生ずることなく、正常にVDD−GND間の振幅を持った出

力信号を得ることが出来る。

(もっと読む)

半導体回路、インバータ回路および半導体装置

【課題】簡便な回路構成で過電圧から素子を保護する。

【解決手段】高電圧で抵抗値を制御可能なN1において、ドレイン端子は、抵抗R6を介して出力素子NO5のゲート端子(制御端子)、ソース端子は、NO5のエミッタ端子、そして、ゲート端子は、NO5の出力端子であるコレクタ端子に接続される。入力端子がHiレベルの場合、NO5はオフし、この状態で別に設けられた高圧回路の高電位側にNO5の出力端子を接続し、低電位側にVDD4のマイナス電極を接続すると、NO5のコレクタ−エミッタ間には所望の高電圧が印加される。入力端子をLoレベルに切替えると、PD2はオン、NO5の出力端子には未だ高電圧が印加されているので、N1もオンの状態となり、NO5の電流駆動能力は低い状態ではあるが、オン状態となる。

(もっと読む)

半導体スイッチ回路

【課題】 半導体スイッチ回路に要求される挿入損失特性、ハンドリングパワー特性、歪み特性を損なわず、高いアイソレーション特性を実現することができる半導体スイッチ回路を提供する。

【解決手段】 2つの入出力端子間に、直列接続した複数の電界効果トランジスタで構成される第1のスイッチ素子と、一方の入出力端子と接地との間に、直列接続した複数の電界効果トランジスタで構成される第2のスイッチ素子とを備え、第1のスイッチ素子及び第2のスイッチ素子の接続点と第2の入出力端子との間に、1つの電界効果トランジスタで構成される第3のスイッチ素子を備える。

(もっと読む)

ブートストラップ回路並びにこれを用いたシフトレジスタ、走査回路及び表示装置

【課題】 単一導電型のトランジスタで構成されるシフトレジスタにおいて、回路の小型化及び低消費電力化を図る。

【解決手段】 第1の接点(ノードN1)の電圧が電源電圧よりも高くあるいは低くなることで出力に電源電圧の電圧を出力するブートストラップ回路を含んだシフトレジスタであって、前記第1の接点に2個以上直列接続されたトランジスタ(Tr1、Tr2)と、前期トランジスタのドレイン・ソース間電圧が電源電圧以下となるように前記トランジスタ間の第2の接点(ノードN2)に電圧を供給する手段と、前記第1の接点に接続されゲート電極が第1の入力端子に接続された第1の入力トランジスタ(Tr3)と、出力端子とクロック信号に接続されかつゲート電極に前記第1の接点が接続された出力トランジスタ(Tr7)を有し、出力トランジスタのゲート電極はブートストラップする期間以外、開放状態にならない。

(もっと読む)

定電圧電源回路及び定電圧電源回路の動作制御方法

【課題】 動作させる定電圧回路を切り換えるときに起こりうる出力電圧のオーバーシュートの発生を防止することができ、一定の出力電圧を供給することができる定電圧電源回路及び定電圧電源回路の動作制御方法を得る。

【解決手段】 定電圧回路2及び3で出力端子OUTを共有し、定電圧回路2が作動開始する際、作動開始する定電圧回路2の誤差増幅回路A11に入力される基準電圧Vr1の立ち上がりを誤差増幅回路A11に入力される分圧電圧VFB1よりも遅れるように、遅延回路14を使用して基準電圧発生回路11への電源供給を遅らせるようにした。

(もっと読む)

駆動回路

【課題】本発明は、ターンオン時及びターンオフ時の過渡時、消費電力のロスを低減でき、且つ出力電流の高周波成分によるEMIノイズの発生を低減することができる駆動回路を提供する。

【解決手段】一方の端子に負荷が接続されたドライバ素子2のオン/オフを制御する駆動回路であって、ドライバ素子2の制御端子に電流を流し込むスイッチ素子4と、ドライバ素子2の制御端子から電流を引き出すスイッチ素子3とを有するスイッチング回路1と、ドライバ素子2の制御端子と他方の端子との間に設けられた容量素子8とを備える。

(もっと読む)

半導体素子制御装置

【課題】 駆動用半導体素子のリーク電流測定を正確に行うことを可能とする半導体素子制御装置を提供する。

【解決手段】 負荷2に通電を行うためのPチャネルMOSFET1についてリーク電流を測定したい場合には、FET21をオフにしFET1のゲートと電源との電気的接続を断つことでFET1と制御IC24とを電気的に接続した状態でも、リーク電流を容易に測定することが可能となる。

(もっと読む)

リセット信号出力回路を備えた電子機器

【課題】電子機器において、起動時等における電源電圧をモニタして、適宜リセット信号を出力するための部品を別途追加することなく、リセット信号出力回路を安価に構成し、機器のコストダウンを図る。

【解決手段】温度信号出力回路5に用いられているICに含まれる余剰のコンパレータを用いて、リセット信号出力回路4のコンパレータ10,20を構成する。コンパレータ10の−入力端子には抵抗R11,R12によってVcc1を分圧して得た所定電圧V1を、+入力端子には抵抗R21,R22によってVcc2を分圧して得た所定電圧V2をそれぞれ印加する。さらに、+入力端子に接続したコンデンサCによって+入力端子の電圧変動を遅延させ、Vcc1が十分に安定するまでコンパレータ10が制御回路2にローのリセット信号を継続して出力し、制御回路2の動作を停止させる。

(もっと読む)

差動出力回路

【課題】簡単な回路構成で、チャージインジェクションによるノイズの影響を低減できる差動出力回路を提供すること。

【解決手段】第1,第2の電位VDD,VSSの間に、第1〜第4のトランジスタT1〜T4が接続され、トランジスタT1,T3の第1の共通ゲートとトランジスタT2,T4の第2の共通ゲートに対して、差動のクロック信号が入力され、トランジスタT1,T3の第1の共通ドレインとトランジスタT2,T4の第2の共通ドレインとから、差動のクロック信号が出力可能とされ、第1〜第4のダミートランジスタC1〜C4は、第1〜第4のトランジスタT1〜T4の夫々に対応して設けられ、ゲートには対応する各トランジスタに供給される前記クロック信号とは逆相のクロック信号が入力され、対応する各トランジスタがオンからオフになる時にオフからオンしてチャージインジェクションをキャンセルするものである。

(もっと読む)

半導体装置および制御方法

【課題】 消費電力を低減することができる半導体装置を提供する。

【解決手段】 半導体装置100は、電源電圧が供給される電源端子5とグランド端子6間に接続され、入力端子41乃至43から入力された信号をデコードするデコーダ103と、電源端子5とデコーダ103間を切断する電源制御回路109とを含む。電源制御回路109は、入力端子41乃至43とデコーダ103間にワイヤボンディングで並列接続される。電源制御回路109は、入力端子41乃至43から入力される信号の組み合わせのうち、デコード時に使用していない信号の組み合わせを用いてドレインスイッチFET91を制御する制御信号を生成するロジック93を含む。

(もっと読む)

ノイズ低減回路

【課題】 クロストークノイズを安定して減少させることができ、クロストークノイズに起因する回路誤動作を確実に防止できるノイズ低減回路を提供する。

【解決手段】 電源側に並列に接続された第一及び第二のトランジスタと、前記第二のトランジスタの出力側に直列接続された抵抗手段とを設け、前記抵抗手段の出力側と前記第一のトランジスタの出力側とを出力ノードで接続し、前記出力ノードから出力される出力電圧の変化が段階的になるように前記第一及び第二のトランジスタのオン/オフ動作タイミングを制御する制御回路を備えた。

(もっと読む)

1 - 15 / 15

[ Back to top ]