Fターム[5J055EZ08]の内容

Fターム[5J055EZ08]に分類される特許

1 - 20 / 207

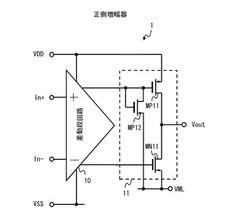

出力回路及びそれを備えた増幅器

【課題】出力波形に付加される遅延の増大を抑制することが可能な出力回路を提供すること。

【解決手段】本発明にかかる出力回路は、高電位側電源端子と外部出力端子Voutとの間に設けられ、電源電圧VDD〜接地電圧VSS間の電圧範囲を振幅する一対の増幅信号の一方に基づいてソース−ドレイン間に流れる電流が制御される出力トランジスタMP11と、低電位側電源端子と外部出力端子Voutとの間に設けられ、一対の増幅信号の他方に基づいてソース−ドレイン間に流れる電流が制御される出力トランジスタMN11と、電源電圧VDDより低く接地電圧VSSより高い中間電圧VMLが供給されている低電位側電源端子と、出力トランジスタMP11のゲートと、の間に設けられ、出力トランジスタMP11のゲート電圧と中間電圧VMLとの電圧差に基づいて出力トランジスタMP11のゲートをクランプするクランプ用トランジスタMP12と、を備える。

(もっと読む)

昇圧回路及びその給電方法

【課題】簡略化された回路構成でノイズ低減効果を持つ多相駆動型の昇圧回路を実現する。

【解決手段】昇圧回路は、所定周期のクロック信号を出力する発振回路と、前記クロック信号の1本の配線に直列接続され、トータル遅延時間が前記所定周期よりも長い複数の遅延回路と、前記複数の遅延回路に対応して前記1本の配線に接続された複数の分割昇圧回路と、を含む。

(もっと読む)

アナログマルチプレクサ

【課題】アナログデータ出力にクロック信号が混入しないアナログマルチプレクサを提供する。

【解決手段】アナログマルチプレクサは、2つのアナログデータ信号D1,D2の非反転信号を入力とし、クロック信号CLKに応じて2つのアナログデータ信号D1,D2のうち何れか一方を選択的に出力する第1のセレクタ4と、2つのアナログデータ信号D1,D2の反転信号を入力とし、クロック信号CLKに応じて2つのアナログデータ信号D1,D2のうち何れか一方を選択的に出力する第2のセレクタ5と、第1のセレクタ4の出力信号と第2のセレクタ5の出力信号との差信号を出力する減算回路6とを備える。

(もっと読む)

受信回路、半導体装置、センサ装置

【課題】受信動作への切換時に発生するノイズを抑制する。

【解決手段】受信回路10は、圧電センサ2の受信信号SP及びSNを増幅するアンプ15と、圧電センサ2の一端とアンプ15の一端との間に並列接続されて受信動作への切換時に位相をずらしてオンされる複数のトランジスタ11a及び11b(ないしは12a及び12b)と、を有する。

(もっと読む)

負荷駆動装置

【課題】負荷電流検出手段により検出された負荷電流を用いてリーク故障を確実に検出する。

【解決手段】駆動回路33a、33bの出力端子Ta2、Tb2から電源線6に至る還流経路内にシャント抵抗9a、9bを接続し、電源線5と給電分岐点Nsとの間に共通のシャント抵抗24を接続する。駆動制御回路32は、MOSFET7a、7bをPWM駆動し、負荷電流検出回路12a、12bから負荷電流Ia、Ibを入力し、総電流検出回路23から総電流Isを入力する。検出負荷電流Ia、Ibに対しそれぞれ対応するPWM駆動信号のオフ駆動期間をマスク処理し、マスク処理した検出負荷電流Iam、Ibmを加算した加算電流Icmと検出総電流Isとを比較する。両者が等しい場合には正常状態と判定し、異なる場合にはショート故障またはリーク故障が生じたと判定する。

(もっと読む)

信号変換回路、その信号変換回路を備えるアイソレータ回路及び信号変換方法

【課題】高い周波数の差動信号をシングルエンドの信号に変換可能な信号変換回路、当該信号変換回路を備えたアイソレータ回路及び信号変換方法を提供すること

【解決手段】本発明にかかる信号変換回路10は、差動信号である信号D1及び信号D2が入力されるヒステリシスコンパレータ1、2及び変換バッファ3を備える。ヒステリシスコンパレータ1は、信号D1の電位V1と信号D2の電位V2との大小の比較結果を信号E1として出力する。ヒステリシスコンパレータ2は、電位V1と電位V2との大小を比較し、当該比較結果を信号E1の反転信号である信号E2として出力する。変換バッファ3は、信号E1及び信号E2をシングルエンド信号Fに変換する。

(もっと読む)

インターフェース回路

【課題】ノイズを低減することができるインターフェース回路を提供することを課題とする。

【解決手段】インターフェース回路は、電源電圧端子が第1の電源電圧ノードに接続され、入力信号を増幅する第1のバッファ(111)と、第2の電源電圧ノード及び前記第1のバッファの電源電圧端子間に接続されるスイッチ(124)と、前記第1のバッファの入力信号がローレベルからハイレベルに立ち上がると、遅延時間経過後に前記スイッチをオフからオンに切り換える第1の制御回路(127)とを有する。

(もっと読む)

差動入力バッファ

【課題】動作モード切り換え時におけるノイズを抑制する。

【解決手段】差動入力バッファ1は、動作モードを通常状態又は省電力状態のいずれかに切り換える電源回路MN1,MN2と、ソースフォロア回路を構成する半導体素子MP1,MP3及びMP2,MP4のそれぞれの寄生容量の合計である第1の寄生容量に対応する第2の寄生容量を有する半導体素子MP7,MP8により構成されるダミー回路とを有し、動作モードの切り換え時に第1の寄生容量に起因して発生する電流の流通方向と、動作モードの切り換え時に第2の寄生容量に起因して発生する電流の流通方向とが共通の配線において相反する構成を有する。

(もっと読む)

高周波スイッチモジュール

【課題】スイッチポート切替時間が短く、かつ低消費電力、低面積を同時に満たす高周波スイッチモジュールを提供する。

【解決手段】デコーダ3は、前記スイッチポートを切替える制御信号CNTに応答し、スイッチ7を制御するためのスイッチ制御信号SWCNTを生成して、スイッチ切替タイミング検出器は、スイッチ制御信号SWCNTに応答し、スイッチ切替え検出信号t_swを生成し、周波数制御信号生成器は、スイッチ切替え検出信号t_swに応答し、周波数制御信号ICONT、CCONTを生成し、負電圧発生回路は、周波数制御信号ICONT、CCONTに応答し、前記負電圧発生回路内で生成したクロック信号の周波数を2つ以上のそれぞれ異なる周波数に切替つつ、負電圧出力信号NVG_OUTを生成し、スイッチ7は、スイッチ制御信号SWCNTと前記負電圧出力信号NVG_OUTに応答し、複数の高周波信号ポート間の経路を切替える。

(もっと読む)

入出力回路

【課題】回路規模の増大を抑制しながら、コネクタに接続されたチャージャーの種類を的確に認識する。

【解決手段】電源検出回路12は、VBUS端子への外部からの給電を検出する。チャージャー検出回路14は、DP端子およびDM端子の電圧を検出することにより、チャージャーの種類を特定する。チャージャー検出回路14は、DP端子およびDM端子の少なくとも一方のオープン、プルアップ、プルダウンまたは両端子間のショートを検出する。

(もっと読む)

電流スイッチ回路およびDA変換器

【課題】差動出力電流のグリッチを打ち消しつつ、電源およびグランドに発生したノイズを打ち消す。

【解決手段】スイッチトランジスタM1、M2は、差動入力電圧Dip、Dimに基づいてスイッチング動作することで入力電流Iinを電流Ii1、Ii2に変換し、雑音電流発生回路1は、入力電流源2を介して流れる雑音電流を模擬したダミー電流Ibを生成し、スイッチトランジスタM3、M4は、差動入力電圧Dip、Dimに基づいてスイッチング動作することでダミー電流Ibを電流Ii3、Ii4に変換し、電流Ii1、Ii2に逆相的に重畳する。

(もっと読む)

半導体出力回路及び外部出力信号生成方法並びに半導体装置

【課題】電源電圧の低下による外部出力信号のばらつきを抑制する。

【解決手段】内部入力信号Aの電位がグランド側からVDD側、あるいはVDD側からグランド側へ変化するのに応じて、出力部1は外部出力信号EBの電位を変化させる。差動部2は、外部出力信号EBと、所定の基準信号VREFとに応じた出力信号を出力し、外部出力信号EBが所定の基準信号VREFに応じた電位となるようボルテージフォロアとして機能する。これにより、外部出力信号EBの低電圧側出力電圧VOLのばらつきを抑制する。

(もっと読む)

スイッチング素子の駆動回路

【課題】定電流制御に異常が生じる場合、スイッチング素子S*#が熱破損するおそれが生じたり、スイッチング状態の切替に伴うサージが過度に大きくなったりするおそれがあること。

【解決手段】電源20から出力される正の電荷は、異常検出用抵抗体22、定電流用抵抗体24および充電用スイッチング素子32を介してスイッチング素子S*#のゲートに充電される。この際、定電流用抵抗体24の電圧降下量が規定値となるように、オペアンプ36によって充電用スイッチング素子32のゲート電圧が操作される。異常検出用抵抗体22の電圧降下量は、充電側異常判断部62に取り込まれ、これに基づき定電流制御の異常の有無が判断される。

(もっと読む)

ドライバ回路およびそれを用いた試験装置

【課題】ポジティブエッジの波形、ネガティブエッジの波形の少なくとも一方を調節可能なドライバ回路を提供する。

【解決手段】分岐回路10は、送信すべき入力信号SINを複数の経路12に分岐する。各タイミング調節回路20は、それぞれが対応する経路に分岐された送信すべき信号Saのポジティブエッジおよびネガティブエッジの少なくとも一方に遅延を与える。合成出力回路30は、複数のタイミング調節回路20の出力信号Sbを合成し、合成された信号SOUTを伝送線路3に出力する。

(もっと読む)

ゲート駆動回路及び半導体装置

【課題】応答性を損なうことなく能動クランプ素子の損失電力を低減できる能動クランプ回路を用いたゲート駆動回路及び半導体装置を提供する。

【解決手段】スイッチ素子Tr7のゲートを駆動するゲート駆動回路であって、制御信号に基づいてスイッチ素子Tr7を駆動する駆動部(トランジスタTr1,Tr2,Tr4,Tr5)と、スイッチ素子Tr7の第1主端子(ドレイン)と第2主端子(ソース)との間に印加される電圧が所定電圧以上の場合に、駆動部によるスイッチ素子Tr7に対する駆動動作を強制的に遮断して、スイッチ素子Tr7の第1主端子と第2主端子との間の電圧がクランプされるようにスイッチ素子Tr7を駆動するアクティブクランプ回路(ダイオードD1、ツェナーダイオードZD1、抵抗R1、トランジスタTr3,Tr6)とを備える。

(もっと読む)

電気回路および/または電子回路に関するコンフィギュレーション方法ならびにデバイス

【課題】同じタイプの特性量を有し、この特性量の値が相互に比例するいくつかの機能ブロックを備える電気回路をコンフィギュレーションする。

【解決手段】機能ブロックは、同様のタイプの少なくとも1組の電気素子(102a〜102d、104a〜104d)と、前記電気素子を互いに接続するおよび/もしくは電気回路100の残部に接続するための手段(106a〜106d、108a〜108d、110a〜110d)とにより構築され、テストされる1組の接続コンフィギュレーションのそれぞれに対して、電気回路のパラメータの値を測定するステップと、テストされる結合コンフィギュレーションの中から、測定されたパラメータの値が、少なくとも1対の機能ブロックの特性量の値間の不整合が最小の1つのコンフィギュレーションを選択するステップと、選択されたコンフィギュレーションに従って、接続する手段をポジショニングするステップとを含む。

(もっと読む)

負荷駆動回路の保護装置

【課題】FET(T1)のドレイン電流IDが急激に増加し、電圧Vdsが増加する過渡期間であっても、FET(T1)の温度上昇量を忠実に示す信号を生成することが可能な負荷回路の保護装置を提供する。

【解決手段】FET(T1)の両端に生じる電圧Vdsに比例する電流Iaを流す電流変換回路21と、この電流Iaを通電するインピーダンス回路22を備える。そして、FET(T1)の過渡熱抵抗の時間に対する変化を示す関数を過渡熱関数Rth(t)としたとき、FET(T1)に、ゼロから階段状に増加する電流を通電した際に、インピーダンス回路22の点P2に生じる電圧V5が、過渡熱関数Rth(t)の平方根に比例した電圧となるように、前記インピーダンス回路のインピーダンスを設定する。そして、電圧V5が判定電圧V6を上回った場合に、FET(T1)を遮断して負荷駆動回路を過熱から保護する。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】出力信号遅延を抑制し、消費電流の増大を抑制する出力回路の提供。

【解決手段】入力端子101と出力端子102の電圧を差動入力する差動入力段110からなる差動増幅回路と、第1及び第2の電源端子VDD、VSSに接続された第1及び第2のカレントミラー130、140と、前記第1及び第2のカレントミラーの入力間、出力間に接続される第1、第2の連絡回路150L、150Rと、第1導電型の第1のトランジスタ121と第2導電型の第2のトランジスタ122とからなる出力増幅回路と、前記第1、第2の電源端子VDD、VSSの電源電圧の間の電圧が供給される第3の電源端子VMLの電圧に応じたバイアス信号を受ける第1導電型の第3のトランジスタ161からなる制御回路160と、を備えている。

(もっと読む)

ミリメートル波減衰器及びシャントスイッチング回路

【課題】ミリメートル波周波数において有効な切替え可能減衰器を提供する。

【解決手段】入力減衰器22は、直列結合されているRF_IN+端子、第1のノード、伝送線路TL3、直流遮断キャパシタCbl3、第2のノード、第3のノード、及び出力端子を有する第1の入力回路215を有する。第1のノードは、直列結合されているキャパシタCm3及び第1のシリコンゲルマニウムヘテロ接合バイポーラトランジスタQ9を介して選択的に接地へ結合される。第2のノードは、キャパシタCm1を介して接地へ結合されている。第3のノードは、直列結合されている直流遮断キャパシタCbl1、抵抗Ratt1及び第2のシリコンゲルマニウムヘテロ接合バイポーラトランジスタQ7を介して選択的に接地へ結合される。入力減衰器22は、更に、第1の入力回路215と並列に、第1の入力回路215と同じ構造を有する第2の入力回路216を有する。

(もっと読む)

レギュレータ用半導体集積回路

【課題】 外部から回路をオン、オフ制御するための制御端子を有するレギュレータ用ICにおいて、制御信号による起動直後に出力端子に向かってラッシュ電流が流れるのを防止できるようにする。

【解決手段】 制御回路のオン、オフを指示する制御信号が入力される外部制御端子(CE)とを備えたレギュレータ用ICにおいて、電圧入力端子または出力端子と接地電位端子との間に直列に接続された電流源(Tr0,R3)と基準電圧回路(Tr2,Tr3)を設け、該電流源と基準電圧回路との接続ノードは外付けのコンデンサが接続される外部端子(CS)に接続し、基準電圧回路はデプレッション型MOSトランジスタとエンハンスメント型MOSトランジスタが直列に接続され、それらのトランジスタのしきい値電圧の差に相当する電圧を出力するように構成した。

(もっと読む)

1 - 20 / 207

[ Back to top ]