Fターム[5J055EZ53]の内容

電子的スイッチ (55,123) | 機能的回路 (8,211) | 電源回路、特徴がある定電圧回路 (631) | 負電源、基板バイアス回路 (31)

Fターム[5J055EZ53]に分類される特許

1 - 20 / 31

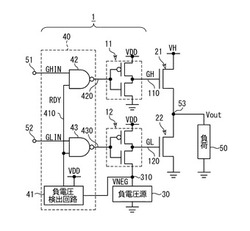

ゲート駆動回路、電力変換回路、3相インバータ、及びゲート駆動方法

【課題】電力変換回路において、ノーマリオン型トランジスタを利用したスイッチング素子への貫通電流を抑制する。

【解決手段】ハイサイドトランジスタ21とローサイドトランジスタ22の少なくとも一方は、ノーマリオン型トランジスタである。2つのゲート駆動回路11、12の少なくとも一方は、正電源から供給される第1電源電圧VDDと、負電圧源30から供給され接地電圧GNDよりも低い第2電源電圧VNEGとに応じた駆動電圧GH、GLを、ノーマリオン型のトランジスタのゲートに出力する。制御回路40は、第2電源電圧VNEGが参照電圧Vrefよりも高い場合、ハイサイドトランジスタ21に流れるドレイン電流を遮断する。

(もっと読む)

半導体スイッチ及び無線機器

【課題】高周波特性を改善した半導体スイッチ及び無線機器を提供する。

【解決手段】電源回路と、駆動回路と、スイッチ部と、第1の電位制御回路と、を備えた半導体スイッチが供給される。前記電源回路は、負の第1の電位を生成する第1の電位生成回路と、電源電位を降圧した正の第2の電位を生成する第2の電位生成回路と、を有する。前記駆動回路は、前記第1の電位と第3の電位とが供給され、端子切替信号に基づいて前記第1の電位及び前記第3の電位の少なくとも一方を出力する。前記スイッチ部は、前記駆動回路の出力に応じて複数の高周波端子のいずれか1つに共通端子を接続する。前記第1の電位制御回路は、第1のトランジスタを有する分割回路と、第2のトランジスタを有する増幅回路と、を有する。

(もっと読む)

パルス信号出力回路およびシフトレジスタ

【課題】安定して動作することが可能なパルス信号出力回路及びそれを含むシフトレジスタを提供する。

【解決手段】酸化物半導体を用いたトランジスタを複数用いて、パルス信号出力回路を構成する。また、パルス信号出力回路の動作に応じて、酸化物半導体を用いたトランジスタのしきい値電圧を変動させる。また、該パルス信号出力回路を含むシフトレジスタを構成する。これにより、安定して動作することが可能なパルス信号出力回路及びそれを含むシフトレジスタを提供することができる。

(もっと読む)

2線式交流スイッチ

【課題】2線式交流スイッチの低消費電力化を実現する。

【解決手段】

交流電源と負荷とを結ぶ電路に挿入される2線式交流スイッチであって、スイッチ端子S1、S2と、スイッチ端子間のオンオフを制御するためのゲート端子G1、G2と、基板端子Subとを有し、スイッチ端子間に双方向に電流を流すことができ、スイッチ端子S1が交流電源1に接続され、スイッチ端子S2が負荷2に接続される半導体スイッチからなるメインスイッチ3と、メインスイッチの基板端子Subを接地するかフローティングにするかを切り替えるサブスイッチ9と、を備える。

(もっと読む)

ゲートドライブ回路

【課題】ターンオン時のスイッチング特性が変動せず、電力損失を発生せずにスイッチング素子を安定してターンオンさせることができるゲートドライブ回路。

【解決手段】ワイドバンドギャップ半導体かなるスイッチング素子Q1のゲートに制御回路からの制御信号を印加することによりスイッチング素子をオンオフ駆動させるゲートドライブ回路であって、制御回路とスイッチング素子のゲートとの間に接続されたコンデンサC1と抵抗R1とからなる並列回路と、並列回路にコンデンサC2とスイッチング素子Q2と抵抗R2からなる直列回路がさらに並列接続され、コンデンサC2とスイッチング素子Q2との接続点にダイオードD1のアノードが接続され、ダイオードD1のカソードとスイッチング素子Q2のゲートはスイッチング素子Q1のソースに接続され、制御信号のオフ信号に対してスイッチング素子Q1ゲートを負電位にバイアスする。

(もっと読む)

CMOSインバータを用いたマルチプレクサ、デマルチプレクサ、ルックアップテーブルおよび集積回路

【課題】CMOSインバータのP形MOSトランジスタのボディバイアスを変化させても、入力信号の立ち上がりと立ち下がりの伝搬遅延時間の差を、従来のものより小さく保てるマルチプレクサ、デマルチプレクサ、ルックアップテーブルおよび集積回路を提供する。

【解決手段】パスゲートM1、M2の出力に初段出力バッファとして低しきい値CMOSインバータINV1を接続したセレクター回路を基本構成とし、それを用いたマルチプレクサ、デマルチプレクサ、ルックアップテーブルおよび集積回路であって、パスゲートはそのボディ端子が可変電位をとるボディバイアス電源VBNに接続し、INV1のP形MOSトランジスタM3のしきい値電圧を可変にできるようにそのボディ端子は可変電位をとるボディバイアス電源VBPに接続し、そのN形MOSトランジスタM4はそのしきい値電圧を固定するためにそのボディ端子が固定電位をとる電源VSSに接続する。

(もっと読む)

電圧レギュレータ

【課題】ノーマリオン型のトランジスタをオンオフ駆動できるようにする。

【解決手段】電圧レギュレータは,入力電圧に接続されたノーマリオン型の第1のトランジスタと,第1のトランジスタと出力端子との間に設けられたインダクタと,第1のトランジスタとインダクタとの接続ノードとグランド電圧との間に設けられた還流回路と,第1のトランジスタのゲートに駆動信号を供給する駆動回路と,グランド電圧に接続され,第1のトランジスタのオンオフ動作により接続ノードに生成されるパルス信号に基づいて負電圧を生成し,負電圧を駆動回路に供給する負電圧生成回路とを有する。

(もっと読む)

高周波半導体スイッチ装置

【課題】スイッチの切替時間を短縮できる高周波半導体スイッチ装置を提供する。

【解決手段】制御回路は、負電圧発生回路に接続されるとともに、出力ノードが高周波スイッチ回路に接続され、高周波スイッチ回路に供給するローレベルの制御信号として負電位の信号を供給するレベルシフト回路を有し、出力ノードに蓄積されている電荷を、レベルシフト回路が動作する前に放電させる。

(もっと読む)

CMOSアナログスイッチ回路、負電圧サンプリング回路

【課題】オン抵抗が低い導通状態で、グランド電圧に対して正電圧側と負電圧側に振幅する大信号入力を可能とするCMOSアナログスイッチ回路を提供する。

【解決手段】PMOSトランジスタ101、NMOSトランジスタ102のソース同士を入力端子106に接続し、ドレイン同士を出力端子107に接続して構成される相補構成のCMOSアナログスイッチ回路103において、PMOSトランジスタ101のバックゲートに正電源電圧を供給し、NMOSトランジスタ102のバックゲートに負電源電圧を供給し、正電源電圧または負電源電圧のうち、いずれか一方を負電圧制御信号S1としてPMOSトランジスタのゲートに供給し、他方を負電圧制御信号S2としてNMOSトランジスタのゲートに供給する。

(もっと読む)

クロック負昇圧回路

【課題】回路構成が簡易、小型でウェル・バイアス電圧の立ち上がり時間が短く、安定した負昇圧クロックを供給することが可能なクロック負昇圧回路を提供する。

【解決手段】クロック負昇圧回路部301、クロック負昇圧回路部302、クロック負昇圧回路部301、クロック負昇圧回路部302のウェル層上に設けられたNMOSトランジスタ107に電圧を供給するキャパシタ403、NMOSトランジスタ104を備え、クロック負昇圧回路部301が備えるNMOSトランジスタ104とキャパシタ403とを接続する電圧ライン303、クロック負昇圧回路部302が備える2つのNMOSトランジスタ104の出力を接続する電圧ライン303によってクロック負昇圧回路を提供する。

(もっと読む)

高周波スイッチング回路

【課題】相互変調特性と、電流消費との間のバランスが良好な高周波スイッチを有する携帯電話を提供する。

【解決手段】高周波スイッチング回路100は、高周波スイッチングトランジスタ110を備える。高周波スイッチング回路では、高周波スイッチングトランジスタのチャネル経路を介して、高周波信号経路がのびている。高周波スイッチング回路は、制御回路120を備える。制御回路は、制御回路が受信した制御信号140に応じて、少なくとも2つの異なるバイアス電位を、高周波スイッチングトランジスタの基板130に印加する。

(もっと読む)

スイッチ回路

【課題】シリーズFETおよびシャントFETとして4端子NMOSFETを用いるSPSTスイッチ回路では、シリーズFETがオン状態で、シャントFETがオフ状態のときに、SPSTスイッチ回路はオン状態になる。FETのバックゲートには寄生ダイオードが存在し、入力交流信号電圧が所定の閾値を超えると、寄生ダイオードがオン状態になる。その結果、SPSTスイッチ回路はスイッチ・デバイスとしての線形動作を維持できなくなり、挿入損失特性やゆがみ特性が悪化する場合がある。

【解決手段】FETのバックゲートに、バイアス電圧を印加するためのバイアス電源を設ける。このバイアス電源として、DC−DC変換回路を用いることで、SPSTスイッチ回路をシリコン半導体チップ化することが容易になる。

(もっと読む)

半導体装置、半導体装置の起動制御方法、及びシステム

【課題】安定した参照電圧生成が可能であり且つ適切なタイミングで起動信号を生成できる電源回路ユニットを備えた半導体集積回路を提供する。

【解決手段】半導体装置は、外部電源が投入されたことを検出して第1検出信号を出力する外部電源検出回路と、前記外部電源に基づいて内部電源電圧を生成する内部電源電圧生成回路と、前記第1検出信号に応答して第1参照電圧を生成する参照電圧生成回路と、前記参照電圧が所定電圧になったことを検出して第2検出信号を出力する参照電圧検出回路と、前記第2検出信号に応答して前記第1参照電圧に依存した第2参照電圧に基づいて、容量素子が負荷として結合されるバイアス電圧を生成するバイアス電圧生成回路と、前記第2検出信号に応答して前記バイアス電圧と前記外部電源の電圧もしくは前記内部電源電圧に依存したモニタ電圧とを比較してスタート信号を出力する電源電圧検出回路とを含む。

(もっと読む)

DC−DCコンバータ

【課題】出力短絡保護機能を設ける場合に、短絡電流をバイパスするバイパス回路を外部に設けることなく、内部回路(内部素子)を保護できるDC−DCコンバータの提供。

【解決手段】この発明は、直流電圧を昇圧して出力電圧を生成し、当該出力電圧の生成のために入力端子1と出力端子2との間に複数のMOSトランジスタM1〜M4が直列接続されたDC−DCコンバータである。MOSトランジスタM4は、自己の基板電位制御用のMOSトランジスタM41、M42を有する。DC−DCコンバータの定常動作時にはMOSトランジスタM42がオンし、MOSトランジスタM4の基板端子に出力端子2の電位が印加される。一方、DC−DCコンバータの出力短絡時にはMOSトランジスタM41がオンし、MOSトランジスタM4の基板端子に出力端子2とは反対側の電位が印加される。

(もっと読む)

電力供給制御回路

【課題】ターンオフ時に出力端子に発生する逆起電圧に対して、電源の逆接続回路の影響を受けずに過電圧保護回路が正常に動作する電力供給制御回路を提供することである。

【解決手段】第1電源ライン101と出力端子106との間に接続される出力トランジスタ109と、出力端子と第2電源ライン102との間に接続される負荷112と、出力トランジスタ109の制御端子と第1電源ライン101との間に接続され負荷からの逆起電圧に対して導通状態となるスイッチトランジスタ110を含んで構成される過電圧保護回路と、電源が電源ラインに逆方向に接続された場合は出力トランジスタの制御端子に対して電気通路を形成し、一方、正常に接続された場合はその電気通路を負荷からの逆起電圧に対しても遮断状態とする電源逆接続保護回路(114、115、121、122)を備えて構成される。

(もっと読む)

電源切換回路

【課題】 バイポーラ動作しない電源切換回路を提供する。

【解決手段】 デプレッション型(D型)NMOS15〜16はNMOSであるので、D型NMOS15〜16のソース電圧が電源電圧VPP1になっても、D型NMOS15〜16はバイポーラ動作しない。D型NMOS16はNMOSであるので、D型NMOS16のソース電圧が電源電圧VPP2になっても、D型NMOS16はバイポーラ動作しない。エンハンスメント型(E型)PMOS14のゲート電圧及びソース電圧が電源電圧VPP1になってドレイン電圧が電源電圧VPP2になっても、E型PMOS14のゲート電圧及びソース電圧はドレイン電圧よりも高いので、E型PMOS14はバイポーラ動作しない。

(もっと読む)

バックゲート切替回路、充電制御装置、電子機器

【課題】本発明は、電界効果トランジスタのソース・ドレインいずれが高電位となるか不定であるシステムにも好適に用いることが可能なバックゲート切替回路、並びに、これを用いた充電制御装置及び電子機器を提供することを目的とする。

【解決手段】本発明に係るバックゲート切替回路20は、端子T2から電力供給を受けて電圧Va、Vbの比較信号を生成する比較部(CMP、R1〜R5、N1)と;端子T3から電力供給を受けて反転比較信号を生成するインバータINVと;トランジスタ14のバックゲートと端子T2との間に接続され、反転比較信号に応じてオン/オフ制御されるトランジスタP1と;トランジスタ14のバックゲートと端子T3との間に接続され、比較信号に応じてオン/オフ制御されるトランジスタP2と;インバータINVの入力端及びトランジスタP2のゲートをプルダウンする抵抗(R6、R7)と;を有して成る。

(もっと読む)

電圧供給回路、表示装置、および電子機器、並びに電圧供給方法

【課題】同一極性のトランジスタにより形成されるパネル等に配置可能で、生産量の向上、工程数やコスト削減を図ることが可能な電圧供給回路、表示装置、および電子機器、並びに電圧供給方法を提供する。

【解決手段】制御端子が第1ノードAに接続され、第1端子が第2ノードBに接続され、第2端子が出力端子OUTに接続された出力トランジスタ121と、アクティブのリセット信号rstを受けてオンし所定電位Vrefと第1ノードAおよび第2ノードBとを接続するスイッチング素子122,123と、第1ノードAに接続されクロックが供給される第1キャパシタ124と、第2ノードBに接続されクロックが供給される第2キャパシタ125と、クロックの振幅を、第1ノードAと第2ノードBの電位が所定の差をもって変動するように調整する調整部と、を有し、リセット信号とクロックとは、逆相である。

(もっと読む)

ソースフォロワー型アナログバッファ、その補償動作方法およびそれを用いたディスプレイ

【課題】ソースフォロワー型アナログバッファ、補償動作方法およびディスプレイを提供する。

【解決手段】能動負荷を備えるソースフォロワー型アナログバッファ、新しい補償動作、および該ソースフォロワー型アナログバッファを複数備えたディスプレイを、アナログバッファの入力電圧と出力電圧の差である誤差電圧を抑制するべく、提供する。該ソースフォロワー型アナログバッファはまた、充電時間およびデバイス特性両方に基づくバラツキを最小限にとどめ、入力電圧の範囲を最大限に大きくすることができる。

(もっと読む)

MOSデバイスの保護回路

【課題】チップサイズの増大を抑制しながらも、MOSデバイスの駆動電圧を超える入力電圧が入力されても当該MOSデバイスの正常動作を可能にし得るMOSデバイスの保護回路を提供する。

【解決手段】保護回路10では、グランドレベルシフト回路10aにより入力電圧Vinの入力最小電圧よりも低くバッテリ電圧VBの電位にほぼ等しく駆動電圧Vddの電位を設定可能な仮想グランドVgndを、駆動電圧VddのグランドGndとする。これにより入力最大電圧がバッテリ電圧VBのアースEに対する駆動電圧Vddを超えてバッテリ電圧VB以下の入力電圧VinがCMOS回路50のCMOSデバイスに入力されても、入力電圧VinをCMOSデバイスの入力許容電圧幅内で入力できる。したがって高耐圧のCMOSデバイスを用いることなく、CMOSデバイスの正常動作を可能にし、チップサイズの増大を抑制しながらも、CMOSデバイスを正常に動作させられる。

(もっと読む)

1 - 20 / 31

[ Back to top ]