Fターム[5J055FX12]の内容

電子的スイッチ (55,123) | 制御、帰還信号の発生 (8,841) | 信号を得る箇所 (1,721) | 制御端子 (1,433)

Fターム[5J055FX12]に分類される特許

1,421 - 1,433 / 1,433

電力変換回路及び電力制御回路の動作及び回路

通常、並列なMOSFETは、電源用途において単一のゲート信号で駆動されるため、MOSFET間のカレントシェアリングが個々のMOSFETの特性に関して自動的に規定される。これは、MOSFET間の電流分布の大規模な非均一性をもたらす可能性がある。本発明によれば、MOSFETのオン抵抗の個々の制御が与えられ、このことが、並列化されたMOSFET間での改善されたカレントシェアリングを可能にする。  (もっと読む)

(もっと読む)

信号増幅用回路、及びアクティブマトリクス装置における同回路の使用

増幅回路はキャパシタ構造(42)と切替装置とを備える。キャパシタ構造は、電圧依存性静電容量を有する第一のキャパシタ(C2)と第二のキャパシタ(C1)(これもまた電圧依存性としてよい)とを有する。同回路は2つのモードで、すなわち少なくとも第一のキャパシタの一端子に入力電圧が提供される第一のモードと、切替装置によって第一及び第二のキャパシタ同士の間で電荷の再配分が起こることにより、第一のキャパシタにかかる電圧が変化し第一のキャパシタの静電容量が減少し、出力電圧が第一のキャパシタにかかる電圧に依存する第二のモードとで、動作可能である。本発明は電圧制御静電容量をキャパシタ間の電荷共有と併せて使用するものであり、これにより、結果的に電圧増幅特性が提供される。よってこの機構は、アナログ電圧の増幅に、または固定レベル(すなわちデジタル電圧)の昇圧に利用できる。よって本発明の回路は、レベルシフトまたは増幅のために、例えばアクティブマトリクスアレイ装置のピクセルでの用途に使用できる。  (もっと読む)

(もっと読む)

トラック/ホールド回路

スイッチ(10)とキャパシタ(12)を備えるトラック/ホールド回路である。第1のブートストラップスイッチ(14a)は、その入力として、クロック信号clkin及び入力信号Vinを有する。第1のブートストラップスイッチ(14a)から出力されるクロック信号clkbootは、スイッチ(10)のゲートに印加される。第1のブートストラップスイッチ(14a)は、電流源(20)という形のレベルシフト手段及びバッファ手段(30)を介して、当該回路の入力Vinと出力Vsとの間に接続されている。第2のブートストラップスイッチ(14b)が設けられており、第2のブートストラップスイッチ(14b)は、その入力として、クロック信号clkin及び入力信号Vinを有する。第2のブートストラップスイッチ(14b)から出力される逆位相クロック信号clknbootは、スイッチ(10)のいずれかの側に接続されている2つのダミースイッチ(16)のゲートに印加される。  (もっと読む)

(もっと読む)

半導体スイッチの高周波制御

共振ゲートドライバ回路は、例えば、MOSFETの効率的なスイッチングを提供する。しかし、共振ゲートドライバ回路は、高いスイッチング周波数が必要とされる用途を可能にさせないことがしばしばある。本発明によれば、共振ゲートドライバ回路のインダクタのプリチャージングが実行される。これは、MOSFETの極めてエネルギー効率が良い高速な動作を可能にさせる。  (もっと読む)

(もっと読む)

無線周波数用双極単投スイッチ

【解決手段】本発明の双極単投(DPST)スイッチは、第1入力ポートに対応する第1回路部と、第2入力ポートに対応する第2回路部と、及び出力ポートを有するスイッチ回路とを具備する。ここで、第1及び第2の回路部の各々は、分離チャンネルの一部を提供する少なくとも1個の第1トランジスタと、送信チャンネルの一部を提供する少なくとも1個の第2トランジスタと、送信チャンネル又は分離チャンネルのいずれかを選択する制御バイアスを提供する少なくとも1個の第3トランジスタとを有する。 (もっと読む)

吸収性マイクロ波単極単投スイッチ

【解決手段】本発明のスイッチ回路は、分離チャンネルの一部を供給する第1差動増幅器対(Q1,Q2)と、送信チャンネルの一部を供給する第2差動増幅器対(Q3,Q4)と、送信チャンネル又は分離チャンネルのいずれかを選択する制御バイアスを供給する第3差動増幅器対(Q5,Q6)とを具備する。このスイッチ回路は、500μm×250μmの小寸法でありながら、15GHz〜26GHzレンジにわたる入力及び出力間に35dBの分離を提供する。  (もっと読む)

(もっと読む)

データ転送方法、データ転送回路、出力回路、入力回路、半導体装置、電子装置

データ転送回路は、nビット(nは2以上の整数)の第1の2値電圧データを2n値の多値電流データに変換して、単一のデータ転送線に出力する電圧電流変換回路を備えている。電流比較回路は、前記データ転送線上の前記多値電流データを(2n−1)ビットの2値電流データに変換し、電流電圧変換回路は、前記(2n−1)ビットの前記2値電流データを(2n−1)ビットの第2の2値電圧データに変換する。計数回路は、前記(2n−1)ビットの前記第2の2値電圧データから前記nビットの前記第1の2値電圧データを復元する。 (もっと読む)

スイッチング回路における不感時間制御

DC−DC変換器は、入力端子(37)と接地端子(38)との間に直列に接続された2つの電界効果トランジスタ(35,36)を有する。両方のトランジスタ(35,36)がオフとなるときの不感時間の調整は、トランジスタ(35,36)の一方又は双方のドレイン(39,44)及びソース(43,40)に直接かけられてケルビンフィードバック接続部(71,72,67,68)を設けることによって行い、信号ラインの抵抗及びインダクタンスを回避するようにしている。  (もっと読む)

(もっと読む)

バッファにおける伝搬遅延及びプロセス及び温度の影響を低減する方法

低速出力エッジを有するバッファ回路が記載されている。パルスのより高値の電流が、ワンショットタイミング回路から駆動されて、出力MOSFETのターンオンか又はターンオフの開始を加速させるために、電流パルスが前記バッファの該出力MOSFETの制御ゲート内へと注入される。前記開始とターンオン及びターンオフとに至る時には、より低値の電流源が、前記出力MOSFETの前記ゲートを駆動するために継続する。一実施形態において、ワンショットは、入力信号の立ち上がりエッジと立ち下がりエッジとからトリガされる。前記より高値の電流パルスの効果は、バッファによる回路遅延を低減することである。更にまた、温度、供給電圧、及びプロセスの変動が起きる時に、実質的に一定となるようバッファ回路の遅延を維持するために、温度に応じるように、及び供給電圧に応じるように、パルス幅を設計することができる。

(もっと読む)

(もっと読む)

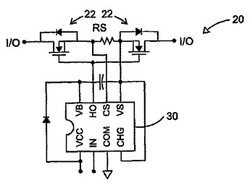

電流検出式の双方向スイッチおよびプラズマディスプレイ用の駆動回路

【解決手段】開示される双方向スイッチ(20)は、第1および第2の半導体スイッチング素子(22)と、これらのスイッチング素子に直列に接続されることによって直列回路を形成する電流センサ(RS)と、これら第1および第2のスイッチング素子がほぼ同時にオン・オフされるようにこれら第1および第2のスイッチング素子のオン・オフ操作を制御する駆動回路(30)であって、制御入力に応じてこれら第1および第2のスイッチング素子をオンにしたり電流センサの電流がほぼゼロ電流近くまで低下する際にこれら第1および第2のスイッチング素子をオフにしたりする駆動回路と、を備える。また、このような双方向スイッチ(20)を用いたプラズマディスプレイパネル(PDP)用の放電サステイン駆動回路も開示される。 (もっと読む)

ノイズ低減回路

【課題】 クロストークノイズを安定して減少させることができ、クロストークノイズに起因する回路誤動作を確実に防止できるノイズ低減回路を提供する。

【解決手段】 電源側に並列に接続された第一及び第二のトランジスタと、前記第二のトランジスタの出力側に直列接続された抵抗手段とを設け、前記抵抗手段の出力側と前記第一のトランジスタの出力側とを出力ノードで接続し、前記出力ノードから出力される出力電圧の変化が段階的になるように前記第一及び第二のトランジスタのオン/オフ動作タイミングを制御する制御回路を備えた。

(もっと読む)

定電流回路、記録素子基板及び記録装置

【課題】 温度変化や駆動素子の特性に影響されず、負荷に流れる電流を一定とする。

【解決手段】 負荷101と、負荷に直列に接続された駆動用トランジスタ102と、定電流源103と、PMOS差動対を構成し、それぞれのソースが定電流源103の出力に共通に接続され、それぞれのドレインがカレントミラー回路を構成するNMOSトランジスタ106及び107のドレインにそれぞれ接続されたPMOSトランジスタ104及び105とを設け、駆動用トランジスタ102のドレインの電位を一定とすることにより、負荷101に流れる電流を一定とする。

(もっと読む)

入力電源切替回路

【課題】 複数の電池の構成を切替えて電力変換効率を向上することに対応可能な入力電源切替回路の構成を提供する。

【解決手段】 第1の電池11の陽極端子と直列に接続する第1の電界効果トランジスタ31と、第2の電池12の陰極端子と直列に接続する第2の電界効果トランジスタ41と、該第1の電池11の陽極端子と該第2の電池12の陰極端子との間に切替手段を設け、かつ、該第1の電界効果トランジスタ31と該第2の電池12の陽極を接続する構成を特徴とする入力電源切替回路。

(もっと読む)

1,421 - 1,433 / 1,433

[ Back to top ]