Fターム[5J056BB19]の内容

Fターム[5J056BB19]に分類される特許

121 - 133 / 133

入出力回路および半導体入出力装置

【課題】 消費電力の増大を防止することが可能な入出力回路および半導体入出力装置を提供する。

【解決手段】 トライステート出力回路(入出力回路)1は、イネーブル信号oeに基づいて出力パッドPADoを駆動するP−MOSトランジスタ65と、P−MOSトランジスタ65のゲートに接続されたノードpgの電位を制御するためのP−MOSトランジスタ64と、イネーブル信号oeの信号レベルが遷移した際に所定時間幅のパルス信号oe5および−oe5を出力するワンショットパルス発生回路10と、パルス信号oe5および−oe5が出力されている期間、P−MOSトランジスタ64を制御するためのバイアス電圧Vbiasを生成し、バイアス電圧VbiasをP−MOSトランジスタ64のゲートに印加するバイアス回路30とを有する。

(もっと読む)

レベルシフタ回路

【課題】CMOSゲートのみで貫通電流を防止するレベルシフタ回路を提供する。

【解決手段】入力端子50からの入力信号Vinと遅延部21で遅延させた入力信号Vin’を、第1の電源電圧の低電位電圧VDDLが供給されるNORゲート22とANDゲート23に入力、各々出力をゲート電圧VG1とゲート電圧VG2とする。レベルシフト部10用で、第2の電源電圧の高電位電圧VDDHが供給される第2の電源電圧端子30に接続されたPMOSトランジスタ1,2のゲートとドレインを交差接続し、各々のドレインとソースが接地端子40に接続されたNMOSトランジスタ4,5のドレインとを接続する。NMOSトランジスタ4,5のゲートにはNORゲート22出力とANDゲート23出力を接続する。NMOSトランジスタ5のドレイン電圧VD2をPMOSトランジスタ3とNMOSトランジスタ6に接続し、出力信号Voutを出力端子70から出力する。

(もっと読む)

半導体集積回路及び制御方法

【課題】 電源分離を行った半導体集積回路にて、その一部の回路で電源がオフされた場合に貫通電流が流れることを防止できるようにする。

【解決手段】 電源がオン/オフされる回路モジュールCMA、CMB、CMCからの出力信号及び出力制御信号SA3、SB3、SC3が入力され、当該出力信号の受け先となる回路に出力を供給する論理ゲートを設け、電源がオン/オフされる回路モジュールに電源電圧の供給が開始された後に出力信号を論理ゲートから出力するように制御し、かつ論理ゲートの出力を所定電位に固定した後に電源がオン/オフされる回路モジュールへの電源電圧の供給を遮断するようにして、電源がオン/オフされる回路モジュールの出力がハイ・インピーダンスとなっても、その受け先となる回路の入力がフローティング状態になることを防止して貫通電流が流れることを防ぐことができるようにする。

(もっと読む)

レベルシフト回路及びこれを用いた携帯無線通信装置

【課題】

異なる電源で構成されるレベルシフト回路及びこれを用いた携帯無線通信装置では、一方の電源電圧が低下した場合、他方の電源で動作する後段回路の出力電圧を固定させ、動作を安定させる。

【解決手段】

入力信号が供給され、第1の電源電圧で動作し、入力信号に応じた第1の出力信号を出力する入力回路(16)と、入力信号と第1の出力信号の差を増幅して第2の出力信号を出力する増幅器14,15と、増幅器からの第2の出力信号のレベルに応じてラッチされた第3の出力信号を出力する第2の電源電圧で駆動されるラッチ回路17と、第2の電源電圧が供給され、第1の電源電圧に応じて出力電圧をラッチ回路の出力に供給するレベル設定回路18とを有し、第1の電源電圧が第2の電源電圧より低下した時にレベル設定回路を動作させて出力電圧を固定し、貫通電流を阻止する。

(もっと読む)

半導体集積回路

【課題】電源制御回路を設けることによる影響を低減するため、回路ブロックの規模に応じて電源制御回路を設ける。

【解決手段】回路ブロックRUSRを周回するように電源線VDD,VSS,VSSMを設け、これら電源線が配置される領域RPWRを利用して電源制御回路を配置する。

(もっと読む)

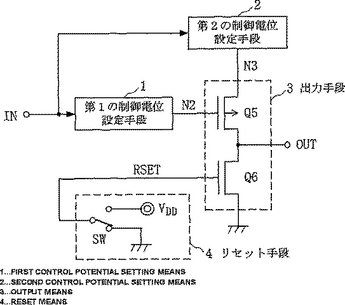

波形整形回路

第1の制御電位設定手段(1)は入力信号(IN)が論理閾値の近傍に達したときに第2の制御電位(N3)との大小関係が逆転する第1の制御電位(N2)を生成する。第2の制御電位設定手段(2)は、入力信号(IN)の変化に応じて入力信号(IN)と同方向に変化する第2の制御電位(N3)を生成する。出力手段(3)は、トランジスタ(Q5,Q6)からなり、第1の制御電位(N2)と第2の制御電位(N3)とリセット信号(RSET)とに基づいて所定の電位の出力信号(OUT)を生成する。リセット手段(4)は、波形整形回路の動作時にトランジスタ(Q6)をオフにする。  (もっと読む)

(もっと読む)

駆動回路

【課題】 低電圧電源から供給される電源電圧VDDが推奨動作電源電圧より低下しても、CMOS出力部等のプッシュプル出力部での貫通電流の発生を防ぐ駆動回路を提供する。

【解決手段】 ソースが高電圧電源に接続されドレインがIN4に接続されゲートがIN5に接続されたP型MOSトランジスタ2、ソースが高電圧電源に接続されドレインがIN5に接続されゲートがIN4に接続されたP型MOSトランジスタ3、ソースが接地されドレインがIN4に接続されゲートが低電圧信号を受けるN型MOSトランジスタ5、及び、ソースが接地されドレインがIN5に接続されたN型MOSトランジスタ6を有するレベルシフト部13と、P型MOSトランジスタ1及びN型MOSトランジスタ4を有するCMOS出力部14とを備え、P型MOSトランジスタ2の駆動電流は、N型MOSトランジスタ5の駆動電流より大きい。

(もっと読む)

半導体回路

【課題】 LSIのパワーオルエリアの電源投入・遮断時に貫通電流や誤動作を発生させることなく、確実に電源遮断状態に移行させる。

【解決手段】 パワーオフエリアにマスクレジスタ19を設け、電源遮断の前にこのマスクレジスタ19に“L”のマスク信号をセットする。バックアップエリア側では、パワーオフエリアから与えられるマスク信号を保持すると共に、このマスク信号が無電圧状態となったときには“L”を保持するラッチ回路33Aを設け、このラッチ回路33Aで保持したマスク信号を用いて、パワーオフエリア側との間の入出力信号をマスクする。

(もっと読む)

半導体集積回路

【課題】 特にD‐フリップフロップにおいて、従来、矛盾するとされていた低消費電力化と高速動作性の両立を実現すること。

【解決手段】 入力データ信号Dとクロック信号CKと制御信号として第1の帰還信号S01および第2の帰還信号S02を入力し、出力データ信号NQを出力するラッチ回路A1と、出力データ信号NQを保持するデータ保持回路A2と、入力データ信号Dと出力データ信号NQを入力し、入力データ信号Dと出力データ信号NQの論理の組み合わせにより第1の帰還信号S01、第2の帰還信号S02を生成する帰還回路A3とを備え、前記第1の帰還信号S01、第2の帰還信号S02によりラッチ回路A1の内部動作をオン/オフ制御することを特徴とする半導体集積回路。

(もっと読む)

出力バッファ回路

【課題】電源端子と基準電位点間に並列接続される複数の出力バッファに適用した場合、同時スイッチング時における貫通電流の大きさを減少でき、電源の電流容量が少なくて済み、また外部負荷によらず貫通電流を抑制可能とする。

【解決手段】電源端子と基準電位点間に並列接続された複数の出力バッファと、これらの出力バッファのうち第1の出力バッファを除く他の出力バッファの入力側に設けられる複数の判定回路で構成され、第n(nはn≧2の整数)の出力バッファの入力側の判定回路は、第1〜第n−1の出力バッファがスイッチング中であるか否かを判定し、前記第1〜第n−1の出力バッファのいずれかがスイッチング中であると判定した場合には、前記第nの出力バッファのスイッチングが前記第1〜第n−1の出力バッファのいずれかのスイッチングと同時に行われないように制御する判定手段とを備える。

(もっと読む)

レベル変換回路

第1の電源を制御する場合の貫通電流と遅延の増加を低減したレベル変換回路を提供することにある。

第1の電源が供給される第1の論理回路の信号レベルを第2の電源が供給される第2の論理回路の信号レベルに変換するというレベル変換回路において、レベル変換コア回路のGND電源端子とGND電源の間に第1の電源の制御に応じて制御信号を生成する第3の論理回路により制御されるスイッチ回路を配置し、前記レベル変換コア回路の出力に前記第3の論理回路により制御されるプルアップ/プルダウン回路を設けるという構成にしたことを特徴とする。  (もっと読む)

(もっと読む)

半導体集積回路装置

【課題】 I/O端子の信号状態を任意に設定することにより、I/Oバッファの貫通電流を防止するとともに、該I/Oバッファにおけるリークテストを可能にする。

【解決手段】 I/Oバッファ部12aには、状態設定回路16が設けられている。この状態設定回路16は、設定レジスタに格納された制御信号I1〜I3の組み合わせに応じてI/O端子Pの信号状態を任意に設定する。これにより、本来、信号保持状態に設定されるI/O端子Pであっても、一時的に、状態設定回路16によってI/Oバッファ部12aをHi−Z状態にすることにより、I/Oバッファ部12aの良否をテストするリークテストを行うことが可能となり、半導体集積回路装置の信頼性を向上させることができる。

(もっと読む)

インバータ回路とこれを用いた圧電発振器

【課題】CMOSインバータの貫通電流は、このインバータを用いた装置の電力消費量を増大させ、特に携帯機器においては電池の寿命を短くする。

【解決手段】従来のCMOSインバータと同じ回路のP-MOSTQ1のソースS回路に、別のP-MOSTQ3を直列に追加接続し、そのゲートと回路の入力端間を遅延回路Z1で接続し、また、前記CMOSインバータのN-MOSTQ2のソース回路に、別のN-MOSTQ4を直列に追加接続してそのゲートと回路の入力端間を遅延回路Z2で接続した回路構成にする。

(もっと読む)

121 - 133 / 133

[ Back to top ]