Fターム[5J056BB19]の内容

Fターム[5J056BB19]に分類される特許

21 - 40 / 133

半導体装置

【課題】電源分離領域内の配線密度を低下させる。

【解決手段】動作モードに応じて電源電圧が供給される電源線VVDDと、常に電源電圧が供給される電源線VDDと、通常モードで電源線VVDDを電源線VDDに接続するか、またはスリープモードで電源線VVDDを接地電位とするか、を切り替える電源切替回路(104、111、110が相当)と、電源線VVDDから電源供給されスリープモードでは動作を停止する第1回路ブロック101と、電源線VDDからの電源供給によって常に動作可能とする第2回路ブロック103と、電源線VVDDの電位が接地電位近傍にあるか否かにそれぞれ応じて、第2回路ブロック103の入力端をハイレベルにするか、第1回路ブロック101の出力信号を第2回路ブロック103に伝達可能とするか、を制御する入力制御回路(114、118が相当)と、を備える。

(もっと読む)

レベルシフト回路及び通信回路

【課題】 入力信号の電圧振幅の最大値と同電圧を供給する電源電圧の入力を必要とせず、異なる電圧振幅の入力信号が入力された場合でも動作可能であり、貫通電流による消費電力の増大を低減できるレベルシフト回路及び通信回路を提供する。

【解決手段】 出力信号の電圧振幅の最大値と同電圧を供給する第1電圧源と内部出力ノードN1の間に設けられた負荷抵抗回路R1と、入力信号の入力電圧を受け付け、制御ノードN2の電圧値を入力信号の電圧振幅の最大値に対応する制御電圧値に保持する電圧記憶回路11と、内部出力ノードN1と入力信号の入力ノードN3の間に設けられ、制御ノードN2の電圧と入力信号の電圧の電圧差に応じてON状態とOFF状態が切り替わるように構成され、入力信号の電圧値が電圧振幅の最大値の場合にOFF状態に、入力信号の電圧値が電圧振幅の最小値の場合にON状態になる第1スイッチング回路MN1と、を備える。

(もっと読む)

半導体集積回路

【課題】 電源ノイズを緩和しながら、内部回路が動作を開始するまでの時間を短縮する。

【解決手段】 内部回路は、基板電圧が供給されるトランジスタを含み、内部電源電圧を受けて動作する。電源スイッチは、内部回路を動作させるための電源オン信号の活性化中に外部電源線を内部電源線に接続する。基板電圧制御回路は、電源オン信号の活性化により上昇する内部電源電圧が目標電圧を超えたときに、基板電圧を第1電圧から第2電圧に変更する。第1電圧を基板電圧として受けているトランジスタのソース・ドレイン間電流は、第2電圧を基板電圧として受けているトランジスタのソース・ドレイン間電流より少ない。このため、電源スイッチがオンした後、内部電源電圧が低い期間にトランジスタのソース・ドレイン間電流を少なくでき、内部回路を流れる貫通電流を少なくできる。

(もっと読む)

容量性結合を用いる低電圧から高電圧へのレベル変換

【課題】高電圧出力トランジスタまたは回路のゲートを駆動するのに必要な電圧に達することができる。

【解決手段】電圧レベル変換回路は、デジタル論理回路と、第1および第2接続部を有するキャパシタであって、第1および第2接続部のうちの一方がデジタル論理信号へ電気的に結合された、少なくとも1つの高電圧キャパシタと、インバータ対であって、インバータ対のうちの少なくとも1つのインバータの出力が、少なくとも1つの高電圧キャパシタの他方の接続部へ電気的に結合された、たすき掛け結合型インバータ対とを備える。高電圧駆動回路は、2つの低電圧入力信号と、2つの信号であって、第1信号が高位側駆動信号であり、第2信号が低位側駆動信号である、2つの高電圧出力信号と、2つのレベル変換部であって、第1レベル変換部が高位側駆動信号に対応し、第2レベル変換部が低位側駆動信号に対応する。

(もっと読む)

集積回路装置

【課題】高い電源電圧を元に、低い電圧を発生させることで、低い電圧を用いる内部回路と高い電圧を用いる外部回路とのインターフェイスを行う場合、外部回路を動作させた状態で内部回路の動作を休止させる場合がある。この場合、低い電圧の発生を止めたことをインターフェイスを行う回路に伝達する回路(POC回路)が必要となるが、従来の回路では、低い電圧を発生させる状態で貫通電流が流れる回路を用いる必要があり、消費電流が増加してしまうという課題がある。

【解決手段】低い電圧の発生を停止する信号により、レギュレーター107の動作を止め、VOUTが十分下がった状態でインターフェイスを行う回路へ供給停止信号をレベルシフト回路121に伝達する。そのため、レベルシフト回路121での貫通電流の発生を抑えられる。さらに、供給停止信号を提供するPOC回路41内での定常状態での貫通電流を防止できる。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えつつ、出力電圧のばらつきをなくすことの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】5Tr2Cで構成されるインバータ回路において、容量素子C1がトランジスタTr5のソースに接続されるとともに、トランジスタTr4を介してトランジスタTr2のソースに接続されている。これにより、入力端子INに立下り電圧が入力され、トランジスタTr1,Tr3がオフしたときに、Vdd2が充電された容量素子C1によって、トランジスタTr2のゲートがVSS+Vth2以上の電圧にチャージされ、トランジスタTr2がオンする。

(もっと読む)

スイッチタイミング制御回路及び半導体装置

【課題】回路規模を大きくせずに複数のスイッチを貫通電流が流れないように確実に導通非導通のタイミングを制御するスイッチタイミング制御回路を提供する。

【解決手段】複数のデータフリップフロップが縦続接続され、縦続接続されたデータフリップフロップには共通のクロック信号が接続され、それぞれ前段のデータ出力信号が後段のデータ入力信号として接続され、初段のデータ入力信号には、最終段のデータ出力信号の論理が反転されて接続された分周回路と、複数のデータフリップフロップのうちそれぞれ複数の異なるデータフリップフロップの出力信号が入力端子に接続された複数の組み合わせ論理回路と、複数の組み合わせ論理回路の出力信号によりそれぞれ導通、非導通が制御される複数のスイッチと、を備える。

(もっと読む)

ダイナミック回路の初期化方法

【課題】ダイナミック回路において、評価制御トランジスタを省略してトランジスタのスタック段数を削減するとともに評価制御トランジスタの省略に伴う初期化動作時の貫通電流の発生を抑制する。

【解決手段】ダイナミック回路の初期化方法は、所定の条件でダイナミックノードの初期化を開始するステップと、複数の入力信号の少なくとも一部について論理評価を行うステップと、論理評価の結果が真のとき、ダイナミックノードの初期化を停止するステップとを備えている。

(もっと読む)

半導体装置

【課題】回路シミュレーションをすることなくスリープ状態からアクティブ状態への遷移時における、ラッシュカレントの発生を抑える半導体装置を提供する。

【解決手段】半導体装置は、複数のブロックに分割された内部回路と、各々の内部回路と電源線またはグランド線との間にそれぞれ接続されたスイッチ回路と、各々の内部回路と対応する各々のスイッチ回路との接続点に接続された制御信号生成回路とを備える。初段のスイッチ回路は、外部から入力されるスリープ信号によりオン/オフが制御され、2段目以降のスイッチ回路は、それぞれ、前段の制御信号生成回路が前段のスイッチ回路のオン/オフにより対応する接続点の電位の変化を検出して生成する制御信号により、初段のスイッチ回路と同じ状態にオン/オフが制御されることにより、上記課題を解決する。

(もっと読む)

レベルシフト回路

【課題】貫通電流を防止するレベルシフト回路

【解決手段】従来のレベルシフト回路にPMOSトランジスタMP3およびMP4ならびにレベルシフト回路の出力信号をフィードバックするスイッチ制御回路を追加することで、従来回路の問題点であった貫通電流の流れる時間を減らし、消費電力を低減させ、かつ実装面積の増加を抑えながら高速動作させる。

(もっと読む)

半導体装置、データ伝送システム、及び半導体装置の制御方法

【課題】小振幅信号を高速に増幅して出力し、かつ、消費電力の少ないアンプを備える半導体装置を提供する。

【解決手段】クロックに同期してデータが更新される小振幅信号を受信するアンプ部と、アンプ部の出力に接続された出力部と、を備え、アンプ部はクロックに同期して小振幅信号の論理レベルが遷移しうるタイミングで電流源の電流を増加し、遷移しないタイミングで電流を減少する。出力部はクロックに同期してアンプ部の出力データの論理レベルが遷移しうるタイミングで出力インピーダンスを低下させて高速に負荷を駆動すると共に、論理レベルが遷移しないタイミングで出力インピーダンスを増加させて貫通電流が流れることを防ぐ。

(もっと読む)

内部電圧発生器

【課題】プルアップ駆動部とプルダウン駆動部が同時に駆動される期間を相殺して、常に一定の内部電圧を維持することができる内部電圧発生器を提供すること。

【解決手段】本発明の内部電圧発生器は、基準電圧を用いて内部電圧のレベルを検出する検出部210と、該検出部の出力信号に応じて、前記内部電圧を出力する内部電圧端を放電駆動する第1の駆動部220と、該第1の駆動部に流れる放電電流を感知する電流感知部230と、該電流感知部の出力信号に応じて、前記内部電圧端を充電駆動する第2の駆動部240とを備える。

(もっと読む)

半導体装置

【課題】スタンバイ時のサブスレッショルドリーク電流およびゲートリーク電流を低減させ、スタンバイモードからの復帰時の貫通電流の発生を防ぐことのできる半導体装置を提供する。

【解決手段】クロックゲート信号Gにより出力レベルが固定されるNANDゲート1およびインバータ2〜6と高電位電源線VDDとの間に接続された高閾値のPMOSトランジスタPH1〜PH6、および低電位電源線VSSとの間に接続された高閾値のNMOSトランジスタNH1〜NH6のスイッチングを、スタンバイ制御信号SB1、SB2およびそれぞれの反転信号SB1N、SB2Nで制御する。

(もっと読む)

入力バッファ回路

【課題】貫通電流の量を低減し、応答速度の低下を抑制する。

【解決手段】差動入力回路と、電源VDDと差動入力回路の一方の電源との間を接続し、差動入力回路の動作状態と非動作状態とを切り替え可能とするPMOSトランジスタ20と、PMOSトランジスタ20に並列に接続され、ゲートに差動入力回路の出力信号を入力するPMOSトランジスタ14と、を備える。PMOSトランジスタ20のサイズは、PMOSトランジスタ14のサイズよりも小さい。接地と差動入力回路の他方の電源との間を接続し、差動入力回路の動作状態と非動作状態とを切り替え可能とするNMOSトランジスタ19と、NMOSトランジスタ19に並列に接続され、ゲートに差動入力回路の出力信号を入力するNMOSトランジスタ13と、をさらに備える。NMOSトランジスタ19のサイズは、NMOSトランジスタ13のサイズよりも小さい。

(もっと読む)

半導体集積回路装置

【課題】電源電圧を制御する回路ブロックを流用する場合に貫通電流を防止するインターフェースの再設計の手間を緩和する。

【解決手段】第1チップ(CHP1)は、第1及び第2ノード、電源電圧が供給される第1回路ブロック、第3と第2ノード間にソース・ドレイン経路を有する第1MOSトランジスタ、そのオン/オフを制御する第1制御回路、及び電源電圧と共に第1回路ブロックの出力が入力される第1変換回路を備える。第2チップ(CHP2)は、第4及び第5ノード、電源電圧と共に第1変換回路の出力が入力される第2変換回路を備える。第1制御回路は、第1MOSトランジスタがオンの場合、第1状態の第1制御信号を第1変換回路に出力し、第1変換回路は第1回路ブロックの信号を第2変換回路に出力する。第1MOSトランジスタがオフの場合、第2状態の第1制御信号を第1変換回路に出力し、第1変換回路はその出力を第1又は第2ノードの電位に制御する。

(もっと読む)

レベルシフト回路、表示装置および電子機器

【課題】貫通電流を抑えつつ大振幅のレベル変換を実現可能なインバータ型のレベルシフト回路を提供する。

【解決手段】インバータ型のレベルシフト回路10において、初段のCMOSインバータ回路11のnチャネルトランジスタ112のサイズを、pチャネルトランジスタ111のサイズのa倍(例えば、100倍)以上の極端なサイズ差に設定する。このサイズ比により、貫通電流を抑えつつ、例えば0−3V振幅から0−12V振幅にレベル変換する場合のような大振幅のレベル変換を実現する。

(もっと読む)

半導体チップ及び半導体チップを搭載する半導体装置

【課題】入力回路を、所望の期間にわたって、常時活性化させること。

【解決手段】本発明に係る半導体チップ1は、複数のパッドと、パッドと電気的に接続される入力回路又は出力回路と、外部回路又は内部回路からの信号の読み出しを制御するリードアクセス信号を出力する主制御部と、リードアクセス信号に基づいて、外部回路又は内部回路から信号が印加されるパッドと電気的に接続される入力回路又は出力回路の活性化を制御する活性化制御部と、を備える。

(もっと読む)

レベルシフト回路、表示装置および電子機器

【課題】貫通電流を抑えることができるとともに、トランジェントの制御の自由度が高いレベルシフト回路を提供する。

【解決手段】第1,第2のトランジスタ(111,112/121,122)およびこれらのトランジスタ間に接続された第3のトランジスタ(113/123)を有する第1,第2の回路部11,12は、第1電源vddと第2電源vssとの間に並列に接続されている。第1の回路部11の第3のトランジスタ113のゲート電極は第2の回路部12の出力ノードに、第2の回路部12の第3のトランジスタ123のゲート電極は第1の回路部11の出力ノードにそれぞれ接続されている。このレベルシフト回路において、第2の回路部12の入力ノードNin2に入力される第1振幅のパルス信号in1を第2振幅のパルス信号outにレベルシフトする際に、第1の回路部11の入力ノードNin1の電圧値によって第2振幅のパルス信号outのトランジェントを制御する。

(もっと読む)

スイッチング出力回路およびスイッチング電源

【課題】貫通電流を防止する。

【解決手段】ハイサイドトランジスタ16およびローサイドトランジスタ18それぞれのゲート電極30、40は、異なる位置に設けられた駆動用コンタクト32(42)と検出用コンタクト34(44)を介して信号を入出力可能に構成される。ハイサイドドライバ22は、制御信号S1が第1レベルであり、かつローサイドトランジスタ18側の検出用コンタクト44の信号SLがローレベルのとき、ハイサイドトランジスタ16側の駆動用コンタクト32にローレベルを印加する。ローサイドドライバ24は、制御信号S1が第2レベルであり、かつハイサイドトランジスタ16側の検出用コンタクト34の信号SHがハイレベルのとき、ローサイドトランジスタ18側の駆動用コンタクト32にハイレベルを印加する。

(もっと読む)

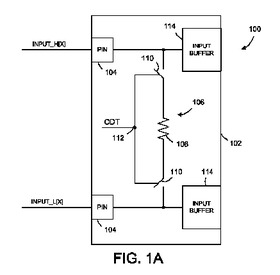

差動式オンライン終端

メモリデバイス及びシステムには、信号線に対するオンチップ終端が組み込まれている。メモリデバイスは、集積回路チップを備える。該集積回路チップは、1対の入力信号を提供する1対の入力信号ピンと、該入力信号ピンの対間に結合されるオンチップ終端回路とを備える。該オンチップ終端回路は、前記1対の入力信号を差動式に終端する。  (もっと読む)

(もっと読む)

21 - 40 / 133

[ Back to top ]