Fターム[5J056BB19]の内容

Fターム[5J056BB19]に分類される特許

61 - 80 / 133

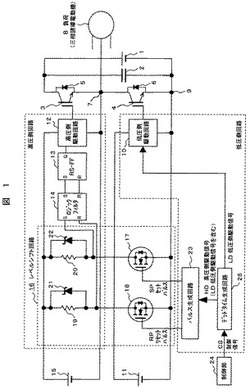

半導体素子駆動装置、電力変換装置、及びモータ駆動装置、並びに半導体素子駆動方法、電力変換方法、及びモータ駆動方法

【課題】直列接続IGBT3,4の接続点7のdV/dtによる誤動作発生時に、上下アーム短絡などの事故を回避できる高信頼性IGBT駆動装置を提供する。

【解決手段】高低圧側IGBT3,4は、デッドタイムを挟み相補的にオン/オフ制御される。これらデッドタイム期間中に、高圧側IGBT3をオフさせるリセットパルスRSを、例えば、次のような要領で発生させる。(1)低圧側IGBT4のオン指令LDの直前に、(2)低圧側IGBT4のオン指令LDの直前から、このオン指令LDと重なる期間tdをもつように、(3)デッドタイムDT期間中、継続して、(4)低圧側IGBT4がオンとなる直前のデッドタイム期間中、継続して、(5)高圧側IGBT3のオン状態を観測したとき、低圧側IGBTのオン指令を無効とするように、リセットパルスを生成する。

(もっと読む)

インバータ回路

【課題】貫通電流の発生を回避すると共に、入力信号に対する出力信号の遅延やデューティ比の変化を生じないようにする。

【解決手段】ゲート電圧制御回路103は、入力信号に対して第1の閾値電圧を基準として反転動作を行うインバータ素子5の出力信号と、入力信号に基づいて、ゲート電圧切替回路102の動作を制御する切替制御信号Vcntと、出力PMOSトランジスタ1、出力NMOSトランジスタ2のゲートに印加されるゲート電圧Vgateを、生成、出力するよう構成されており、終段回路102には、インバータ素子5の出力、又は、ゲート電圧Vgateがゲート電圧切替回路102により選択されて印加されて、出力PMOSトランジスタ1及び出力NMOSトランジスタ2の同時導通状態の回避と共に、入力信号に対して遅延やデューティ比の変化のない出力電圧outputが得られるようになっている。

(もっと読む)

電圧レベルシフト機能を有するインタフェース回路、半導体集積回路、表示装置

【課題】貫通電流が流れ難くより大きな振幅のパルス出力が可能なレベル変換部にする。

【解決手段】トランジスタ302p,304pで構成されたカレントミラー構成の負荷に対して入力トランジスタ312p,314pを設ける。ブートストラップ用の容量素子322(容量値Cap)を、入力トランジスタ312pのゲートとソースとの間に接続し、入力トランジスタ312pとともにブートストラップ回路320を構成する。トランジスタ324pを、基準電位Vref の入力端と入力トランジスタ312pのゲートとの間に接続し、トランジスタ312p,324pのゲートにはパルス信号inを供給する。容量素子322によるブートストラップ動作を利用して、入力トランジスタ312pの抵抗値制御(オン/オフ制御)をしっかりとできるようにすることで、出力OUT の振幅を(Vdd−Vref )/|Vss1−Vref |程度にすることができる。

(もっと読む)

出力回路

【課題】チップサイズの増加を抑え、かつ高速動作が可能な出力回路を得る。

【解決手段】PMOSトランジスタM1のゲート電圧PHが入力された、しきい値電圧にヒステリシスを有するインバータ5と、NMOSトランジスタM2のゲート電圧NLが入力された、しきい値電圧にヒステリシスを有するインバータ8とを備え、PMOSトランジスタM1のゲートには、入力信号Sinと、インバータ8の出力信号の信号レベルを反転させた信号とのOR論理信号を入力し、NMOSトランジスタM2のゲートには、入力信号Sinと、インバータ5の出力信号の信号レベルを反転させた信号とのAND論理信号を入力するようにした。

(もっと読む)

集積回路装置のデータバス電荷共有技術

【課題】多数の内部データバスを有する集積回路装置の高周波数でのデータバスの切り替えによる消費電力を低減する。

【解決手段】集積回路装置のデータバス電荷共有技術は、特に開示される例示的実施態様におけるそれぞれ約0,9倍の一の供給電圧VCCおよび0.1倍のVCCである低電圧VEQ1およびVEQ2を生成する2つの電圧レギュレータを用いて実施され得る。一組の信号は、VCCとVEQ1との間を切り替え、第2組の信号は、VEQ2と0Vとの間を切り替える。二組の信号間の電荷共有は、電圧レギュレータのユニークな構成により実現する。

(もっと読む)

レベルシフト回路

【課題】異なる電源で動作する複数の回路部への電源の供給状態に拘らず確実に貫通電流の経路を遮断することができるレベルシフト回路を提供する。

【解決手段】電源電圧VDD1で動作する入力回路部8と、電源電圧VDD2で動作する出力回路部9と、を備え、入力回路部8に、電源電圧VDD1で動作し、出力回路部9から入力される制御信号を変換するインバータ回路13を設け、当該インバータ回路13の出力を、出力回路部9のVDD2で動作するインバータ回路14の出力と共に入力回路部8の制御信号として用いる。

(もっと読む)

半導体装置

【課題】従来の半導体装置では、NMOSトランジスタを介して流れる貫通電流によって、前段論理回路内部のトランジスタが劣化あるいは破壊される虞があった。

【解決手段】半導体装置は、第1の電源電圧に基づいて、データ信号を伝達するプリバッファと、第1の電源電圧とは異なる第2の電源電圧に基づいて、前記プリバッファによって伝達されたデータ信号を増幅して出力するメインバッファと、スイッチ制御信号に基づいて、前記プリバッファと前記メインバッファとの導通状態を制御するスイッチ部と、前記スイッチ制御信号の生成と、前記スイッチ制御信号の論理レベルの遷移に応じて、前記プリバッファの出力レベルを接地電位にするように前記プリバッファを制御する前記データ信号の生成とを行う制御回路とを有する。

(もっと読む)

半導体集積回路

【課題】電源電圧を制御する回路ブロックを流用する場合に貫通電流を防止するためのインターフェースの再設計の手間を緩和する。

【解決手段】第1ノードと第2ノードとの間の電位差である第1電圧の第1電源が供給される第1回路ブロック(BLK2)、及び第1回路ブロックの出力を第1回路ブロックの外部に送信するための第1変換回路(MIO4)を備える第1チップ(CHP1)と、第3ノードと第4ノードとの間の電位差である第2電圧の第2電源が供給される第2回路ブロック、及び第1変換回路からの出力を前記第2電圧に変換して第2回路ブロックに送信するための第2変換回路とを備える第2チップ(CHP2)とを有する。前記第1回路ブロックは、第1電源が供給される第1モードと第1電源が供給されない第2モードとを有し、第1変換回路は、第1回路ブロックが第2モードの場合は、第1ノード又は第2ノードの電位を前記第2変換回路に送信する。

(もっと読む)

電圧レベル変換回路

【課題】消費電流を低減した電圧レベル変換回路を提供する。

【解決手段】第1電圧の入力信号を入力する入力端子1と、第2電圧の出力信号を出力する出力端子2と、入力端子1と接続される第1のレベルシフトユニット3と、第1のレベルシフトユニット3の出力信号が入力されるインバータ13と、入力端子1と接続されるインバータ10と、インバータ10の出力信号が入力される第2のレベルシフトユニット4と、ドレインが共通に構成されたPMOSトランジスタM23及びNMOSトランジスタM24と、を備え、PMOSトランジスタM23及びNMOSトランジスタM24のゲートをインバータ13及び第2のレベルシフトユニット4に接続し、PMOSトランジスタM23及びNMOSトランジスタM24のドレインを出力端子2に接続した。

(もっと読む)

レベルシフタ

【課題】レベルシフタにおける貫通電流を防止する。

【解決手段】内部ノードn3と接地電位GNDの間に接続されたトランジスタP7,N5によるインバータと、内部ノードn4と接地電位GNDの間に接続されたトランジスタP8,N6によるインバータで構成される保持回路10を設け、これらのインバータをループ状に接続することにより、ノードn1,n2の信号を保持する。これにより、本来相補的である入力信号IN,INBが共にレベル“L”になったときにでも、ノードn1,n2の信号が、その直前のレベルに保持され、トランジスタN3,N4に貫通電流が流れることを防止することができる。

(もっと読む)

入力回路

【課題】入力回路の電源電圧と接地電位との間に流れる貫通電流を改善して、入力回路が設けられた半導体集積回路の消費電流を低減する。

【解決手段】入力回路20は、電源電圧と接地電位との間に接続可能に、一方21に他方25がPMOS25を介して並列接続された2つの抵抗21、22と、入力電圧により制御され一方22に他方27がNMOS26を介して並列接続された2つのNMOS23、24とが直列接続され、その直列接続点の電位をインバータ27を介して出力電圧として出力するとともにインバータ27の出力電位によりPMOS25およびNMOS26が相補的に制御されることによりヒステリシス特性を持たせている。

(もっと読む)

インバータ回路

【課題】CMOSプロセスで形成しても貫通電流を低減し得るインバータ回路を提供する。

【解決手段】インバータ回路10では、電源VddとスイッチングトランジスタTp1のソースとの間にマスク用スイッチングトランジスタTp2が介在し、アースEとスイッチングトランジスタTn1のソースとの間にマスク用スイッチングトランジスタTn2が介在し、これらが同時にオン状態である期間中、これらマスク用スイッチングトランジスタTn2,Tp2のいずれかはオフ状態を維持する。このため、入力端子INに入力される矩形波による電圧が、スイッチングトランジスタTn1の閾値電圧Vtn1を超え、かつスイッチングトランジスタTp1の閾値電圧Vtp1を下回ってMOSトランジスタTp1,Tn1が同時にオン状態になっても、この期間中マスク用スイッチングトランジスタTn2,Tp2のいずれかがオフ状態を維持し電源Vdd−アースE間の貫通電流を阻止する。

(もっと読む)

デッドタイム制御回路

【課題】デッドタイムを広範囲に複数ステップで設定する際、デッドタイムに応じてステップ間隔を変更することを、遅延素子を外付けすることなく、回路規模の小さいICチップで実施することは困難であった。

【解決手段】2つのパルス信号の活性化パルスエッジを遅延させて互いの不活性化パルスエッジと活性化パルスエッジとの間にデッドタイムを付加して並列出力するデッドタイム制御回路10であって、制御信号(DA)に基づいて前記デッドタイムに応じたステップ間隔の複数ステップの遅延時間のいずれかを選択して前記入力したパルス信号の両パルスエッジを遅延させる遅延回路部101a、101bと、前記入力したパルス信号と前記遅延回路部が遅延させたパルス信号とを論理処理して前記活性化パルスエッジを遅延させた信号を生成する信号生成部(論理回路部102a、102b)と、を備える。

(もっと読む)

論理回路

【課題】 間欠動作する論理回路の動作停止時(待機時)のリーク電流を低減し、さらにスイッチング動作時のトランジスタ間の貫通電流を低減する。

【解決手段】 縦積み接続したnMOSトランジスタとpMOSトランジスタを用いて構成される論理回路において、論理回路を構成するnMOSトランジスタおよびpMOSトランジスタのそれぞれが、高電位側に配置したnMOSトランジスタと低電位側に配置したpMOSトランジスタの各ソース端子を接続した複合トランジスタで構成され、複合トランジスタを構成するnMOSトランジスタとpMOSトランジスタの各ゲート端子に、相補的なディジタル信号が入力される構成である。

(もっと読む)

レベルシフタ回路

【課題】貫通電流を低減することができるレベルシフタ回路を提供する。

【解決手段】NMOSトランジスタN2のプルアップ用のNMOSトランジスタN3及びPMOSトランジスタP3を備える。電源ノードVDD2のみに電源電圧が供給されている間では、NMOSトランジスタN2がオンするため、インバータ回路INV3に入力される電位の下降に応じて、インバータ回路INV3が動作し、出力される電位が上昇するため、出力端子14の電位がHレベルで安定する結果、インバータ回路INV3における貫通電流が発生しなくなり、レベルシフタ回路10全体としての貫通電流を低減することができる。

(もっと読む)

インバータ回路および遅延回路

【課題】遅延回路などに適用した場合に、回路規模を小さくでき、貫通電流を防止でき、

かつ、消費電力を低減できるインバータ回路の提供

【解決手段】この発明は、入力信号IN1でオンオフするMOSトランジスタP11と、

入力信号IN2でオンオフするN型のMOSトランジスタN11と、直列接続されるとと

もにゲートとドレインが接続される2つのMOSトランジスタP12、N12とを備えて

いる。MOSトランジスタP11、MOSトランジスタP12、N12、およびMOSト

ランジスタN11は、第1電源VDDと第2電源VSSとの間に直列に接続されている。

MOSトランジスタP11とP12の共通接続部から出力信号OUT1を取り出し、MO

SトランジスタN11とN12の共通接続部から出力信号OUT2を取り出すようになっ

ている。

(もっと読む)

ドライバ回路

【課題】デッドタイムを適切に設定し、貫通電流を防止する。

【解決手段】出力バッファ10は、電源端子102と接地端子GNDの間に直列に接続された、ハイサイドトランジスタM1およびローサイドトランジスタM2を含む。遅延回路12は、信号レベルが、ハイサイドトランジスタM1およびローサイドトランジスタM2のオン、オフに対応づけられて切り替わるパルス信号S0を受ける。遅延回路12は、パルス信号S0に遅延を与えることにより、異なる遅延を有する第1パルス信号S1、第2パルス信号S2を生成する。NAND回路14は、第1パルス信号S1、第2パルス信号S2の否定論理積に応じた信号をハイサイドトランジスタM1のゲートに与える。NOR回路16は、第1パルス信号S1、第2パルス信号S2の否定論理和に応じた信号をローサイドトランジスタM2の他方のゲートに与える。

(もっと読む)

インピーダンス制御回路及び半導体チップ

【課題】簡易な構成で安定したインピーダンス制御を行うことができるインピーダンス制御回路及び半導体チップを提供すること。

【解決手段】本発明にかかるインピーダンスは電流源と、電流源の出力電流が入力されるカレントミラー回路24と、カレントミラー回路24の出力電流が流れされるレプリカバッファ2と、カレントミラー回路24の出力端子の電位とカレントミラー回路24の入力端子の電位とを比較する比較器9と、比較器9の比較結果に基づいて、Pchレプリカバッファ2の抵抗を制御する制御信号を生成する制御信号生成器14とを備えるものである。

(もっと読む)

半導体装置

【課題】 制御信号のタイミングによらず、スタンバイ時の貫通電流を防止できる半導体装置を提供する。

【解決手段】 高位電源線11と低位電源線12との間に接続される第1および第2機能回路セル13、14と、第1機能回路セル13と低位電源線12との間に接続された第1絶縁ゲート電界効果トランジスタM1と、高位電源線11と低位電源線12との間に接続される第2機能回路セル14と高位電源線11との間に接続された第2絶縁ゲート電界効果トランジスタM2と、第1および第2機能回路セル13、14の一方の出力端と、他方の入力端とを接続する配線15とを具備する。

スタンバイ時に、第1機能回路セル13の出力φ2が高電位状態となり、第2機能回路セル14の出力φ3が低電位状態となるように、第1および第2絶縁ゲート電界効果トランジスタM1、M2を駆動し、他方の機能回路セルに流れる貫通電流を抑制する。

(もっと読む)

半導体集積回路

【課題】回路面積の増大を抑制しつつ、貫通電流を防ぐ。

【解決手段】半導体集積回路は、第1の内部電圧で動作する第1の回路ブロック11と、第2の内部電圧で動作し、かつ第1の回路ブロック11の後段に接続され、かつ第1の回路ブロック11から信号が供給される第2の回路ブロック12と、第1の高位側電源電圧を用いて第1の回路ブロック11に第1の内部電圧を供給し、かつ第2の高位側電源電圧を用いて第2の回路ブロック12に第2の内部電圧を供給し、かつ第2の内部電圧が第1の内部電圧を超えないように制御する電圧制御回路13,14とを具備する。

(もっと読む)

61 - 80 / 133

[ Back to top ]