Fターム[5J056CC11]の内容

Fターム[5J056CC11]に分類される特許

1 - 20 / 34

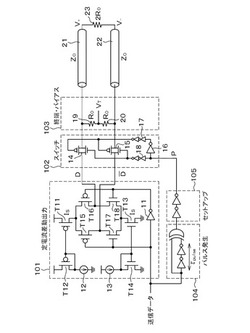

小振幅差動パルス送信回路

【課題】最適の時期に出力電流を流して、それ以外の時期には出力電流を止めることによって省エネ性能に優れた小振幅差動パルス送信回路を提供すること。

【解決手段】定電流を送信データに応じて差動的に出力する定電流差動出力回路101と、前記定電流差動出力回路101の出力を、送信データの値の変化による該出力の過渡現象が収束した後であって次のデータが出力される前における所定期間通過させるスイッチ回路102と、前記スイッチ回路102の出力を所定電位にバイアスするバイアス回路103とを備える小振幅差動パルス送信回路。

(もっと読む)

半導体装置、システム装置、及び信号制御方法

【課題】処理装置の入出力パッドの端子数を低減することができる半導体装置を提供する。

【解決手段】処理装置21のバス制御回路34に含まれる入出力回路は、外部I/F22と接続されるパッドに接続される。入力部は、パッドから入力される信号に応じた入力信号を出力する。この入力信号は、処理回路31に供給される。パッドは、入力部の入力端子に接続され、出力端子は電源電圧VDDを伝達する電源配線に接続されている。入力部は、外部I/F22のバス制御回路44から入力されるHレベルの信号の電圧を出力端子から出力する。従って、電源配線には、外部I/F22から入力されるHレベルの信号による電圧が供給される。

(もっと読む)

クロック生成回路および撮像装置

【課題】シュミットトリガー回路と同様な機能を有し、シュミットトリガー回路と比較して貫通電流を低減する。

【解決手段】インバータ回路INV1は、前段回路の回路閾値よりも低い第1の回路閾値を有し、前段回路から出力された入力クロックが入力され、入力クロックの論理状態および第1の回路閾値に応じた第1の出力信号を出力する。インバータ回路INV2は、前段回路の回路閾値よりも高い第2の回路閾値を有し、前段回路から出力された入力クロックが入力され、入力クロックの論理状態および第2の回路閾値に応じた第2の出力信号を出力する。スイッチ回路SWは、第1の出力信号および第2の出力信号が入力され、第1の出力信号および第2の出力信号の論理状態が、異なる状態から同じ状態に変化したときに、異なる論理状態に対応した第1の電圧および第2の電圧のいずれか一方を出力クロックとして出力する。

(もっと読む)

信号伝達回路及びこれを用いたスイッチ駆動装置

【課題】入力信号をレベルシフトして出力するレベルシフト回路を有しながらも、電源の電圧変動等による誤信号の出力を抑えることが可能となる信号伝達回路を提供する。

【解決手段】第1入力信号および第2入力信号の各々をレベルシフトし、それぞれ第1シフト済み信号および第2シフト済み信号として出力する、レベルシフト回路を備え、レベルシフト回路は、第1入力信号に応じて開閉するスイッチング素子と抵抗を有する第1直列回路、および、第2入力信号に応じて開閉するスイッチング素子と抵抗を有する第2直列回路が、電源と接地端との間において互いに並列に設けられており、第1直列回路上の電圧を第1シフト済み信号として、第2直列回路上の電圧を第2シフト済み信号として、それぞれ出力するようになっており、接地端から第1直列回路および第2直列回路に向かって逆電流が流れることを防止する、逆流防止部を備えた信号伝達回路とする。

(もっと読む)

受信回路、受信方法及び受信回路を備える通信システム

【課題】従来の受信回路では、耐ノイズ性が低い問題があった。

【解決手段】本発明の受信回路の一態様は、送信回路Txとは異なる電源系において動作する受信回路Rxであって、送信回路Rxが絶縁素子ISOを介して出力する送信信号に基づき生成される受信信号Aの信号レベルの変化に応じて受信データDrx1の論理レベルを切り替える状態保持回路10と、受信データDrx1の論理レベルが切り替わる第1のタイミングから予め設定された第1の期間が経過するまでの期間において、状態保持回路10に受信データDrx1の論理レベルの保持を指示するホールド信号Dを生成する状態保持制御回路20と、を有する。

(もっと読む)

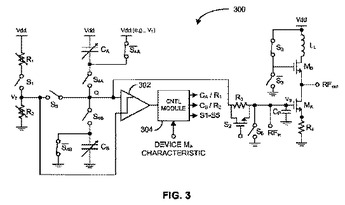

アクティブデバイスをバイアスするシステム及び方法

アクティブデバイスに対するバイアス電圧を発生する装置が開示され、第1の電圧源と、第1の電圧源に応答してチャージを発生するように適応されたキャパシティブエレメントと、アクティブデバイスに対するバイアス電圧を発生するためにチャージを供給するように適応された第1のスイッチングエレメントとを備える。本装置は、アクティブデバイスの1以上の特性に基づいてキャパシティブエレメントをコントロールするように適応されコントローラを備えるかもしれない。コントローラは、リファレンス電圧に基づいて、すなわちアクティブデバイスの1以上の特性に基づいて前記キャパシティブエレメントのキャパシタンスをコントロールかもしれない。  (もっと読む)

(もっと読む)

半導体集積回路

【課題】差動アンプ回路の出力信号の出力をより正確に制御することが可能な半導体集積回路を提供する。

【解決手段】半導体集積回路は、第4のMOSトランジスタと第5のMOSトランジスタとの間の接点の第1の電圧に応じた信号とイネーブル信号とが入力され、イネーブル信号が第1のレベルであり且つ第1の電圧が規定電圧以上の場合に差動アンプ回路の出力信号を出力端子に出力するための第1の信号を出力し、イネーブル信号が第2のレベルまたは第1の電圧が規定電圧未満の場合に第2の信号を出力する演算回路と、差動アンプ回路の出力信号と演算回路が出力した信号とが入力され、第1の信号が入力された場合には、出力信号を出力端子に出力し、第2の信号が入力された場合には、出力端子へ或る論理に固定した信号を出力する出力バッファ回路と、を備える。

(もっと読む)

レベルシフト回路

【課題】外的要因により発生するコンデンサの充放電による信号伝達不良を防止して、確実な信号伝達を行うレベルシフト回路。

【解決手段】第1電圧レベルを第1電圧レベルとは異なる第2電圧レベルに変換するレベルシフト回路であって、第2電圧レベルの論理電圧状態を第1コンデンサC1を介してセットするセットレベル回路20aと、第2電圧レベルの論理状態を第2コンデンサC2を介してリセットするリセットレベル回路20bと、セットレベル回路のセット信号とリセットレベル回路のリセット信号とによりローサイドスイッチQ1に直列に接続されたハイサイドスイッチQ2をオン/オフ駆動する駆動回路24と、第1コンデンサ及び第2コンデンサに流れる電流の内の少なくともいずれか一方を検出する電流検出回路15,16,を備える。

(もっと読む)

レベルシフト回路

【課題】外的要因による誤動作を防止して確実な信号伝達を行うレベルシフト回路。

【解決手段】第1電圧レベルを第1電圧レベルとは異なる第2電圧レベルに変換するレベルシフト回路であって、第2電圧レベルの論理電圧状態をセットするセット信号を送信するセットレベル回路21と、第2電圧レベルの論理電圧状態をリセットするリセット信号を送信するリセットレベル回路22と、第2電圧レベルでセット信号及びリセット信号を検出するための基準値を設定する基準レベル回路C3とを有し、セットレベル回路とリセットレベル回路と基準レベル回路との各々は、それぞれコンデンサC1〜C3を介して第1電圧レベルから第2電圧レベルに信号を伝達する。

(もっと読む)

シュミットトリガ型インバータ

【課題】さらに入力ノイズ耐性を有するシュミットトリガ型インバータを提供すること。

【解決手段】入力側ノードへの供給電圧が増加して第1の基準電圧に達するに従い出力側ノードから出る電圧が比較高電圧レベルから比較低電圧レベルに遷移し、入力側ノードへの供給電圧が減少して第1の基準電圧より低い第2の基準電圧まで減少するに従い出力側ノードから出る電圧が比較低電圧レベルから比較高電圧レベルに遷移するインバータと、インバータの入力側ノードに一方端が接続された第1の抵抗素子と、インバータの入力側ノードに一方端が接続された、該一方端の電圧が上昇するほどに抵抗値が減じる可変抵抗素子と、可変抵抗素子の他方端に一方端が接続された第2の抵抗素子と、ドレインが第2の抵抗素子の他方端に接続され、ゲートがインバータの出力側ノードに接続され、ソースが接地電位に接続されたnチャネルMOSトランジスタとを具備する。

(もっと読む)

高信号レベル対応入出力回路

インターフェース入力(図2:220)は、ホスト回路の電子構成要素が確実に扱える最大信号レベルよりも高い入力信号レベル(padloc)を受け取るように適合された入力回路(図10:221)を持つ。この入力回路(図10:221)は、入力信号(padloc)のレベルを所望の信号レベルにシフトする。キーパー回路(キーパー:プルアップ1011;プルダウン1012)は、入力回路に結合され、入力信号レベル(padloc)に合致するシフトされた信号(lvl_dn_int)のトリガレベルを維持する。  (もっと読む)

(もっと読む)

ラダー抵抗回路、基準電圧生成回路、ドライバ、電気光学装置及び電子機器

【課題】高精度な抵抗分割を小規模な回路面積で実現できるラダー抵抗回路、基準電圧生成回路、ドライバ、電気光学装置及び電子機器を提供すること。

【解決手段】ラダー抵抗回路は、複数の抵抗ユニットRA1〜RAmn(m、nは2以上の整数)と複数の選択ユニットSLA1〜SLAmnを含む。直列に接続された抵抗ユニットRA1〜RAnは方向D1に沿って配置され、方向D1の反対方向を方向D3とする場合に、直列に接続された抵抗ユニットRAn+1〜RA2nは方向D3に沿って配置される。方向D1に直交する方向を方向D2とする場合に、抵抗ユニットRAn+1は抵抗ユニットRAnの方向D2に配置される。選択ユニットSLAiは、抵抗ユニットRAiの方向D2に配置され、抵抗ユニットRAiに対応するタップに接続される。

(もっと読む)

電気回路、電気光学装置、電子機器、および電気回路の駆動方法

【課題】ヒステリシス特性を示すインバータ回路の構成を簡素化しながら消費電力を低減する。

【解決手段】インバータ回路Q1は、Pチャネル型のトランジスタTR1とNチャネル型のトランジスタTR2とで構成される。トランジスタTR1およびトランジスタTR2の各々のバックゲートには閾値制御信号C1が供給される。閾値制御信号C1は、インバータ回路Q1からの出力信号SOUT1のレベルが低下し始める時点にてローレベルに設定されるとともに当該時点の経過後にハイレベルに設定され、かつ、出力信号SOUT1のレベルが上昇し始める時点にてハイレベルに設定されるとともに当該時点の経過後にローレベルに変化する。

(もっと読む)

電気回路、電気光学装置、電子機器、および電気回路の駆動方法

【課題】ヒステリシス特性を示すインバータ回路の構成を簡素化しながら消費電力を低減する。

【解決手段】インバータ回路Q1は、Pチャネル型のトランジスタTR1と、Nチャネル型のトランジスタTR2とで構成される。信号供給点R1とトランジスタTR1のチャネルコンタクト領域Aとの間には容量C1が介在し、信号供給点R1とトランジスタTR2のチャネルコンタクト領域Aとの間には容量C2が介在する。信号供給点R1には閾値制御信号SC1が供給される。閾値制御信号SC1は、インバータ回路Q1からの出力信号SOUT1のレベルが低下し始める時点にてローレベルに設定されるとともに当該時点の経過後にハイレベルに設定され、かつ、出力信号SOUT1のレベルが上昇し始める時点にてハイレベルに設定されるとともに当該時点の経過後にローレベルに変化する。

(もっと読む)

シュミット回路

【課題】入力信号EAの立ち上がり時の回路しきい値電圧VIH及び立ち下がり時の回路しきい値電圧VILのDC仕様がVDDとVSSとの中心電圧近傍からVSS側又はVDD側に極端に偏っている場合であっても、入力信号EAの立ち上がり時の回路しきい値電圧VIH及び立ち下がり時の回路しきい値電圧VILのDC仕様を満足させることができるシュミット回路を提供する。

【解決手段】PMOSトランジスタ26、27とNMOSトランジスタ28からなる入力部25に対して、PMOSトランジスタ32からなる第1のヒステリシス設定部31と、NOR回路34とPMOSトランジスタ35からなる第2のヒステリシス設定部33とを設ける。

(もっと読む)

シュミットトリガ回路

【課題】本発明は、単純な構成のシュミットトリガ回路を提供することを目的とする。

【解決手段】シュミットトリガ回路は、第1の入力及び第2の入力が双方ともに第1の入力レベルの時に出力が第1の出力レベルであり、第1の入力及び第2の入力が双方ともに第2の入力レベルの時に出力が第2の出力レベルであり、第1の入力及び第2の入力の一方が第1の入力レベルで他方が第2の入力レベルである時に出力が第1の出力レベルである2入力1出力の論理回路と、共通の入力信号を第1の入力及び第2の入力に入力する際に第1の入力への入力タイミングと第2の入力への入力タイミングとを異ならせる遅延素子とを含み、論理回路の第1の入力に対する第1の閾値電圧と第2の入力に対する第2の閾値電圧とが互いに異なるように構成されていることを特徴とする。

(もっと読む)

出力回路

【課題】チップサイズの増加を抑え、かつ高速動作が可能な出力回路を得る。

【解決手段】PMOSトランジスタM1のゲート電圧PHが入力された、しきい値電圧にヒステリシスを有するインバータ5と、NMOSトランジスタM2のゲート電圧NLが入力された、しきい値電圧にヒステリシスを有するインバータ8とを備え、PMOSトランジスタM1のゲートには、入力信号Sinと、インバータ8の出力信号の信号レベルを反転させた信号とのOR論理信号を入力し、NMOSトランジスタM2のゲートには、入力信号Sinと、インバータ5の出力信号の信号レベルを反転させた信号とのAND論理信号を入力するようにした。

(もっと読む)

入力回路

【課題】入力回路の電源電圧と接地電位との間に流れる貫通電流を改善して、入力回路が設けられた半導体集積回路の消費電流を低減する。

【解決手段】入力回路20は、電源電圧と接地電位との間に接続可能に、一方21に他方25がPMOS25を介して並列接続された2つの抵抗21、22と、入力電圧により制御され一方22に他方27がNMOS26を介して並列接続された2つのNMOS23、24とが直列接続され、その直列接続点の電位をインバータ27を介して出力電圧として出力するとともにインバータ27の出力電位によりPMOS25およびNMOS26が相補的に制御されることによりヒステリシス特性を持たせている。

(もっと読む)

入力回路

【課題】入力レベルに対してヒステリシス特性を持たせる。

【解決手段】第1トランジスタM1は、ソースが接地端子P2に接続され、ゲートに入力デジタル信号S1が入力される。第2トランジスタM2は、ソースが電源端子P1に接続され、そのドレインが第1トランジスタM1のドレインに接続される。第2トランジスタM2はデプレッション型で構成する。第1インバータ12は、第1トランジスタM1、第2トランジスタM2の接続点P3、すなわちドレイン電位Vxを反転し、第2トランジスタM2のゲートに出力する。入力回路10は、接続点P3のドレイン電位Vxに応じたレベルを出力する。

(もっと読む)

高ヒステリシス幅入力回路

【課題】従来のヒステリシス入力回路は等価的にP型MOSFETとN型MOSFETのインバータ回路のβ比を変えて、ロジックレベルのヒステリシスを作っていたが、この方式では電源電圧が低下するとヒステリシス幅が極端に小さくなった。また、電源電圧の広範囲の変動に対してヒステリシス幅を確保することは難しかった。また、ロジックレベルを形成するのにP型とN型MOSFETを用いるので形状比の設定にやや無理があり、また製造工程でのバラツキの影響を受けやすかった。

【解決手段】入力回路2個と正極の電源にP型、N型MOSFET、負極の電源にN型、P型MOSFETと、及び前状態を記憶するラッチ回路を設け、前状態により、前記各MOSFETをオン・オフすることにより、ヒステリシス特性を得る。電圧特性が異なるMOSFETを使い分けることにより、前述の課題が解消できた。

(もっと読む)

1 - 20 / 34

[ Back to top ]