Fターム[5J056CC20]の内容

Fターム[5J056CC20]に分類される特許

1 - 10 / 10

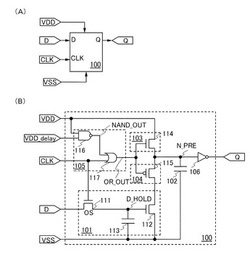

半導体記憶装置

【課題】電源電圧の停止及び復帰を行う構成において、外部回路より半導体記憶装置を制御するための信号数を削減する。

【解決手段】酸化物半導体を半導体層に有するトランジスタを有する記憶回路と、記憶回路に保持されたデータを読み出すための電荷を蓄積する容量素子と、容量素子への電荷の蓄積を制御するための電荷蓄積回路と、データの読み出し状態を制御するデータ検出回路と、電源電圧が供給された直後の期間において、電源電圧の信号と電源電圧を遅延させた信号とにより、電荷蓄積回路による容量素子への電荷の蓄積をさせるための信号を生成するタイミング制御回路と、容量素子の一方の電極の電位を反転して出力するインバータ回路と、を有する構成とする。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えることの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】5Tr1Cで構成されるインバータ回路1において、トランジスタT2のゲートと高電圧線L3との間に接続されたトランジスタT4,T5と、トランジスタT2のゲートと低電圧線L1との間に接続されたトランジスタT3とのオンオフ動作により、全期間に渡ってトランジスタT1,T2が同時にオンしないようになっている。

(もっと読む)

信号処理回路、及び信号処理回路の駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた信号処理回路の提供を目的の一つとする。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積及び放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、酸化物半導体をチャネル形成領域に含むトランジスタを用いる。そして、上記記憶素子を、信号処理回路が有する、レジスタやキャッシュメモリなどの記憶装置に用いる。

(もっと読む)

予備充電ロジックにおけるエラー検出

【課題】内蔵のエラー検出回路を持ったドミノロジックのような予備充電されたロジックを含む集積回路を提供すること。

【解決手段】推論ノード22と検査ノード24とを含むドミノロジックを持つ集積回路2が提供される。予備充電回路36は、推論ノードと検査ノードの両方を予備充電する。論理回路26は、入力信号値に基づいて推論ノードと検査ノードとのため放電路を提供する。評価制御回路28,30は、先ず推論ノードを論理回路に結合し、次いで検査ノードを論理回路に結合するので、もし論理回路26への入力信号が適切な値を持つなら、これらは放電されうる。推論ノードと検査ノードとが両方とも放電されるか又は両方とも放電されないかのいずれでもない場合に、エラー検出回路32はエラーを検出する。

(もっと読む)

ドライバ装置

【課題】UVLO機能を内蔵したドライバ装置を提供する。

【解決手段】電源に接続された第1のスイッチ素子と、前記第1のスイッチ素子と直列接続された第2と、第3と、前記第3のスイッチ素子と並列接続された第4のスイッチ素子と、一端が前記第3及び第4のスイッチ素子に接続され、他端が前記第1のスイッチ素子の制御電極に接続された第1の抵抗と、前記第1の抵抗を介して前記第3のスイッチ素子の負荷となるカレントミラーと、前記カレントミラーに電流を流す放電回路と、外部から入力信号を受けて、前記第2と第3のスイッチ素子を介して前記第1のスイッチ素子と、を交互にオン、オフするように制御し、かつ、前記放電回路及び前記第4のスイッチ素子を、前記電源が立ち上がるときにオンさせて前記カレントミラーに電流を流すことにより、電源が立ち上がった後は前記第4のスイッチ素子をオフする制御回路を備える。

(もっと読む)

電子回路のブートストラップポイント電圧を低下する方法、及びその方法を用いた装置

【課題】電子回路のブートストラップポイントの電圧を低下させる方法とそれを用いた装置を提供する。

【解決手段】シフトレジスタ回路等の電子回路において、ブートストラップポイント電圧レベルを低下させる放電装置を提供する。この回路において、第1トランジスタは、導通の際、入力パルスを受信し、入力パルスを第2トランジスタのゲート端に伝送して、第二トランジスタを導通状態にする。このゲート端がいわゆるブートストラップポイントである。入力パルスを受信した時、出力パルスが第2トランジスタのドレイン/ソース端に生成される。出力パルスの時間周期において、第1トランジスタは非導通態で、且つ、ブートストラップポイントは高電圧レベルにあり、第1トランジスタに対し電圧を印加する。放電回路は、少なくとも一つのトランジスタから構成され、ブートストラップポイントに接続されて、出力パルス周期内の電圧レベルを低下させる。

(もっと読む)

容量性負荷の電流消耗を下げる構造及びその方法

【課題】駆動電流を節約し、負荷の電流消耗を下げ、電力を節約できる容量性負荷の電流消耗を下げる構造及びその方法を提供する。

【解決手段】容量性負荷の電流消耗を下げる構造は、駆動部品の出力端に対して、電圧信号を容量性負荷へ伝送する。そのうち、保存容量は、出力端と容量性負荷の間に設置し、切換スイッチは保存容量に切り換えて、出力端と容量性負荷に連接する。また容量性負荷の電流消耗を下げる方法は、出力端の電圧信号が転換した時、切換スイッチは先ず保存容量と容量性負荷の負荷容量を同等化する。同等化が完了した後、切換スイッチを切り換えて出力端と容量性負荷を連接し、容量性負荷に対して充電/放電を行う。

(もっと読む)

波形改善回路

【課題】コンデンサに充電された電荷の放電タイミングを最適にし、高速信号に対応できるようにした波形改善回路を提供する。

【解決手段】信号線4に伝送されるデジタルの信号Stの波形を改善する波形改善回路1は、信号Stのレベルが所定値を超えたことをレベル検出回路11Aが検出すると、その出力電圧Vdに基づいてスイッチ回路12Aが導通状態になり、電源電圧VBを充電回路13Aのコンデンサ131に印加してコンデンサ131を充電する。信号Stの電圧レベルが、コンデンサ131の充電電圧Vcよりも低くなったタイミングでコンデンサ131から信号線4へ、放電回路14Aのダイオード141を介して放電が行われ、アンダーシュートが改善される。

(もっと読む)

表示装置及びその制御方法

【課題】入力信号のLowレベルと出力信号のLowレベルが異なり、かつ入力信号のHiレベルと出力信号のHiレベルが異なる場合でも、貫通電流を充分抑えることが可能な同じ導電型のMOSトランジスタで構成される電圧レベル変換器を備えた表示装置を得る。

【解決手段】表示装置の抵抗容量負荷RL,CLを駆動する電圧レベル変換器が、容量C

PA、NMOS1、容量CB及びNMOS3とからなるチャージ回路6と、NMOS2、

NMOS4及びNMOS5とからなるディスチャージ回路7と、このディスチャージ回路

7の前段に設けたリセット信号生成回路RSTとで構成される。このリセット信号生成回

路RSTには、入力パルスVINと逆相をなす信号/VINが入力され、その出力を、N

MOS2、NMOS4及びNMOS5のゲート端子に供給することで、確実に、ディスチ

ャージ回路7をON,OFFさせる。

(もっと読む)

レベルシフタ回路及びそれを用いた表示素子駆動回路

【課題】回路規模の小さなレベルシフタ回路を実現する。

【解決手段】Pチャネル型のMOSトランジスタMP1を制御信号CTL1で、Nチャネル型のMOSトランジスタMN1を制御信号CTL2で、それぞれ制御する。制御信号CTL1と制御信号CTL2とは互いに独立している。制御信号CTL2を、データ信号DATA及び制御信号CTL3を入力とするNOR回路2により生成する。第1の電位及びGND電位をサンプリングする負荷容量C1を、MOSトランジスタMP2・MN2のゲート容量で構成する。

(もっと読む)

1 - 10 / 10

[ Back to top ]