Fターム[5J056DD39]の内容

論理回路 (30,215) | 構成要素(素子) (5,667) | トランジスタ(UJT、IGBT他) (4,294) | トランジスタの組合せ (2,266) | バイポーラトランジスタとFETの組合せ (147) | FETはP型とN型の組合せ (78)

Fターム[5J056DD39]の下位に属するFターム

FETは相補動作するもの、COMS (52)

Fターム[5J056DD39]に分類される特許

1 - 20 / 26

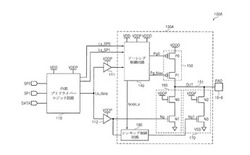

出力バッファ回路の動作方法、その動作方法を用いる出力バッファ回路、その出力バッファ回路を含むシステムオンチップ、及びその出力バッファ回路を含む携帯用データ処理装置。

【課題】 供給電圧または動作電圧に無関係に信頼性を保証可能な出力バッファ回路の動作方法を提供する。

【解決手段】 出力バッファ回路130Aのソーシング制御回路140は、DCレベルを指示する指示信号に基づいて第1ソーシング制御信号Pg0を生成する。ソーシング制御回路140は、指示信号に基づいて第2ソーシング制御信号Pg_biasを生成する。ソーシング回路150は、第1ソーシング制御信号Pg0と第2ソーシング制御信号Pg_biasとに応じて第1電圧VDDOを出力端子151に供給する。第1シンキング回路160は、第2バッファ112から出力されたデータNgのレベルに基づいて出力端子151に接地電圧VSSを供給する。これにより、メインドライバーとして使われるPMOSトランジスタP0、P1のゲート酸化物の信頼性を保証しながら、高速で出力データをバッファリングすることができる。

(もっと読む)

レベルシフト回路

【課題】占有面積が小さく、温度変化や素子のバラツキの影響を受け難く、さらに、ノイズを低減することで高品位のレベルシフトを実現することができるレベルシフト回路を提供する。

【解決手段】レベルシフト回路1は、主に、第1の信号(VIN)をレベルシフトして第2の信号(Vm)を出力するレベルシフト部10と、pMOSトランジスタ32aとnMOSトランジスタ32bを含み、第2の信号を反転させた第3の信号(S1)を出力するCMOSインバータ回路部32、偶数個のインバータ素子(第1のインバータ33a〜第mのインバータ33m)を含み、第3の信号を遅延させた第4の信号(S3)を生成する遅延回路部33、論理素子を含み、第3の信号及び第4の信号が入力して第5の信号(S5)を出力する論理回路部34、及び第4の信号と第5の信号が入力するD−FF素子35、を含む出力バッファ部30と、を備える。

(もっと読む)

出力回路

【課題】2つの出力信号間のタイミングのずれを低減すること。

【解決手段】入力信号IN,XINはトランジスタM1,M2のゲートに供給される。トランジスタM1のドレインはトランジスタM3のドレインとトランジスタM4のゲートに接続され、トランジスタM2のドレインはトランジスタM3のゲートとトランジスタM4のドレインに接続される。また、トランジスタM1,M2のドレインは差動対のトランジスタM11,M12のゲートに接続される。トランジスタM3,M4のソースには、ゲートにバイアス電圧VBが供給されるトランジスタM5が接続される。トランジスタM11,M12のソースには、ゲートにバイアス電圧VBが供給されるトランジスタM13が接続される。

(もっと読む)

レベルシフト回路

【課題】出力電圧の立ち上がりの遅延時間と立ち下がりの遅延時間との差異を低減することが可能なレベルシフト回路を提供する。

【解決手段】出力電圧の立ち上がりの遅延時間と出力電圧の立ち下がりの遅延時間とが互いに異なるレベルシフト部F1、F2が複数段接続されている。そして、前段のレベルシフト部F1の出力電圧の立ち下がりの遅延時間を後段のレベルシフト部F2の出力電圧の立ち上がりの遅延時間で補償し、前段のレベルシフト部F1の出力電圧の立ち上がりの遅延時間を後段のレベルシフト部F2の出力電圧の立ち下がりの遅延時間で補償する。

(もっと読む)

半導体集積回路

【課題】SOI型の半導体集積回路において電源遮断時の低消費電力及び電源供給時の動作性能向上に資することができる電源遮断制御を可能にする。

【解決手段】本発明に係る半導体集積回路は、第1電源スイッチと、前記第1電源スイッチに直列接続される論理回路を有する。前記論理回路は、順序回路(FF1,FF2)及び組み合わせ回路(LOG1,LOG2)を含み、前記第1電源スイッチと前記組み合わせ回路との間に第2電源スイッチが接続される。第1モードにおいて前記第1電源スイッチをオフ状態に制御し、前記順序回路及び前記組み合わせ回路を非通電状態にし、第2モードにおいて前記第1電源スイッチをオン状態に維持し且つ前記第2電源スイッチをオフ状態に制御し、前記順序回路を通電状態、前記組み合わせ回路を非通電状態にする電源スイッチ制御回路を有する。

(もっと読む)

加算器

【課題】新たなロジックインメモリ構造を提供する。また、より消費電力の低い信号処理回路を提供する。また、より消費電力の低い電子機器を提供する。

【解決手段】オフ電流の低いトランジスタを用いて記憶素子を構成することで、記憶機能と演算機能を組み合わせた回路を提供する。オフ電流の低いトランジスタを用いることで、オフ電流の低いトランジスタのソースまたはドレインの一方と、他のトランジスタのゲートとの間などに電荷を保持することができる。そのため、オフ電流の低いトランジスタのソース又はドレインの一方と、他のトランジスタのゲートと、の間のノード等を記憶素子として用いることができる。また、加算器の動作に伴うリーク電流を著しく低減することができる。これにより、消費電力の低い信号処理回路を構築することが可能である。

(もっと読む)

リンギング抑制回路

【課題】より簡単な構成で波形歪みのエネルギーを消費させ、リンギングを確実に抑制できるリンギング抑制回路を提供する。

【解決手段】一対の信号線3P,3N間に、NチャネルMOSFET7を接続し、制御回路14は、伝送線路3を介して伝送される差動信号のレベルがハイからローに変化したことを検出すると、NチャネルMOSFET7を一定期間オンさせる。すなわち、差動信号のレベルが遷移する期間にNチャネルMOSFET7が導通することで信号線3P,3N間のインピーダンスを大きく低下させ、差動信号波形の歪みエネルギーを吸収させてリンギングの発生を確実に抑制する。

(もっと読む)

半導体集積回路

【課題】不良回路ブロックを特定する時間を短くでき、また、各回路ブロックの信頼性加速試験での特性劣化を精度良く測定できる半導体集積回路を提供することを目的とする。

【解決手段】複数の回路ブロックB1、B2、・・・Bnと、複数の回路ブロックに対応し、回路ブロックと電源端子2との接続を制御する複数のスイッチ回路Sa1、Sa2、・・・Sanと、複数のスイッチ回路に対応し、スイッチ回路へ回路ブロック選択信号を出力する複数のフリップフロップ回路DFF1、DFF2、・・・DFFnとを備え、複数のフリップフロップ回路は、シフトレジスタ回路を構成し、外部信号の入力に基づいて、2以上のスイッチ回路を選択して回路ブロック選択信号を出力し、当該回路ブロック選択信号を入力された2以上のスイッチ回路は、当該2以上のスイッチ回路それぞれに対応する回路ブロックと電源端子とを接続する半導体集積回路100。

(もっと読む)

出力回路及び出力装置

【課題】出力端子をシンク型又はソース型に切換える場合に、基板を交換する必要がなく、また出力端子に誤って電源を接続してもスイッチング素子の破損を防止することができる出力回路及び該出力回路を備える出力装置を提供する。

【解決手段】ディップスイッチ81にてソース型出力対応モードを選択した場合に、第2スイッチング素子32を常時オンにし、第1スイッチング素子31のオン/オフ制御によって、外部機器への出力をオン/オフ制御する。ディップスイッチ81にてシンク型出力対応モードを選択した場合に、第1スイッチング素子31を常時オンにし、第2スイッチング素子32のオン/オフ制御によって、外部機器への出力をオン/オフ制御する。またソース型出力対応モードを選択した状態で、第2出力端子32に誤って外部電源を接続した場合、第2スイッチング素子32に大電流が流れるが、直ちにヒューズ35が切断される。

(もっと読む)

レベルシフト回路

【課題】消費電流を低減することができ、信号伝達に必要な電源電圧を低減することができ、電源電圧が揺れても正確に信号を伝達することができるレベルシフト回路を得る。

【解決手段】本発明のレベルシフト回路は、インバータ回路INV2、レベルシフト素子MOS1、第1の抵抗R1及びカレントミラー回路CM1を備える。インバータ回路INV2は、入力信号を反転して出力する。レベルシフト素子MOS1は、入力信号を反転した信号をゲート信号として動作する。第1の抵抗R1の一端は、インバータ回路の出力に接続されている。カレントミラー回路CM1は、第1の抵抗R1を介してインバータ回路INV2の出力から入力した電流に対応する電流をレベルシフト素子MOS1のソースから接地点に流す。

(もっと読む)

レベルシフト回路

【課題】消費電流を低減することができ、信号伝達に必要な電源電圧を低減することができ、電源電圧が揺れても正確に信号を伝達することができるレベルシフト回路を得る。

【解決手段】本発明のレベルシフト回路は、インバータ回路INV2、レベルシフト素子MOS1、第1の抵抗R1及びカレントミラー回路CM1を備える。インバータ回路INV2は、入力信号を反転して出力する。レベルシフト素子MOS1は、入力信号を反転した信号をゲート信号として動作する。第1の抵抗R1の一端は、インバータ回路の出力に接続されている。カレントミラー回路CM1は、第1の抵抗R1を介してインバータ回路INV2の出力から入力した電流に対応する電流をレベルシフト素子MOS1のソースから接地点に流す。

(もっと読む)

レベルシフト回路

【課題】外的要因により発生するコンデンサの充放電による信号伝達不良を防止して、確実な信号伝達を行うレベルシフト回路。

【解決手段】第1電圧レベルを第1電圧レベルとは異なる第2電圧レベルに変換するレベルシフト回路であって、第2電圧レベルの論理電圧状態を第1コンデンサC1を介してセットするセットレベル回路20aと、第2電圧レベルの論理状態を第2コンデンサC2を介してリセットするリセットレベル回路20bと、セットレベル回路のセット信号とリセットレベル回路のリセット信号とによりローサイドスイッチQ1に直列に接続されたハイサイドスイッチQ2をオン/オフ駆動する駆動回路24と、第1コンデンサ及び第2コンデンサに流れる電流の内の少なくともいずれか一方を検出する電流検出回路15,16,を備える。

(もっと読む)

スイッチング制御回路

【課題】ハーフブリッジ回路を構成する2つのスイッチング素子を共にオンさせるような2つのパルス信号が入力された場合であっても、2つのスイッチング素子が同時にオンすることを確実に防止すること。

【解決手段】第1パルス信号と第2パルス信号に基づいて、第1出力端子(DRV1)4からP型MOSFET(MOS1)10に第1駆動信号が出力され、第1パルス信号と第2パルス信号に基づいて、第2出力端子(DRV2)5から第2スイッチング素子であるN型MOSFET(MOS2)11に第2駆動信号が出力されるように構成され、保護回路20によりP型MOSFET(MOS1)10及びN型MOSFET(MOS2)11のうちの少なくとも一方がオフされるようにした。

(もっと読む)

メモリ装置内の自動リセット(SELFRESET)クロックバッファ

【解決手段】メモリ装置はクロックバッファ回路を含む。前記クロックバッファ回路は、クロスカップル論理回路を含む。前記クロスカップル論理回路は、前記論理ゲートのうち1つの出力が前記論理ゲートのうち1つの入力に結合された少なくとも2つの論理ゲートを備える。前記クロスカップル論理回路は、クロック信号を受けるため入力に結合される。前記メモリ装置はまた、前記クロスカップル論理回路の前記出力からクロック信号を生成するように動作可能なクロックドライバを含む。前記クロック信号から前記クロスカップル論理回路へのフィードバックループは、前記クロスカップル論理回路を制御する。バッファ回路は、前記クロック生成回路による競合を回避しつつ、前記クロック信号を維持するための前記クロック信号に結合された3端子インバータを含む。前記メモリ装置は、チップ選択信号によって有効とされる。 (もっと読む)

負荷駆動回路

【課題】負荷駆動用の電界効果トランジスタのゲートソース間の耐圧保護をしつつ低消費電流で高速動作可能な負荷駆動回路を提供することを目的としている。

【解決手段】負荷駆動回路においける負荷駆動用の電界効果トランジスタのソースゲート間にツェナー機能デバイスを接続する一方、前記電界効果ドランジスタのゲートにオン電位及びオフ電位を択一的に供給するオンオフスイッチ回路を設け、前記負荷駆動用電界効果トランジスタが導通した場合に前記ツェナー機能デバイスに流れる電流を制限する。

(もっと読む)

半導体集積回路

【課題】降圧回路の出力電位に対するトリミング効率を向上させる。

【解決手段】第1及び第2外部電圧を受け内部電圧(VDL)を発生する降圧回路と、降圧回路に結合され、上記内部電圧の電圧レベルを調整する為の情報を格納する揮発性格納回路(31DR)と、上記内部電圧と上記第2外部電圧とを受け、内部電圧と上記第2外部電圧との間で動作される中央処理装置(10)と、上記中央処理装置によってアクセス可能な不揮発性記憶素子とを有する。上記不揮発性記憶素子に格納された上記情報は半導体集積回路の初期化に応答して読み出され、上記揮発性格納回路は上記不揮発性記憶素子から読み出された上記情報を上記半導体集積回路の初期化に応答して格納することにより、上記情報によって調整された内部電圧が上記降圧回路から上記中央処理装置へ供給される。

(もっと読む)

半導体集積回路及び電圧制御発振器

【課題】待機状態から任意の容量安定状態への過渡時間の短いMOSバラクタを提供する。

【解決手段】Nウェルを有するMOSバラクタ素子の動作待機時に電極の電位からウェル領域の電位を引いた電位差を0以上にする制御回路を備えることにより、動作待機時から任意の容量安定状態への過渡時間を短くすることが可能となる。また、Pウェルを有するMOSバラクタ素子の動作待機時に電極の電位からウェル領域の電位を引いた電位差を0以下にする制御回路を備えることにより、動作待機時から任意の容量安定状態への過渡時間を短くすることが可能となる。

(もっと読む)

差動アンプ回路

【課題】インダクタンスを外部から簡単に調整することができる差動アンプ回路を得る。

【解決手段】差動対を構成する第1及び第2のトランジスタと、第1のトランジスタの出力端子と電源との間に接続された第1のインダクタと、第2のトランジスタの出力端子と電源との間に接続された第2のインダクタと、第1のインダクタにシリアル接続された第1のトランスミッションゲートと、第2のインダクタにシリアル接続された第2のトランスミッションゲートとを有する。

(もっと読む)

定電圧回路、電子機器、電子制御機器

【課題】流れる電流の量にかかわらず出力電圧を一定に維持することで、電子制御機器等の誤動作を防止することのできる定電圧回路を提供する。

【解決手段】流入電流に基づいて基準電圧が変化する第一半導体素子Q10を備えた基準電圧発生回路11と、前記基準電圧と出力電圧の電圧差に応じて出力電流を調整して定電圧制御する第二半導体素子Q20と、前記基準電圧と出力電圧の電圧差を検出する第三半導体素子Q30を備えた電圧検出回路12と、前記電圧検出回路12により検出された電圧差に対応した電流を前記基準電圧発生回路11に供給するバイアス電圧補正回路13を備えて構成される定電圧回路10であって、前記第一半導体素子Q10及び前記第三半導体素子Q30の夫々に抵抗R10、R30が直列に接続されている。

(もっと読む)

スイッチング回路

【課題】安定したスイッチング特性を有するスイッチング回路を提供する。

【解決手段】コレクタが定電流源11を介して電源Vccに接続され、エミッタが基準電位GNDに接続されたトランジスタ12と、コレクタの電位に基づき、トランジスタ12のゲートに信号を出力してオンとオフを切換え、オフからオンに切り換えるときには、入力電圧Vinがトランジスタ12の閾値電圧Vthより高い第1の電圧V1のときにトランジスタ12を切換え、オンからオフに切り換えるときには、入力電圧Vinがトランジスタ12の閾値電圧Vthより低い第2の電圧V2のときにトランジスタ12を切換えるドライブ手段とを具備する。

(もっと読む)

1 - 20 / 26

[ Back to top ]