Fターム[5J056DD58]の内容

Fターム[5J056DD58]に分類される特許

1 - 19 / 19

液晶表示装置

【課題】動作を不安定にすることなく、各トランジスタの特性劣化を抑制することが可能

な半導体装置を提供することを課題とする。

【解決手段】非選択期間において、トランジスタが一定時間毎にオンすることで、シフト

レジスタ回路の出力端子に電源電位を供給する。そしてシフトレジスタ回路の出力端子は

、該トランジスタを介して電源電位が供給される。該トランジスタは非選択期間において

常時オンしていないので、該トランジスタのしきい値電位のシフトは、抑制される。また

、シフトレジスタ回路の出力端子は、該トランジスタを介して一定期間毎に電源電位が供

給される。そのため、シフトレジスタ回路は、ノイズが出力端子に発生することを抑制で

きる。

(もっと読む)

バス絶縁型PLC

【課題】フォトカプラ等の絶縁素子の必要数を大幅に削減可能として上記実装装置の規模の小型化とコストの大幅な削減化を可能とすること。

【解決手段】CPU2と、CPUとの間で信号の入力伝送および出力伝送の少なくとも一方の伝送をする複数の入/出力回路6,7と、CPUからの信号はシリアル/パラレル変換し、入/出力回路からの信号はパラレル/シリアル変換するバスI/F3a,3bと、CPUとバスI/Fとの間に配されて信号をシリアル伝送する信号伝送バス8a,8bと、バスI/Fと各入/出力回路との間に配されて信号をパラレル伝送する信号伝送バス9a,9b,10a,10bと、を備え、シリアル信号伝送バス8a,8b内に、絶縁回路部20a,20bを設けた構成。

(もっと読む)

OFDM方式モデム

【課題】OFDM方式モデムにおいて、受信信号の最大値以上の電圧を発生する高電圧生成回路を設けることなく受信スイッチの動作の信頼性を確保できるようにする。

【解決手段】制御部2が変調および復調を行い回線接続部4を介して通信の回線10に接続されるOFDM方式モデムにおいて、受信通信路11に設けられ子機の受信インピーダンスを親機に対して子機を複数台接続したときの通信性能の低下を抑える高インピーダンスとする高インピーダンス受信部20、および受信通信路の開閉を行うフォトモスリレー21,211,212を備え、前記高インピーダンス受信部が前記フォトモスリレーの出力回路のMOS FETにながれる電流を許容電流以下とし、前記制御部が前記フォトモスリレーを開閉制御する。

(もっと読む)

半導体装置及び電子機器

【課題】消費電力を低減することができる半導体装置及びそれを用いた電子機器を提供す

ることを課題とする。

【解決手段】本発明の半導体装置は、高電位電源から第1の電位が供給され、低電位電源

から第2の電位が供給され、入力ノードに第1の信号が入力されると、出力ノードから第

2の信号を出力する。本発明の半導体装置は、第2の信号の電位差を、第1の電位と第2

の電位の電位差よりも小さくすることにより、配線の充電と放電に伴う消費電力を低減す

ることができる。

(もっと読む)

駆動回路および表示装置

【課題】出力電圧の立ち上がるタイミングのばらつきを低減することの可能な駆動回路、およびこの駆動回路を備えた表示装置を提供する。

【解決手段】バッファ回路1は、互いに直列に接続されたインバータ回路10およびインバータ回路20を備えている。インバータ回路20は、3つのトランジスタTr21,Tr22,Tr23を有している。そのうちの2つのトランジスタTr21,Tr22は、デュアルゲート型のトランジスタである。これらトランジスタTr21,Tr22のバックゲートの電圧を調整することにより、トランジスタTr21,Tr22の閾値電圧を調整することができる。

(もっと読む)

電力調整装置およびLEDドライバ

【課題】制御信号を用いて電力を多段階制御する電子機器、および2段階制御する電子機器の何れにも適用可能でありながら、極力簡易な制御信号が与えられるだけで適切に電力を調整し得る電力調整装置を提供する。

【解決手段】第1状態または第2状態をとる制御信号を受付け、制御信号に基づいて、所定装置に供給される電力を調整するものであって、制御信号が第1状態から第2状態に遷移した場合、遷移時点から所定の判定時間が経過するまでに、制御信号が第1状態に戻ったかを判定する機能と、戻った場合には、第1方式によって電力を現状と異なる値に調整し、戻らなかった場合には、第2方式によって電力を現状と異なる値に調整する機能を備え、第1方式は、制御信号に基づき、電力を2段階以上に設定された各値の何れかに調整する方式であり、第2方式は、電力を所定値に調整する方式である電力調整装置とする。

(もっと読む)

半導体集積回路

【課題】電源起動時のリーク電流によるトランジスタの誤作動を防止することが可能な半導体集積回路を提供すること。

【解決手段】発明にかかる半導体集積回路は、第1の制御信号を駆動回路120を介して出力する論理回路209と、コレクタが高電位側の電源電圧VCCに接続され、エミッタが出力端子VOUTに接続され、ベースに入力される第1の制御信号に応じてオンオフが制御されるNPN型バイポーラトランジスタ201をそなえる。また、一方の端子がベースと駆動回路210との間のノードに接続され、他方の端子が電源電圧及び接地電圧のいずれか一方に接続されたトランジスタスイッチ203と、第1のトランジスタスイッチに並列に接続された抵抗素子205とを備える。このような回路構成により、電源起動時のリーク電流によるトランジスタの誤作動を防止することができる。

(もっと読む)

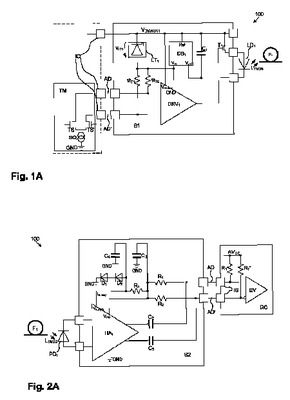

TMDS符号化信号を伝送する回路装置及び方法

少なくとも部分的に、特に少なくともタイムスロット方式でTMDS符号化され、且つ特に少なくとも1つのDVIデータ接続、及び/又は、少なくとも1つのHDMIデータ接続に割り当てられた信号を、少なくとも1つのデータソースから少なくとも1つのデータシンクへ安価に伝送する回路装置(100;100’)及び方法を提供するために、

駆動回路(S1;S1’)は、上流に接続され且つ前記データソースに割り当てられた少なくとも1つの接続インターフェース(IQ)によって、約5ボルトの供給電圧を含み、特に約55ミリアンペア以下でチャージすることができる、供給電圧(VDVI/HDMI)を供給されること、

前記駆動回路(S1;S1’)の下流に接続された少なくとも1つの発光素子(LD1)、特に少なくとも1つの光ダイオード、少なくとも1つの発光ダイオード、少なくとも1つのレーザダイオード、あるいは少なくとも1つの半導体レーザを含む少なくとも1つのレーザによって、電気的なTMDS符号化信号を電気−光変換して、前記TMDS符号化信号を与えられた光(LTMDS)として、少なくとも1つの光ファイバー(F1)、特に少なくとも1つのガラス繊維又は少なくとも1つのプラスチックファイバーを含む少なくとも1つのプラスチック材料繊維に、連結すること、

少なくとも1つのTMDSトランスミッタ(TM)からデータソースに割り当てられた前記接続インターフェース(IQ)へ供給される直流電流部分は、前記駆動回路(S1;S1’)によって前記発光素子(LD1)を制御する変調信号電流に変換されること、

前記TMDS符号化信号を与えられた前記光(LTMDS)は、少なくとも1つの光吸収素子(PD1)、特に少なくとも1つのフォトダイオードによって、前記光ファイバー(F1)から取り出されて、光−電気変換され、前記光吸収素子(PD1)の下流且つ前記データシンクに割り当てられた少なくとも1つの接続インターフェース(IS)の上流に接続された少なくとも1つのトランスインピーダンス変換回路(S2;S2’)に供給され、前記トランスインピーダンス変換回路(S2;S2’)は、少なくとも1つの差動ペア配線(AD、AD’)によって印加される直流電圧部分によって提供されることが提案される。  (もっと読む)

(もっと読む)

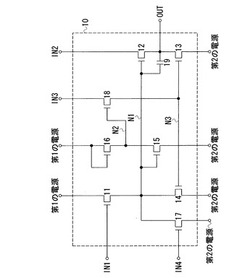

プログラマブルロジックデバイス、カード及び伝送装置

【課題】 冗長構成とすることなく、デバイスの運用を中断せずに機能の更新が可能となると共に、冗長分のコスト及び消費電力を削減できるプログラマブルロジックデバイス、カード及び伝送装置を提供する。

【解決手段】 FPGA10は、入力される入力信号を複数に分配し、論理ブロックに既に構成された論理回路1及び論理ブロックに新規に構成される新規な論理回路11に対して、分配された信号を出力する分配回路部2と、論理回路1及び新規な論理回路11からの各出力信号のうちいずれかを選択するセレクタ回路部3と、新規な論理回路11に出力信号を出力するように分配回路部2を制御すると共に、新規な論理回路11からの出力信号を出力するようにセレクタ回路部3を制御する切り替え制御部4と、を備える。

(もっと読む)

電気的に画素化された発光素子

電気的に画素化された発光素子、電気的に画素化された発光素子を形成するための方法、電気的に画素化された発光素子を含むシステム、電気的に画素化された発光素子の使用方法。 (もっと読む)

半導体デバイス、表示パネル及び電子機器

【課題】使い勝手の良い単一チャネル型のバッファ回路を提案する。

【解決手段】絶縁基板上に単一チャネルの薄膜トランジスタで形成されるバッファ回路を、(a)第1及び第2の薄膜トランジスタが直列に接続された回路構成を有し、第1及び第2の薄膜トランジスタの接続中点を出力端とする第1の出力段と、(b)第1の制御配線に制御電極が接続される第7の薄膜トランジスタと、第2の制御配線に制御電極が接続される第8の薄膜トランジスタが直列に接続された回路構成を有し、第7及び第8の薄膜トランジスタの接続中点に現れる電位を第3の制御配線に与える第2の出力段と、(c)一方の主電極が第1の制御配線に接続され、制御電極が第3の制御配線に接続される回路構成を有し、出力端に出力パルスが現われている期間、セットパルスと同じ論理レベルの電位を第1の制御配線に印加する第9の薄膜トランジスタとで構成される。

(もっと読む)

半導体回路

【課題】温度変化や製造プロセスのばらつきに起因する出力の変動を抑制する。

【解決手段】温度が上昇するとバイアス電圧生成回路28からNMOSトランジスタ26のゲートに供給されるバイアス電圧VGSが低下することで参照電流Irefが低下し、温度上昇に伴う電圧Vcの低下幅が小さくなり、温度が低下するとバイアス電圧VGSが上昇することで参照電流Irefが増大し、温度低下に伴う電圧Vcの増加幅が小さくなる。、製造プロセスのばらつきによりトランジスタの閾値電圧Vtが設計値より低下した場合は、バイアス電圧VGSも低下することで参照電流Irefが低下し、閾値電圧Vtの低下に伴う電圧Vcの低下幅が小さくなり、製造プロセスのばらつきによりトランジスタの閾値電圧Vtが設計値より上昇している場合は、バイアス電圧VGSも上昇することで参照電流Irefが増大し、閾値電圧Vtの上昇に伴う電圧Vcの増加幅が小さくなる。

(もっと読む)

駆動回路、駆動方法、固体撮像装置および電子機器

【課題】電源電圧の低電圧側の電圧と高電圧側の電圧との間の中間電圧での駆動を、トランジスタのゲート酸化膜に高耐圧素子構造を適用することなく実現できるようにする。

【解決手段】第1,第2出力バッファ回路20,30Aを用いた駆動回路10において、当該駆動回路10を構成するトランジスタのゲート酸化膜にその耐圧ΔVlimを超える電圧を印加することなく、第1出力バッファ回路20の作用によって耐圧ΔVlimを超えた電圧振幅VL−VHで駆動する。これに加えて、第2出力バッファ回路30Aにおいて、出力端子35側のトランジスタMp32,Mn32を、バイアス電圧の定常印加でなく、耐圧範囲内の電圧(VL〜VD,VS〜VH)で駆動するとともに、ノードN31,N32側のトランジスタMp31,Mn31を、耐圧範囲内の電圧でなく、範囲外の電圧VL〜VHで駆動することで、中間電圧VMでの駆動を実現する。

(もっと読む)

バッファ回路とそれを用いた受光回路

【課題】電源電圧変動によるコレクタ−エミッタ間の電圧ずれをなくし、オフセット電圧の電源電圧依存性を良好とする。

【解決手段】本発明の一態様に係るバッファ回路は、ベースをBIAS1に接続したトランジスタt1、トランジスタt2と、トランジスタt1のエミッタの流出電流と入力電流の和を一定電流とする定電流回路と、トランジスタのエミッタの流出電流を前記一定電流と同じ電流とする定電流回路と、トランジスタt1のコレクタ電流と、トランジスタt2のコレクタ電流とを同じ電流とする第1ミラー回路3とを備え、第1ミラー回路3は、トランジスタt1のコレクタに、コレクタが接続されたトランジスタt3と、トランジスタt2のコレクタに、コレクタが接続されたトランジスタt4とを有し、トランジスタt3とトランジスタt1の間の接続点及びトランジスタt4とトランジスタt2の間の接続点には、Vref電圧に基づいた電圧が供給される。

(もっと読む)

レベルシフト回路、電気光学装置、およびレベルシフト方法

【課題】レベル変換の信頼性を向上すると共に構成を簡素化する。

【解決手段】ラッチ回路LATの出力ノードN2にはトランジスタTnpが設けられている。このトランジスタTnpは、入力信号IN1の論理レベルが遷移する直前の所定期間においてアクティブとなるプリチャージ信号PRCによってオン状態となり、出力ノードN1をローレベル(VSS2)にプリチャージする。入力ノードN1にはトランジスタTndが設けられている。トランジスタTndは入力信号IN1はローレベルからハイレベルに遷移するとオン状態となり、入力ノードN1の電位をローレベル(VSS2)に設定する。これによって、ラッチ回路LATの記憶内容を確実に更新することができる。

(もっと読む)

レベルシフト回路、駆動装置、LEDヘッド及び画像形成装置

【課題】低電圧駆動で駆動される低耐圧素子で構成される論理回路部分と駆動電圧に耐える高耐圧の素子を同一チップのICで構成する場合、高耐圧素子の部分に半導体製造プロセスによる微細加工が適用できず、プロセス工程が増加するという問題があった。

【解決手段】電源供給端子VDDにソース端子が接続されたPチャンネル型の第1と第2のMOSトランジスタと、グランドにソース端子が接続されたNチャンネル型の第3と第4のMOSトランジスタと、前記第3のMOSトランジスタのドレインにソース端子が接続されるNチャンネル型の第5のMOSトランジスタと、前記第4のMOSトランジスタのドレインにソース端子が接続されるNチャンネル型の第6のMOSトランジスタと、第2の電源供給端子VDにソースが接続されたPチャンネル型の第7と第8のMOSトランジスタとを備える。

(もっと読む)

入れ子状のトランスインピーダンス増幅器

【課題】高利得、広帯域のトランスインピーダンス増幅器を提供する。

【解決手段】トランスインピーダンス増幅器3900は、入力及び出力を有する第1の演算増幅器3604を備える。第2の演算増幅器3606は、入力、及び第1の演算増幅器3604の入力に接続する出力を有する。第1のフィードバック素子は、一端を第1の演算増幅器3604の非反転入力に接続し、他端を第1の演算増幅器3604の反転出力に接続する。第1のフィードバック素子は、第1のキャパシタンス3902を備える。第2のフィードバック素子は、一端を第1の演算増幅器3604の反転入力に接続し、他端を第1の演算増幅器3604の非反転出力に接続する。

(もっと読む)

レーザまたは変調器駆動用の低電圧高速出力段

本発明は、ギガビット/秒程度のデータ速度で、特にレーザ・ダイオード(700)または変調器を駆動するための駆動回路(100)を提供する。駆動回路(10)はレーザ・ダイオード(700)または変調器を効率的に駆動できる低電圧高速出力段を有する。ドライバ回路(10)は、一連の回路を備えており、前記一連の回路は、スルーレート制御回路、少なくとも1つのトランスリニア増幅器(200、201、202)、プッシュプル段(300)、および負荷電流を駆動する出力段(400)を備える。その多様性により、このドライバは他の用途、例えばライン・ドライバ、ケーブル・ドライバ、バックプレーン相互接続用の高速シリアル・インターフェースなどに使用されてよい。ドライバは、高い電力効率でもって、例えば公称3.3Vで2.7Vまでの低電源電圧で動作することができる。1つの主要な手がかりは、出力段によって生成された大きな信号電流全部を、例えば駆動されるレーザ・ダイオード中で、電源線路で電流を浪費することなく使用することである。  (もっと読む)

(もっと読む)

インタフェース回路

【課題】 P1形およびP2形のうちの所望の形式で使用することができ、応答速度が速いインタフェース回路を提供する。

【解決手段】 インタフェース回路をP1形で使用する場合は端子T4とT6を接続し、P2形で使用する場合は端子T5とT6,T7とT8をそれぞれ接続する。車両感知信号/Dが活性化レベルの「L」レベルになると、P1形の場合はフォトトランジスタ6が導通せず、出力端子T2,T3間が非導通状態になり、P2形の場合はフォトトランジスタ6が導通し、出力端子T2,T3間が導通状態になる。従来のフォトMOSトランジスタの代わりにフォトトランジスタ6を使用したので、応答速度が速くなる。

(もっと読む)

1 - 19 / 19

[ Back to top ]