Fターム[5J056EE11]の内容

Fターム[5J056EE11]に分類される特許

1 - 20 / 341

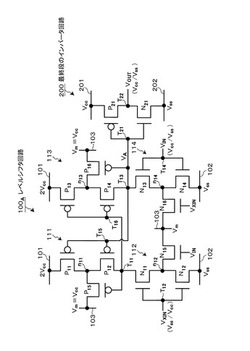

レベルシフタ回路、走査回路、表示装置、及び、電子機器

【課題】回路を構成するトランジスタのソース−ドレイン耐圧を維持したまま、走査回路の最終段のインバータ回路の入力電圧の振幅を増大させることが可能なレベルシフタ回路を提供する。

【解決手段】第1固定電源側の2つのトランジスタ回路が第1導電型のトランジスタから成り、第2固定電源側の2つのトランジスタ回路が第2導電型のトランジスタから成るとともに、第1固定電源側の2つのトランジスタ回路及び第2固定電源側の2つのトランジスタ回路の少なくとも一方側の2つのトランジスタ回路はダブルゲートトランジスタから成るレベルシフタ回路において、一方の電源側の2つのトランジスタ回路が動作状態のとき、他方の電源側の2つのトランジスタ回路のダブルゲートトランジスタの共通接続ノードに第3固定電源の電圧を与えるスイッチ素子を設ける。

(もっと読む)

集積回路、集積回路装置及び伝送システム

【課題】回路遅延の増大を抑制しながら、回路しきい値電圧のバラツキを抑制できる集積回路を提供する。

【解決手段】

集積回路1は、高位側電源VDDと出力端子OUTの間に接続されたPMOSトランジスタMP1と、低位側電源VSSと出力端子OUTの間に接続されたNMOSトランジスタMN1と、高位側電源VDDと出力端子OUTの間に直列に接続されたPMOSトランジスタMP2及びNMOSトランジスタMN3と、低位側電源VDDと出力端子OUTの間に直列に接続されたNMOSトランジスタMN2及びPMOSトランジスタMP3とを備えている。PMOSトランジスタMP1、MP2、及びNMOSトランジスタMN1、MN2のゲートが入力端子INに接続されている。また、NMOSトランジスタMN3のゲートは高位側電源に接続され、PMOSトランジスタMP3のゲートは低位側電源に接続されている。

(もっと読む)

出力回路

【課題】高電圧信号を出力する回路を低耐圧トランジスタで構成しても、信頼性を向上させることのできる出力回路を提供する。

【解決手段】実施形態の出力回路は、出力部1が、高電圧電源端子VCCHと出力端子とZの間に接続されPMOSトランジスタP11、P12と、接地電位端子GNDと出力端子Zとの間に接続されたNMOSトランジスタN11、N12とを有し、低電圧入力信号INが入力されるプリバッファ部2が、PMOSトランジスタP11、NMOSトランジスタN11へ、VCCHよりも小さい振幅のゲート電圧PG、NGを出力する。PMOSトランジスタP12およびNMOSトランジスタN12のゲート端子へVCCHよりも低い定電圧VGが印加され、PMOSトランジスタP12の基板へVCCHよりも低い基板バイアス電圧VBPが印加され、NMOSトランジスタN12の基板へ接地電位よりも高い基板バイアス電圧VBNが印加される。

(もっと読む)

半導体装置及びこれを備える半導体モジュール

【課題】データ出力バッファの正確なインピーダンスキャリブレーション動作を行う。

【解決手段】電源ラインVL1とデータ端子24との間に接続されたP型トランジスタユニット201と、電源ラインVL1とキャリブレーション端子ZQとの間に接続されたP型トランジスタユニット111〜114と、キャリブレーション端子ZQの電位が基準電位VREFと一致するよう、P型トランジスタユニット111〜114インピーダンスを調整し、一致した状態におけるP型トランジスタユニット111〜114の一つのインピーダンスをP型トランジスタユニット201に反映させるインピーダンス制御回路とを備える。これにより、基準電位VREFが電源電位VDDの半分のレベルからオフセットしたレベルに設定されている場合であっても、正確なキャリブレーション動作を行うことができる。

(もっと読む)

論理回路、半導体集積回路

【課題】供給される電源電圧の変動を抑制することができる論理回路及び当該論理回路が搭載される半導体集積回路を提供すること。

【解決手段】本発明の一態様であるバッファ回路100は、バッファ部11、電圧検出部12及びスイッチ部13を有する。バッファ部11は、電源端子Ts1又は電圧レギュレータ1と電源端子Ts2との間に接続されることにより電源供給され、入力信号INと同論理の信号を出力端子Toutへ出力する。電圧検出部12は、出力端子Toutの電圧を検出し、検出結果に基づく検出信号Sdetを出力する。スイッチ部13は、検出信号Sdetに応じて、バッファ部11を電源端子Ts1又は電圧レギュレータ1と接続する。

(もっと読む)

電力制御回路、それを含む半導体装置及び該電力制御回路の動作方法

【課題】電力制御回路、それを含む半導体装置及び該電力制御回路の動作方法を提供する。

【解決手段】本発明の電力制御回路は、電源電圧とロジック回路との間に連結されてロジック回路への電源供給をスイッチングする回路であって、外部から並列的にモード転換信号を受信する複数の第1パワーゲーティングセルと、第1パワーゲーティングセルのうちの何れか1つと連結される少なくとも1つの第2パワーゲーティングセルと、第2パワーゲーティングセルと直列連結される複数の第3パワーゲーティングセルと、直列連結された複数の第3パワーゲーティングセルのうち、先端の第3パワーゲーティングセルと並列連結される複数の第4パワーゲーティングセルとを含み、モード転換信号は、第1パワーゲーティングセルのうちの何れか1つ、第2及び第3パワーゲーティングセルを経て第4パワーゲーティングセルに伝達され、第1ないし第4パワーゲーティングセルのそれぞれは、各自のセルに入力されるモード転換信号に応答して電源供給をスイッチングする。

(もっと読む)

半導体装置

【課題】出力信号の立ち上がり時間および立下り時間が短い半導体装置を提供する。

【解決手段】このクロックドライバは、クロック信号CLKBの反転信号CLKを出力ノードN2に出力するインバータ1と、電源電圧VCCのラインと出力ノードN2との間に直列接続されたトランジスタP2,P3と、出力ノードN2と接地電圧VSSのラインとの間に直列接続されたトランジスタQ2,Q3と、クロック信号CLKを所定時間だけ遅延させてトランジスタP2,Q3のゲートに与える遅延回路3とを含む。たとえば、クロック信号CLKBが「L」レベルから「H」レベルに変化すると、所定時間だけトランジスタQ2,Q3がともにオンして、出力ノードN2から電流を引き抜く。

(もっと読む)

CMOS論理集積回路

【課題】異なる論理レベルの信号を高速に伝達可能なCMOS論理集積回路を提供する。

【解決手段】レベルシフト回路とCMOS論理回路とを備えたことを特徴とするCMOS論理集積回路が提供される。前記レベルシフト回路は、第1の低電位と前記第1の低電位よりも高い第1の高電位との間で変化する第1の論理レベルの信号を前記第1の低電位と前記第1の高電位よりも高い第2の高電位との間で変化する第2の論理レベルの信号に変換する。前記CMOS論理回路は、前記第1の論理レベルの第1の信号がゲートに入力される第1のNチャンネル形MOSFETと、前記第1のNチャンネル形MOSFETに直列に接続され前記第1の信号と反転関係にある前記第2の論理レベルの第2の信号がゲートに入力される第2のNチャンネル形MOSFETとを有する。

(もっと読む)

コンパレータ、及びそれを用いた半導体装置

【課題】新たな構成のチョッパ型のコンパレータを提供する。

【解決手段】コンパレータは、インバータと、容量素子と、第1のスイッチと、第2のスイッチと、第3のスイッチとを有し、インバータの入力端子と出力端子とは、第1のスイッチを介して電気的に接続され、インバータの入力端子は、容量素子の一対の電極のうちの一方と電気的に接続され、容量素子の一対の電極のうちの他方は、第2のスイッチを介して参照電位が与えられ、入力された信号電位は第3のスイッチを介して容量素子の一対の電極のうちの他方に与えられ、インバータの出力端子から出力される電位を出力信号とし、第1のスイッチは、チャネルが酸化物半導体層に形成されるトランジスタを用いて構成される。

(もっと読む)

スイッチング回路

【課題】スイッチング回路のデッドタイム制御における電力効率を向上させる。

【解決手段】スイッチング制御部2は、パルス信号Aがロウレベルの時に、Pチャンネル電界効果トランジスタM3のドレイン電位G1が立ち上がったのを検出してから、Nチャンネル電界効果トランジスタM4のドレイン電位G2が立ち上がるように、スイッチング部Wを制御し、パルス信号Aがハイレベルの時に、Nチャンネル電界効果トランジスタM4のドレイン電位G2が立ち下がったのを検出してから、Pチャンネル電界効果トランジスタM3のドレイン電位G1が立ち下がるように、スイッチング部Wを制御する。

(もっと読む)

スイッチ装置および試験装置

【課題】入力電圧範囲の大きな半導体スイッチ装置を提供する。

【解決手段】外部から入力される制御電圧に応じて第1端子および第2端子間を電気的に接続または切断するスイッチ装置であって、第1端子および第2端子の間にソースおよびドレインが接続され、当該スイッチ装置に入力される入力電圧とゲート電圧との差に応じてオンまたはオフとなるメインスイッチと、制御電圧および入力電圧に応じて第1基準電圧を電圧シフトさせた駆動電圧をメインスイッチのゲートに供給する制御部と、を備えるスイッチ装置を提供する。

(もっと読む)

制御電圧生成回路、定電流源回路及びそれらを有する遅延回路、論理回路

【課題】回路規模を増大させることなくトランジスタの閾値電圧に応じた制御電圧を精度良く生成することが可能な制御電圧生成回路を提供すること。

【解決手段】本発明にかかる制御電圧生成回路は、高電位側電源と低電位側電源との間に直列に接続された同一導電型の複数のMOSトランジスタを有し、何れかのMOSトランジスタのドレイン電圧を参照電圧Vp1として生成する参照電圧生成部11と、高電位側電源と低電位側電源との間に直列に接続され参照電圧生成部11と同一導電型の複数のMOSトランジスタを有し、何れかのMOSトランジスタのゲートに参照電圧が供給され、何れかのMOSトランジスタのドレイン電圧を制御電圧(バイアス電圧)として出力する電圧変換部12と、を備える。

(もっと読む)

半導体装置

【課題】基準電圧生成回路に電源電圧が投入されてから安定平衡状態に達するまでの時間を短縮する回路を提供することを課題とする。

【解決手段】スタートアップ回路から基準電圧生成回路に入力される初期電圧を、基準電圧生成回路の安定平衡状態における内部電圧に近い電圧とすればよい。また、このような電圧を電源が遮断された状態でも保持しておくことができ、且つ起動時に出力することのできるスタートアップ回路とすればよい。

(もっと読む)

半導体回路および半導体装置

【課題】簡易な構成で電荷の再利用効率を高め、複数のLSIを搭載したシステム全体のエネルギー効率を向上することが可能な半導体回路および半導体装置を提供する。

【解決手段】入力端子20にLレベルの信号が入力されたとき、回路素子10の出力端子22に接続される信号線24の配線容量Cpに正の電荷が充電される。入力端子20にHレベルの信号が入力されたとき、NMOSトランジスタNr1は、論理素子のNMOSトランジスタN1が導通するのと同時に導通する。これにより、信号線24から放電される電荷の一部が、NMOSトランジスタNr1およびダイオードD1を介して、電荷回収線2に移動する。電荷回収線2が回収した電荷は、電荷再利用端子3を介して半導体チップ1Aの外部に放出されると、電荷再利用線30に接続された電荷回収用の容量素子Cextに蓄積される。蓄積され電荷は、他の半導体回路等の電源端子に供給される。

(もっと読む)

半導体装置

【課題】しきい値が従来例では動作しないような値でも動作させることが可能な半導体装置である。

【解決手段】第1乃至第3のN型トランジスタと、第1乃至第3のP型トランジスタと、アナログスイッチと、容量手段とを有し、容量手段の一方は、アナログスイッチ、第3のN型トランジスタのソース又はドレインの他方、及び第3のP型トランジスタのソース又はドレインの他方と電気的に接続され、容量手段の容量は、第1のP型トランジスタ及び第1のN型トランジスタで発生する容量より大きく、アナログスイッチには、第1のラッチ信号、第2のラッチ信号、及びデータ信号が入力され、第1のラッチ信号は、第2のP型トランジスタのゲート、及び第3のN型トランジスタのゲートに入力され、第2のラッチ信号は、第2のN型トランジスタのゲート、及び第3のP型トランジスタのゲートに入力される半導体装置である。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】出力信号遅延を抑制し、消費電流の増大を抑制する出力回路の提供。

【解決手段】入力端子101と出力端子102の電圧を差動入力する差動入力段110からなる差動増幅回路と、第1及び第2の電源端子VDD、VSSに接続された第1及び第2のカレントミラー130、140と、前記第1及び第2のカレントミラーの入力間、出力間に接続される第1、第2の連絡回路150L、150Rと、第1導電型の第1のトランジスタ121と第2導電型の第2のトランジスタ122とからなる出力増幅回路と、前記第1、第2の電源端子VDD、VSSの電源電圧の間の電圧が供給される第3の電源端子VMLの電圧に応じたバイアス信号を受ける第1導電型の第3のトランジスタ161からなる制御回路160と、を備えている。

(もっと読む)

容量性結合を用いる低電圧から高電圧へのレベル変換

【課題】高電圧出力トランジスタまたは回路のゲートを駆動するのに必要な電圧に達することができる。

【解決手段】電圧レベル変換回路は、デジタル論理回路と、第1および第2接続部を有するキャパシタであって、第1および第2接続部のうちの一方がデジタル論理信号へ電気的に結合された、少なくとも1つの高電圧キャパシタと、インバータ対であって、インバータ対のうちの少なくとも1つのインバータの出力が、少なくとも1つの高電圧キャパシタの他方の接続部へ電気的に結合された、たすき掛け結合型インバータ対とを備える。高電圧駆動回路は、2つの低電圧入力信号と、2つの信号であって、第1信号が高位側駆動信号であり、第2信号が低位側駆動信号である、2つの高電圧出力信号と、2つのレベル変換部であって、第1レベル変換部が高位側駆動信号に対応し、第2レベル変換部が低位側駆動信号に対応する。

(もっと読む)

信号駆動回路

【課題】DCオフセットを低減し、正確な出力アナログ電圧値を得る信号駆動回路を提供する。

【解決手段】信号駆動回路は、デジタルデータに基づいて第一アナログ電圧を発生するデジタル/アナログコンバータ(DAC)と、第一アナログ電圧に基づいてアナログバッファによって第二アナログ電圧をロードに選択的に出力、またはアナログバッファを通過することなしに第一アナログ電圧をロードに選択的に出力する出力回路とを含む。

(もっと読む)

トランスミッタ、インタフェイス装置、車載通信システム

【課題】電源電圧の変動に起因する入力信号と出力信号のデューティばらつきを抑制する。

【解決手段】トランスミッタ10は、一端から充電電圧Vaが引き出されるコンデンサ105と、コンデンサ105の充電電流I1を生成する第1定電流源103と、コンデンサ103の放電電流I2を生成する第2定電流源104と、送信入力信号INの論理レベル、及び、充電電圧Vaと基準電圧Vrefとの比較結果に基づいて、コンデンサ105の充放電制御を行う充放電制御部(101、102、106)と、充電電圧Vaに応じてスルーレートが設定され、出力側電源電圧V2に応じて信号振幅が設定される送信出力信号OUTを生成する出力段(109〜116)と、出力側電源電圧V2に依存して基準電圧Vrefを変動させる基準電圧生成部107と、基準電圧Vrefに依存して充電電流I1及び放電電流I2の各電流値を変動させる定電流制御部108と、を有する。

(もっと読む)

負荷容量の駆動回路

【課題】2相クロックによる負荷容量の駆動において、負荷容量間の電荷の再利用を行うと共に、出力クロックの高速化を容易にする。

【解決手段】第1クロック信号とその逆位相の第2クロック信号とに対してそれぞれ遅延した第1及び第2遅延クロック信号が生成される。インバータ回路は第1クロック信号と第1遅延クロック信号とが逆位相である逆転期間において第1クロック信号と逆位相の第1電位を第1出力ノードに生成し且つ第2クロック信号と逆位相の第2電位を第2出力ノードに生成し、第1クロック信号と第1遅延クロック信号とが同位相である一致期間において第1出力ノードと第2出力ノードとをハイインピーダンスとする。スイッチ回路は、逆転期間において第1出力ノードと第2出力ノードとを接続するオン状態とする。第1出力ノードと第2出力ノードとは、駆動対象回路の負荷容量に接続される。

(もっと読む)

1 - 20 / 341

[ Back to top ]