Fターム[5J056EE12]の内容

Fターム[5J056EE12]に分類される特許

1 - 20 / 98

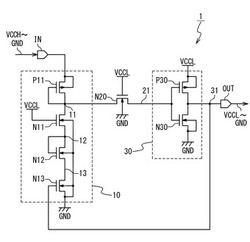

入力回路

【課題】高電位信号を低電位信号に変換する入力回路であって、適切なターゲット反転電位で動作可能な入力回路を提供する。

【解決手段】入力回路は、高電源電位が入力される入力端子とグランド端子との間に接続された抵抗と、抵抗中の第1ノードに接続された第2ノードと、第2ノードと第3ノードとの間に接続されたインバータと、抵抗を通した入力端子とグランド端子との間の電気的接続をON/OFF制御するスイッチと、を備える。ターゲット反転電位は、インバータの反転電位よりも高い。入力端子の電位がターゲット反転電位の場合、第2ノードの電位がその反転電位となる。第2ノードの電位が反転電位より低い場合、インバータは低電源電位を第3ノードに出力し、且つ、スイッチは上記の電気的接続をONする。一方、第2ノードの電位が反転電位より高い場合、インバータはグランド電位を第3ノードに出力し、且つ、スイッチは上記の電気的接続をOFFする。

(もっと読む)

電圧スイッチ回路

【課題】低濃度ドープのPMOSトランジスタを用いて、高電圧ストレスに耐える電圧スイッチ回路を提供する。

【解決手段】該電圧スイッチ回路は、出力回路210、第1の電圧降下制御回路220、第2の電圧降下制御回路230、第3の電圧降下制御回路240、および入力回路250を備えている。また、高電圧源HVの電圧振幅は、基準電圧源Vrefの電圧振幅よりも高く、基準電圧源Vrefの電圧振幅は、論理電圧源VDDの電圧振幅よりも高い。

(もっと読む)

ラッチ回路

【課題】回路面積が小さく、かつ省電力化したラッチ回路を提供する。

【解決手段】複数の論理回路(第1の論理回路11、第2の論理回路13、第3の論理回路15、及び第4の論理回路17)によりラッチ回路1を構成し、選択信号の論理レベルに応じて差動動作とシングルエンド動作の切り替えを行う。また、これらの複数の論理回路11,13,15,17へのクロック入力信号に応じて個々の論理回路をON状態又はOFF状態にすることで、差動動作とシングルエンド動作それぞれにおいてスルー動作とホールド動作をさせる。

(もっと読む)

半導体装置

【課題】消費電力を低減することができる半導体装置及びそれを用いた電子機器を提供す

ることを課題とする。

【解決手段】本発明の半導体装置は、高電位電源から第1の電位が供給され、低電位電源

から第2の電位が供給され、入力ノードに第1の信号が入力されると、出力ノードから第

2の信号を出力する。本発明の半導体装置は、第2の信号の電位差を、第1の電位と第2

の電位の電位差よりも小さくすることにより、配線の充電と放電に伴う消費電力を低減す

ることができる。

(もっと読む)

表示装置、表示モジュール及び電子機器

【課題】回路を構成するトランジスタ数を少なくし、且つレベルシフタを配置することな

くシフトレジスタとして正確に動作を行う半導体回路の提供することを課題とする。

【解決手段】第1端子が高電位電源に接続されたpチャネル型トランジスタと、第1端子

が低電位電源に接続されたnチャネル型トランジスタと、を含む回路群と、インバータ回

路と、をm段(mは任意の正の整数であり、m≧3)有し、第2n−1段目(nは任意の

整数であり、m≧2n≧2)の回路群の前記nチャネル型トランジスタのゲートにはクロ

ック信号が入力され、第2n段目(nは任意の整数であり、m≧2n≧2)の回路群の前

記nチャネル型トランジスタのゲートには反転クロック信号が入力される。

(もっと読む)

演算回路及び演算回路の駆動方法

【課題】消費電力を低減する。

【解決手段】入力信号を元に論理演算処理を行い、論理演算処理の結果に応じて設定される電位を記憶データとして保持し、記憶データに応じた値の信号を出力信号として出力する機能を有し、論理演算処理を行う演算部と、出力信号の電位を、論理演算処理の結果に応じて値が設定される第1の電位に設定するか否かを制御する第1の電界効果トランジスタと、出力信号の電位を、基準電位である第2の電位に設定するか否かを制御する第2の電界効果トランジスタと、を備える。

(もっと読む)

半導体記憶装置

【課題】電源電圧の停止及び復帰を行う構成において、外部回路より半導体記憶装置を制御するための信号数を削減する。

【解決手段】酸化物半導体を半導体層に有するトランジスタを有する記憶回路と、記憶回路に保持されたデータを読み出すための電荷を蓄積する容量素子と、容量素子への電荷の蓄積を制御するための電荷蓄積回路と、データの読み出し状態を制御するデータ検出回路と、電源電圧が供給された直後の期間において、電源電圧の信号と電源電圧を遅延させた信号とにより、電荷蓄積回路による容量素子への電荷の蓄積をさせるための信号を生成するタイミング制御回路と、容量素子の一方の電極の電位を反転して出力するインバータ回路と、を有する構成とする。

(もっと読む)

クロック生成回路および撮像装置

【課題】シュミットトリガー回路と同様な機能を有し、シュミットトリガー回路と比較して貫通電流を低減する。

【解決手段】インバータ回路INV1は、前段回路の回路閾値よりも低い第1の回路閾値を有し、前段回路から出力された入力クロックが入力され、入力クロックの論理状態および第1の回路閾値に応じた第1の出力信号を出力する。インバータ回路INV2は、前段回路の回路閾値よりも高い第2の回路閾値を有し、前段回路から出力された入力クロックが入力され、入力クロックの論理状態および第2の回路閾値に応じた第2の出力信号を出力する。スイッチ回路SWは、第1の出力信号および第2の出力信号が入力され、第1の出力信号および第2の出力信号の論理状態が、異なる状態から同じ状態に変化したときに、異なる論理状態に対応した第1の電圧および第2の電圧のいずれか一方を出力クロックとして出力する。

(もっと読む)

バッファ回路

【課題】入力信号の交流成分の歪み等の影響をなるべく受けることなく、本来のデューティー比(目標デューティー比)で出力信号を出力することのできるバッファ回路を提供する。

【解決手段】バッファ回路10は、デューティー比検出部16と直流成分生成部17とから構成される負帰還回路部によって、入力信号増幅部15の入出力間で出力信号SOのデューティー比に応じた直流成分の信号を帰還させている。つまり、バッファ回路10は、出力信号SOのデューティー比に応じて、入力信号SI´の直流成分をさらに小さくしたり、大きくしたりする。これにより、バッファ回路10は、出力信号SOのデューティー比を目的デューティー比に変更した上で、その出力信号SOを出力することができる。

(もっと読む)

通信信号生成装置及び通信装置

【課題】集積回路の実装面積を抑えつつ通信信号の通信波形のリンギングを抑制する。

【解決手段】トランスミッタ130において、出力バッファ制御信号生成部131は、トランジスタ132a〜132d,133a〜133dをすべてオンにして第1通信線11及び第2通信線12に電流を流すことによりドミナントを表す通信信号を生成し、トランジスタ132a〜132d,133a〜133dをすべてオフにして第1通信線11及び第2通信線12に電流を流さないことによりレセッシブを表す通信信号を生成する。そして、出力バッファ制御信号生成部131は、ドミナントを表す通信信号の1ビット時間において、トランジスタ132a〜132d,133a〜133dを順にオフにして出力バッファ(第1のトランジスタ群132及び第2のトランジスタ群133)の各インピーダンスを徐々に高くする。

(もっと読む)

半導体装置及び電子機器

【課題】消費電力を低減することができる半導体装置及びそれを用いた電子機器を提供す

ることを課題とする。

【解決手段】本発明の半導体装置は、高電位電源から第1の電位が供給され、低電位電源

から第2の電位が供給され、入力ノードに第1の信号が入力されると、出力ノードから第

2の信号を出力する。本発明の半導体装置は、第2の信号の電位差を、第1の電位と第2

の電位の電位差よりも小さくすることにより、配線の充電と放電に伴う消費電力を低減す

ることができる。

(もっと読む)

レベルシフト回路

【課題】レベル変換における動作範囲を広くする。

【解決手段】第1の電位(VDD1)の波高値を有する入力パルス信号(VIN)を入力するCMOSインバータ回路(P1、N1)と、第1の電位よりも高電位となる第2の電位(VDD2)の電源で動作し、一端(ND1)をCMOSインバータ回路の出力端に接続し、他端から第2の電位の波高値を有し入力パルス信号と同相の出力パルス信号(VOUT)を出力するラッチ回路(INV1、P3)と、第1の電位以上かつ第2の電位未満の電源供給をCMOSインバータ回路に対して行う電源供給回路(P2、INV2)と、を備え、電源供給回路は、入力パルス信号が少なくとも接地レベルとなる場合に電源供給を制限するように機能する。

(もっと読む)

バッファ回路

【課題】出力の反射を抑制しつつスルーレートを高い自由度を持って調整可能なバッファ回路を提供する。

【解決手段】

複数の出力トランジスタPOA1〜POE1は、電源端子(電源電圧VCCQ)と出力端子DoutP1との間に電流経路を並列接続され導通することにより出力端子DoutP1の電圧を変化させる。ゲート制御用トランジスタTA1〜TE1は、接地端子Dgndと出力トランジスタPOA1〜POE1のゲートとの間、又は2つの出力トランジスタのゲートの間に電流経路を形成するように接続され、出力トランジスタにゲート電圧を与える。ゲート制御用トランジスタTA1〜TE1のゲートは、ゲート制御用トランジスタTA1〜TE1のソースの電圧が変化したときにゲート−ソース間の電位差が閾値電圧以上となって導通するよう、所定の電圧を与えられている。

(もっと読む)

半導体記憶装置および昇圧回路

【課題】回路面積の削減しつつ、消費電流やピーク電流の増大を抑制することが可能な半導体記憶装置を提供する。

【解決手段】昇圧回路は、第1ないし第4の整流素子と、第1ないし第4のMOSトランジスタと、第1ないし第4のキャパシタと、スイッチ回路と、を備える。スイッチ回路は、第1のMOSトランジスタの他端と第3の整流素子の一端との間の第1の接続点、および、第2のMOSトランジスタの他端と第4の整流素子の一端との間の第2の接続点に接続された低レベル端子と、第3のMOSトランジスタの他端、および、第4のMOSトランジスタの他端に接続された高レベル端子と、を有し、低レベル端子の電圧または高レベル端子の電圧を切り換えて、出力端子に出力するスイッチ回路と、を含む。

(もっと読む)

半導体装置

【課題】スタンバイ時のサブスレッショルドリーク電流およびゲートリーク電流を低減させ、スタンバイモードからの復帰時の貫通電流の発生を防ぐことのできる半導体装置を提供する。

【解決手段】クロックゲート信号Gにより出力レベルが固定されるNANDゲート1およびインバータ2〜6と高電位電源線VDDとの間に接続された高閾値のPMOSトランジスタPH1〜PH6、および低電位電源線VSSとの間に接続された高閾値のNMOSトランジスタNH1〜NH6のスイッチングを、スタンバイ制御信号SB1、SB2およびそれぞれの反転信号SB1N、SB2Nで制御する。

(もっと読む)

半導体装置

【課題】電源回路等を追加することなく、第1の電源電圧が低下してもダイナミックVTによる高速化の効果の低減を抑制できる半導体装置を提供する。

【解決手段】第1の回路は、第1の電源電圧を供給する第1の電源ラインと第1の電源電圧よりも低い第2の電源電圧を供給する第2の電源ライン間に接続された、トランジスタを備える。制御回路は、第1の電源ラインと第2の電源ライン間に接続され、上記トランジスタのバックゲートに第1の電源電圧と第2の電源電圧の電位差よりも振幅が大きい制御信号を供給する。

(もっと読む)

パルス出力回路、シフトレジスタ

【課題】薄膜トランジスタの特性劣化の程度を小さくし、回路内の誤動作を低減し、より確度の高い動作を保証する駆動回路を提供する。

【解決手段】シフトレジスタに設けられたパルス出力回路において、パルスの出力が行われない非選択期間、ゲート電極がオンするように浮遊状態となっているトランジスタのゲート電極が接続されたノードに対し、クロック信号がトランジスタのゲート電極に入力されるように設けることで、定期的に電位を供給する。また、ブートストラップ動作を行うトランジスタのゲートにゲートが固定電位に接続されたトランジスタを設ける。

(もっと読む)

低電流論理ゲート回路

本回路は、ゲート・ソース接合を有するEモードトランジスタ(E3,E4,E5)と、ゲート・ソース接合を有するDモードトランジスタ(D)と、Dモードトランジスタのソース(4)と信号出力(OUT)端として設けられるEモードトランジスタのドレイン(2)との間に電圧降下(E1,E2)を生じさせる構成要素と、Eモードトランジスタのドレイン(2)とDモードトランジスタのゲート(6)との間の接続ラインと、Eモードトランジスタのゲート(3,24,27)の信号入力(IN)端とを備える。Eモードトランジスタは、NAND及び/又はNOR論理回路として動作するように配置される。本回路は、低い電流を流すのみで、GaAsテクノロジーにおける論理回路を動作させることができる。  (もっと読む)

(もっと読む)

低電流インバータ回路

本回路は、ゲート・ソース接合を有するEモードトランジスタ(E3)と、ゲート・ソース接合を有するDモードトランジスタ(D)と、Dモードトランジスタのソース(4)とEモードトランジスタのドレイン(2)との間に電圧降下を生じさせる構成要素(E1、E2)と、Eモードトランジスタのドレイン(2)とDモードトランジスタのゲート(6)との間の接続ラインとを備える。Eモードトランジスタのゲート(3)は入力信号(IN)用に設けられ、Eモードトランジスタのドレイン(2)は出力信号(OUT)用に設けられる。本回路は、低電流を流すのみでGaAsテクノロジーにおける論理回路を動作させることができる。  (もっと読む)

(もっと読む)

半導体集積回路およびその動作方法

【課題】低高のしきい値電圧のトランジスタが混在する半導体集積回路で、電源電圧VDDの制御で速度制御を実行する際に各トランジスタの動作速度を適切に制御する。

【解決手段】半導体集積回路は、内部回路13、測定回路14、15、16を具備する。内部回路は低高のしきい値電圧のMOSトランジスタを含み、低しきい値電圧のトランジスタのばらつきは高しきい値電圧のトランジスタのばらつきより大きい。測定回路は低高のしきい値電圧のトランジスタが、ともに、高速の状態Fast、典型の状態Typical、低速の状態Slowのいずれかを検出する。高速の検出結果で小さな変化勾配β[V/σ]の低いレベルVDD−ΔVDDに、典型の検出結果で中間的なレベルVDD±0に、低速の検出結果で大きな変化勾配α[V/σ]の高いレベルVDD+ΔVDDに、電源電圧VDDが設定される。

(もっと読む)

1 - 20 / 98

[ Back to top ]