Fターム[5J056FF05]の内容

Fターム[5J056FF05]に分類される特許

1 - 20 / 28

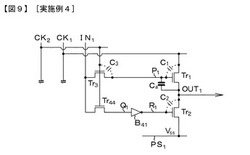

ブートストラップ回路

【課題】飛び込みの影響を軽減できるブートストラップ回路を提供する。

【解決手段】同一導電型の第1乃至第4TRから構成され、第1TRにおいて、一方のS/D領域は第2TRの一方のS/D領域に接続され、他方のS/D領域には、2相のクロックのうち一方のクロックが印加され、ゲート電極は、第3TRの一方のS/D領域に接続され、第2TRにおいて、他方のS/D領域は電圧供給線に接続され、第3TRにおいて、他方のS/D領域には入力信号が印加され、ゲート電極には他方のクロックが印加され、第1TRのゲート電極と第3TRの一方のS/D領域とは、第3TRがオフ状態になると浮遊状態となるノード部を構成し、第4TRにおいて、一方のS/D領域は、反転回路の入力側に接続されると共に、該反転回路の出力側と第2TRのゲート電極とが接続されており、他方のS/D領域は入力信号が印加され、ゲート電極には他方のクロックが印加される。

(もっと読む)

表示装置、表示モジュール及び電子機器

【課題】回路を構成するトランジスタ数を少なくし、且つレベルシフタを配置することな

くシフトレジスタとして正確に動作を行う半導体回路の提供することを課題とする。

【解決手段】第1端子が高電位電源に接続されたpチャネル型トランジスタと、第1端子

が低電位電源に接続されたnチャネル型トランジスタと、を含む回路群と、インバータ回

路と、をm段(mは任意の正の整数であり、m≧3)有し、第2n−1段目(nは任意の

整数であり、m≧2n≧2)の回路群の前記nチャネル型トランジスタのゲートにはクロ

ック信号が入力され、第2n段目(nは任意の整数であり、m≧2n≧2)の回路群の前

記nチャネル型トランジスタのゲートには反転クロック信号が入力される。

(もっと読む)

演算およびスリープ・モード中のデータ格納回路並びに方法

【課題】スリープ・モード中に信号を格納するための回路を提供する。

【解決手段】スリープ信号を受け取るスリープ信号入力と、クロック信号を受け取るクロック信号入力と、クロック信号でクロックされる複数のラッチと、クロック信号でクロックされるトライステート素子であって、トライステート素子は1つの入力に、少なくとも1つの格納ラッチが接続され、格納ラッチは複数のラッチの1つであり、トライステート素子は格納ラッチの入力を、予め定められたクロック信号値に応答して選択的に分離するトライステート素子とを含み、回路への電源供給が、スリープ信号に応答して、回路の少なくとも1部の電圧差が低減されて回路の部分の電源が遮断され、格納ラッチに掛かる電圧差が維持され、トライステート素子で受け取られるクロック信号が予め定められた値に保持されて、格納ラッチの入力が分離される。

(もっと読む)

クロック負昇圧回路

【課題】回路構成が簡易、小型でウェル・バイアス電圧の立ち上がり時間が短く、安定した負昇圧クロックを供給することが可能なクロック負昇圧回路を提供する。

【解決手段】クロック負昇圧回路部301、クロック負昇圧回路部302、クロック負昇圧回路部301、クロック負昇圧回路部302のウェル層上に設けられたNMOSトランジスタ107に電圧を供給するキャパシタ403、NMOSトランジスタ104を備え、クロック負昇圧回路部301が備えるNMOSトランジスタ104とキャパシタ403とを接続する電圧ライン303、クロック負昇圧回路部302が備える2つのNMOSトランジスタ104の出力を接続する電圧ライン303によってクロック負昇圧回路を提供する。

(もっと読む)

差動論理回路、分周回路、及び周波数シンセサイザ

【課題】動作電流を変えても直流出力電圧の変わらない差動論理回路及び分周回路、さらには、周波数シンセサイザにおける動作電流の調整方法を提供する。

【解決手段】複数対の差動論理信号を入力し論理演算を行ってその結果を一対の差動信号出力端子から出力する差動論理部と、差動論理部に電流を供給する電流源回路であって前記電流の大きさが制御可能な電流源回路と、差動信号出力端子に接続された負荷回路と、負荷回路に接続され、一対の差動信号出力端子の直流出力電圧が一定の電圧になるように負荷回路の負荷を制御する負荷制御回路と、を備える。

(もっと読む)

半導体装置

【課題】スイング領域を変換せずに、CML領域でスイングする信号の電源電圧レベルをシフトすることができる回路を提供する。

【解決手段】第1の電源電圧VDD1を電源として用い、第1のレベルを基準としてスイングするCMLクロックCML_TRANS_Pを受信して、そのスイング基準レベルを第2のレベルに切り換えて降圧CMLクロックCML_TRANS_Lとして出力するスイングレベル切換部220と、第2の電源電圧VDD2を電源として用い、スイングレベル切換部220から伝達される降圧CMLクロックCML_TRANS_LをバッファリングするCMLクロック伝達バッファリング部240と、第1の電源電圧VDD1を電源として用い、ソースクロックCML_INをバッファリングして、CMLクロックCML_TRANS_Pを生成した後、スイングレベル切換部220に提供するCMLクロック生成バッファリング部200とを備える。

(もっと読む)

半導体集積回路装置

【課題】電源遮断時にそれ以前の情報を保持する低消費電力モードにおいてその復帰を高速にする。その一つに従来のデータ保持型フリップフロップを用いることが考えられるが、そのためにセルを大きくする等の面積オーバーヘッドが生じるのは望ましくない。

【解決手段】電源遮断時のデータ保持のための電源線は一般の電源幹線よりも細い配線にて形成する。望ましくは、データ保持回路の電源を信号線扱いとして、自動配置配線時に配線することである。そのために、セルにはあらかじめ上記データ保持回路用電源のための端子を通常の信号線と同様に設けて設計しておく。[効果]セルに余分な電源線のレイアウトが不要となり省面積化が図られるとともに、既存の自動配置配線ツールにより設計が可能となる。

(もっと読む)

入力インターフェース回路

【課題】有効なセットアップ特性及びホールド特性を良好に確保することが可能な入力インターフェース回路を提供すること。

【解決手段】本発明に係る入力インターフェース回路100は、データが外部入力される信号端子に接続される入力初段回路と、外部入力されるクロックと、入力初段回路に含まれるラッチ回路3、4へのラッチタイミング信号とを同位相に調整する位相調整回路6と、を備える。位相調整回路6は、クロックと当該クロックから擬似する擬似遅延回路の出力との比較結果に基づいてクロックツリー回路7を通過してラッチ回路3、4へと供給されるラッチタイミング信号の遅延時間を調整する。

(もっと読む)

半導体集積回路

【課題】消費電力を削減するために、クロック反転信号を用いることなくクロック信号に同期してデータの転送および保持を行わせる。

【解決手段】記憶ノードM、MBを持つ状態保持回路F11において、Pチャンネル電界効果トランジスタM1、M2のゲートおよびNチャンネル電界効果トランジスタM3、M4のゲートにはクロック信号CKを入力し、Pチャンネル電界効果トランジスタM1を介してデータ反転信号DBを記憶ノードMBに印加させ、Pチャンネル電界効果トランジスタM2を介してデータ信号DBBを記憶ノードMに印加させ、Nチャンネル電界効果トランジスタM3を介して出力信号Q1を記憶ノードSに印加させ、Nチャンネル電界効果トランジスタM4を介して出力反転信号QB1を記憶ノードSBに印加させる。

(もっと読む)

半導体装置

【課題】従来のプログラマブルな半導体装置であるFPGAやMPLDはコストパフォーマンスが悪く、かつ長い信号線に対する配慮が不充分であった。

【解決手段】メモリと、アドレス−データ対を有する複数のMLUTから構成されるMLUTブロックにフリップフロップを内蔵した。また隣接するMLUT間の近距離配線には交互配置配線を導入し、隣接していないMLUT間の配線には専用の離間配線、更にはトーラス配線網を設けた。

(もっと読む)

同期出力を有する周波数分周器

【解決手段】周波数でクロック信号を分周し、優れた信号特性を有する差動信号を供給し得る分周器が記述される。1つの典型的な設計では、分周器はシングルエンド分周器及び同期回路を含む。シングルエンド分周器は、周波数でクロック信号を分割し、タイミングスキューを有する相補型信号である第1及び第2信号を供給する。同期回路は、クロック信号に基づき第1、第2信号をリサンプリングし、低減したタイミングスキューを有する差動信号を供給する。1つの典型的な設計では、同期回路は第1及び第2スイッチ、並びに第1及び第2インバータを含む。第1スイッチ及び第1インバータによって第1サンプリング−保持回路又は第1信号をリサンプリングする第1ラッチが形成される。第2スイッチ及び第2インバータによって、第2サンプリング−保持回路又は第2信号をリサンプリングする第2ラッチが形成される。 (もっと読む)

クロック生成回路

【課題】正常な差動クロック信号を生成することができるクロック生成回路を提供することを課題とする。

【解決手段】イネーブル端子にネゲート信号が入力される場合にはレベルが固定された第2の差動クロック信号を出力する入力バッファ回路(101)と、第2の差動クロック信号に同期して、第3の差動クロック信号を出力する第1のラッチ回路(102)と、第2の差動クロック信号の反転信号に同期して、第4の差動クロック信号を出力する第2のラッチ回路(103)と、第4の差動クロック信号をバッファリングし、第6の差動クロック信号を出力する第2の出力バッファ回路(105)と、第6の差動クロック信号が同相信号である場合には、入力バッファ回路のイネーブル端子にネゲート信号を出力する第1の異常モード検出器(112)とを有するクロック生成回路が提供される。

(もっと読む)

半導体装置

【課題】入力信号が有する2値の電位に関わらず、正常に動作させることが可能なデジタル回路の提案を課題とする。

【解決手段】半導体装置の一態様は、入力端子、容量素子、スイッチ、トランジスタ、配線、及び出力端子を有し、前記入力端子は、前記容量素子の第1の電極に電気的に接続され、前記配線は、前記スイッチを介して前記容量素子の第2の電極に電気的に接続され、前記トランジスタのゲートは、前記容量素子の第2の電極に電気的に接続され、前記トランジスタのソース又はドレインの一方は、前記配線に電気的に接続され、前記トランジスタのソース又はドレインの他方は、前記配線に電気的に接続されていることを特徴とする。

(もっと読む)

電子回路のブートストラップポイント電圧を低下する方法、及びその方法を用いた装置

【課題】電子回路のブートストラップポイントの電圧を低下させる方法とそれを用いた装置を提供する。

【解決手段】シフトレジスタ回路等の電子回路において、ブートストラップポイント電圧レベルを低下させる放電装置を提供する。この回路において、第1トランジスタは、導通の際、入力パルスを受信し、入力パルスを第2トランジスタのゲート端に伝送して、第二トランジスタを導通状態にする。このゲート端がいわゆるブートストラップポイントである。入力パルスを受信した時、出力パルスが第2トランジスタのドレイン/ソース端に生成される。出力パルスの時間周期において、第1トランジスタは非導通態で、且つ、ブートストラップポイントは高電圧レベルにあり、第1トランジスタに対し電圧を印加する。放電回路は、少なくとも一つのトランジスタから構成され、ブートストラップポイントに接続されて、出力パルス周期内の電圧レベルを低下させる。

(もっと読む)

スタック型差動信号送信回路

【課題】チャンネル当たりの電力散逸が減少されており、回路の複雑性が低く、内在的な帯域幅の制限が無く、データ又はクロックのエンコーディング無しで動作可能であり、信号受信器に関しての付加的な条件を課すことなしに動作可能であり、且つEMI及びその他のノイズ源に対しての高いロバストの耐久性を有する差動I/Oインタフェースを有する差動信号送信回路を実現する。

【解決手段】チャンネル間において信号電流を再使用することにより電力散逸を最小化させるために電源電極間においてスタック型関係で複数の差動信号送信回路が結合されている差動信号送信回路。

(もっと読む)

低電力モードにおける漏洩電力削減

【課題】スリープモードまたは停止中に、状態を保持しながら漏洩電力を最少とするシーケンス回路を提供する。

【解決手段】データ入力、データ出力、クロック信号入力およびクランプ信号入力を含むシーケンス回路とし、データ入力で受け取るデータ信号をシーケンス回路の中に、クロック信号入力で受け取られるクロック信号に応答してクロックを掛け、クロック信号に応答して、シーケンス回路からデータ出力にデータ信号を出力し、クランプ信号入力の予め定められた値に応答して、低電力モードに切り換え、回路内のシーケンス状態を保持しながらデータ出力を強制値に設定し、強制値は出力データ信号を受け取るように構成された組み合わせ回路からの漏洩電力を低減するように選択する。

(もっと読む)

クロックゲーテッド回路

【課題】放電部からファイティングノードへの不要な電荷の流入による電力消費の問題を解決しうるクロックゲーテッド回路を提供する。

【解決手段】クロックゲーテッド回路が開示されている。本発明のクロックゲーテッド回路はクロック信号受信部、放電部、電圧維持部、出力部及び遮断部を備え、クロック信号受信部はクロック信号が第1論理を有する区間で第1電圧をファイティングノードに印加する。放電部はイネーブル信号が活性化された区間でクロック信号が第1論理から第2論理に遷移する時、ファイティングノードから電荷を放電する。電圧維持部はファイティングノードを電源電圧または接地電圧に維持させ、出力部はファイティングノードの電圧の論理レベルを反転させてゲーテッドクロック信号として出力する。第1論理は論理ローで、第1電圧は電源電圧でありうる。遮断部は放電区間で電圧維持部によるファイティングノードへの電源電圧の供給を遮断する。

(もっと読む)

ラッチ回路及びそれを備えたフリップフロップ回路並びに論理回路

【課題】本発明は、外部から入力する外部信号に依存されずに出力信号をクリアできるクリア機能を備えたラッチ回路及びそれを備えたフリップフロップ回路並びに論理回路に関し、出力信号をクリアするクリア機能を備え、高速動作が可能なラッチ回路及びそれを備えたフリップフロップ回路並びに論理回路を提供することを目的とする。

【解決手段】ラッチ回路1は、入力部16に入力された制御信号CNTに基づいて、入力部2から入力された外部信号Dの出力/非出力を切り替える切替回路3と、切替回路3から出力された信号を入力信号として入力し、当該入力信号に基づいて出力した出力信号Qの論理レベルの状態を保持する状態保持回路5と、入力部18から入力されたクリア信号CLRに基づいて当該入力信号の論理レベルをクリアレベルにするクリア回路7とを有している。

(もっと読む)

論理回路

【課題】低電圧動作のために縦2段重ねとなされた論理回路において、クロック信号の正補のバランスが崩れても論理回路の正常動作が保証できるようにする。

【解決手段】第1の差動対(Q1、Q2)と第2の差動対(Q3、Q4)、第1、第2の差動対の共通ソース点にそれぞれ接続される電流源Q5、Q6、クロック正補信号がに入力される電流切替用トランジスタQ7、Q8を有する単位レジスタ回路において、更にクロック補信号CLKBが微弱となる場合に備えてトランジスタQ9が配備される。クロック補信号CLKBが微弱となった場合、X点にはクロック正信号CLKの逆相、すなわちクロック補信号と同相の信号成分が発生し、これを入力とするトランジスタQ9が動作することで、微弱なクロック補信号入力により未動作状態のQ8の動作を補償して、Q9が差動対Q3−Q4への電流供給切替を保証する。

(もっと読む)

オンダイターミネーション制御装置

【課題】本発明はオンダイターミネーション制御装置に関し、特に、ODT(On−Die Termination)とDLL(Delay Locked Loop)のディセーブル状態でクロック信号を制御し電流の無駄使いを抑えることのできるオンダイターミネーション制御装置を提供すること。

【解決手段】本発明のオンダイターミネーション制御装置は、モード設定に応じて状態が異なるようにするクロック制御信号を出力するモードレジスタセットと、前記クロック制御信号のアクティブ状態に応じて第1内部クロックと第1同期クロックを受信し、第2内部クロックと第2同期クロックを選択的に出力するクロック制御部と、ODT制御信号を受信し、前記第2内部クロックと前記第2同期クロックに同期して、オンダイターミネーションブロックの動作を制御するオンダイターミネーション制御部とを備える。

(もっと読む)

1 - 20 / 28

[ Back to top ]