Fターム[5J067CA36]の内容

Fターム[5J067CA36]に分類される特許

81 - 100 / 157

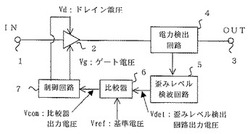

高周波増幅器

【課題】 高周波領域において動作する通信用増幅器の相互変調歪みの信号レベルを一定に保つことにより通信品質を確保し、また、環境温度が変化しても高効率で低消費電力動作が可能な高周波増幅器を提供する。

【解決手段】 高周波電力を入力する増幅器2と、増幅器2の出力ラインの分岐出力を検波出力とする歪レベル検波回路5と、この検波電圧と基準電圧とを比較する比較器6と、この比較器6の出力電圧が入力され、内部に比較器6の出力電圧に対応して増幅器2のゲート電極及びドレイン電極に対する供給電圧を定めるデータテーブルを書き込んだROMを有する制御回路7とを備えるようにし、ROMデ−タに基づき増幅器2のドレイン電圧とゲート電圧を制御するようにした。

(もっと読む)

高周波電力増幅回路

【課題】スタブ、共振回路を使用しないでF級動作を行う高周波電力増幅回路を提供する。

【解決手段】基本周波数f0の信号を増幅するトランジスタ48の出力端に、負荷として整合回路38と前記基本周波数f0を通過させる帯域通過フィルタ30sとの直列回路を備える高周波電力増幅回路20であって、前記直列回路に直列に接続される伝送線路36をさらに備え、伝送線路36の電気長が、トランジスタ48の出力端44からみて2f0である5.4[GHz]の周波数において負荷インピーダンスが短絡となり、3f0である8.1[GHz]の周波数において負荷インピーダンスが開放となるように設定する。

(もっと読む)

高周波装置、及び高周波機器

【課題】 従来のマイクロ波装置では損失が大きいため、これをマイクロ波機器に適用した場合、例えば低雑音増幅器では雑音指数が劣化し、高出力増幅器では出力、効率が低下する課題があった。

【解決手段】 一端どおしが付き合うように配置された2個の主線路3、4と、それぞれの主線路3、4の一端から対向する主線路側に向かって設けられた高インピーダンス線路8、7と、それぞれ高インピーダンス線路7、8の先端と対向する主線路間に装着されたキャパシタ5とで構成した。

(もっと読む)

高周波電力増幅器

【課題】高周波電力増幅器に関し、速やかに高効率動作を開始し、また、広帯域信号にも速やかに効率を落すことなく対応にする。

【解決手段】インダクタL1,L2とキャパシタC1,C2とから成る第1及び第2のタンク回路を、それぞれ、バランス型増幅器を構成する第1及び第2のトランジスタZ1,Z2に接続し、第1及び第2のトランジスタZ1,Z2のドレーン間に出力負荷抵抗R1を接続し、入力信号の極性を互いに反転した差動電圧信号を入力するバランス型増幅器に、両側のタンク回路に共通に、給電エネルギーを蓄積するインダクタL0を接続し、片側のタンク回路から非並衡にスイッチングトランジスタZ0を導通して、インダクタL0に給電エネルギーを蓄え、スイッチングトランジスタZ0をカットオフしたときに、該インダクタL0からバランス型増幅器給電が開始され、出力負荷抵抗R1から出力電力が立ち上がる。

(もっと読む)

ドハティ増幅回路

【課題】 従来のドハティ増幅回路では、AM−PM特性(振幅−位相特性)の変動が複雑であって、十分な歪補償を行うのが困難であるという問題点があり、本発明は、AM−PM特性を改善し、歪の小さいドハティ増幅回路を提供する。

【解決手段】 互いにAM−PM特性の異なる複数のドハティ増幅部を縦続接続したものであって、例えば、AM−PM特性が逆特性となるGaAsFETを用いた成るドハティ増幅部20と、LD−MOSFETを用いたドハティ増幅部30とを縦続接続したものであり、それぞれのドハティ増幅部で発生する位相変化を相殺して、全体として良好なAM−PM特性を実現し、歪を低減するドハティ増幅回路である。

(もっと読む)

ドハティ増幅器

【課題】簡単な構成で隣接チャネル漏洩電力を抑制しつつ高い効率を得ることができるドハティ増幅器を提供する。

【解決手段】第1電圧とこの第1電圧とは異なる第2電圧とを供給する定電圧源21,22と、増幅部とを備え、増幅部は、入力信号を分配する分配回路11と、定電圧源の第1電圧がドレイン−ソース間に印加され、分配回路により分配された一方の信号を常時増幅するキャリア増幅器1と、定電圧源の第2電圧がドレイン−ソース間に印加され、入力信号が所定レベル以上の場合に分配回路により分配された他方の信号を増幅するピーク増幅器2と、キャリア増幅器の出力とピーク増幅器の出力とが合成されて出力される出力端とを備える。

(もっと読む)

ドハティ増幅器

【課題】変化する入力電力やピーク/平均電力比に対して最適なバイアスを印加するドハティ増幅器を提供する。

【解決手段】アクティブ・バイアス回路では、平均電力検出手段22が入力信号の平均電力を示す電圧値を検出し、包絡線検出手段26が入力信号の包絡線を検出し、しきい値演算手段24が平均電力電圧値に応じて包絡線のしきい値を演算し、電圧制限手段32が包絡線を一定値以下に制限し、これにより、入力信号の平均電力に応じたバイアス電圧を印加する。また、ピークホールド手段27が包絡線の最大電圧値を保持し、差演算手段28が包絡線最大電圧値と平均電力電圧値との差を演算し、電圧制御増幅器30が演算された電圧値を制御電圧として増幅率を変化させて包絡線を増幅し、これにより、入力信号のピーク/平均電力比に応じたバイアス電圧を印加する。

(もっと読む)

電力増幅回路

【課題】Chirex合成器とF級増幅器とを組み合わせて、高効率な線形増幅器を実現する場合、補償リアクタンス成分がF級増幅器の高周波整合条件に悪影響を及ぼし、効率が低下する。

【解決手段】電力増幅器として機能するLINC方式増幅器100は、LINC信号分離回路10と、遅延器12と、移相器14と、電力増幅IC40と、を有している。また、電力増幅IC40は、整合回路32,34と、FET16,18と、伝送線路22,24と、伝送線路22に接続されたλ/8オープンスタブ26と、伝送線路24に接続された3λ/8オープンスタブ28と、を有している。

(もっと読む)

整合回路、マルチバンド増幅器

【課題】複数の周波数帯域の信号に対して効率的に動作する整合回路、及び、複数の周波数の信号を同時に効率良く増幅することができるマルチバンド増幅器を提供する。

【解決手段】2以上の周波数帯域の信号を増幅する増幅素子10と、周波数帯域ごとの信号に対してインピーダンス整合を行う整合回路40を備える。一般に、整合回路は、増幅素子よりも動作周波数の幅が狭い。しかし、本発明のように、分波回路20で分波した一方の信号(f1)に対してインピーダンス整合を行うように整合ブロック30を設計し、他方の信号(f2)に対してインピーダンス整合を行うように整合ブロック31を設計することにより、各整合ブロックを効率的に機能させることができる。その結果、高効率で、同時に2以上の周波数帯域の信号を処理する整合回路40、マルチバンド増幅器100を構成することができる。

(もっと読む)

増幅器

【課題】現実的なトランジスタを対象とした、より高効率で広帯域、かつ実装面積が小さく小形な増幅器を得る。

【解決手段】増幅用トランジスタ10と、増幅用トランジスタ10の出力端子に接続され、基本波周波数f0の整数倍となる複数の周波数において入力サセプタンスが発散する高調波反射用スタブ20と、一端が増幅用トランジスタ10の出力端子に高調波反射用スタブ20と並列に接続され、他端が負荷回路に接続され、増幅用トランジスタ10の出力アドミタンスと高調波反射用スタブの入力サセプタンスの和を、負荷回路のインピーダンス値にインピーダンス整合させる基本波整合回路30とを備え、高調波反射用スタブ20は、一端が増幅用トランジスタの出力端子に接続される1つの幹スタブT21と、幹スタブT21の他端に分岐して並列接続される複数の枝スタブT22、T23とを含む。

(もっと読む)

高周波電力増幅器

【課題】出力効率が高く広い周波数帯域において良好な歪み特性を有する高周波電力増幅器を提供する。

【解決手段】マルチフィンガー形のトランジスタで形成され、信号が入力されるゲートパッド30aと接地されるソースパッド30bと信号が出力されるドレインパッド30cとを有する単位FET30を複数有するFET素子12と、単位FET30のゲートパッド30aと接地端との間にシャント接続された直列共振回路32が複数個配設された高周波処理回路14とを備え、直列共振回路32の二つがFET素子12の動作周波数帯域に含まれる周波数の2次及びそれ以上の高調波であって互いに異なる共振周波数を有するものである。

(もっと読む)

安定化回路、高周波フィルタ

【課題】高周波回路において周波数変化率が高い素子を実現し、これを用いた安定化回路および高周波フィルタを提供する。

【解決手段】高周波回路の第1のノード5に接続された開放スタブT11、開放スタブT22の伝送線路の特性インピーダンスはそれぞれZ1、Z2であり、高周波回路の動作周波数fにおける位相定数はそれぞれβ1とβ2である。開放スタブT11と開放スタブT22の長さL1とL2はZ1×cot(β1×L1)=−Z2×cot(β2×L2)の関係式を満たす任意の組み合わせを用いる。抵抗R4の抵抗値は任意に設定可能であり、周波数f以外の周波数において高周波回路に与える損失の大きさを調整する。抵抗R4が第1のノード5における高周波信号インピーダンスよりも十分小さいかあるいは十分大きい場合は高周波回路に与える損失は小さくなり、抵抗Rが前記高周波信号インピーダンスに近い場合は損失が大きくなる。

(もっと読む)

合成器および増幅合成装置

【課題】2つの増幅器がそれぞれ出力する信号を合成すると共に増幅器の電力効率を高くすることが可能な合成器、およびそのような合成器を適用した装置を提供することを目的とする。

【解決手段】第1増幅器の出力端子に一方の端が接続される線状の第1線導体と、第2増幅器の出力端子に一方の端が接続される線状の第2線導体と、第1増幅器の出力端子に接続されない側の第1線導体の端と第2増幅器の出力端子に接続されない側の第2線導体の端との間に接続される先端導体と、第1線導体と第2線導体との間に接続される導電性部材と、を備え、第1増幅器が出力する信号と第2増幅器が出力する信号とを合成し、先端導体から出力する合成器であって、導電性部材が接続される位置が、第1増幅器および第2増幅器における電力損失に基づいて定められることを特徴とする。

(もっと読む)

高周波回路装置,高周波モジュール及び無線通信装置

【課題】基板内を伝搬するPPM漏洩波を減衰させて、電力損失の低減と回路動作特性の向上と異常発振の防止を図った高周波回路装置,高周波モジュール及び無線通信装置を提供する。

【解決手段】高周波回路装置は、スロット線路1,2とFET200とを誘電体基板100の表面側に備え、スロット線路1,2と非対称なPDTLを構成するスロット線路3,4とを裏面側に備える。接地された導体板5−1,5−2が誘電体基板100の両側面部に取り付けられ、導体板5−1(5−2)の上面部52が表面側導体101に、下面部53が裏面側導体102にそれぞれ接触して、表面側導体101と裏面側導体102とを導体板5−1(5−2)で短絡している。そして、誘電体基板100の基板端100a(100b)と導体板5−1(5−2)の起立部51との間に空隙55を画成し、基板端100a(100b)を開放している。

(もっと読む)

高周波用電力増幅器

【課題】負性抵抗の発生を防ぎつつ、所望の周波数帯域で入出力間を中和できる。

【解決手段】本発明による高周波用電力増幅器は、高周波信号が入力される入力端子4と、高周波信号に基づいた信号を出力する出力端子5とを有する3端子能動素子3と、入力端子4と出力端子5との間に設けられ、少なくとも1つの直列共振回路を形成する容量素子2及び伝送線路1とを備える。ここで、3端子能動素子3は、入力端子4と出力端子5間に帰還容量を有し、伝送線路1と帰還容量とは並列共振回路を形成する。又、伝送線路1は、直列共振回路の共振周波数である直列共振周波数fioにおいて、オープンスタブとして機能する。

(もっと読む)

電力増幅器

【課題】広い周波数帯において2次高調波の放射を抑制するとともに高効率動作することのできる電力増幅器を提供する。

【解決手段】出力整合回路12内に、短絡となる周波数の異なる2つのトラップ回路21および22を設け、そのうち、短絡となる周波数の高いトラップ回路21を電力増幅素子4に近い側に配置することで送信周波数帯の中心周波数の2倍の周波数より高い周波数帯をトラップしかつ電力増幅素子4の出力端からみたときの送信周波数帯の2倍の周波数帯の周波数における出力整合回路のインピーダンスを短絡に近い状態に保つとともに、短絡となる周波数の低いトラップ回路22によって送信周波数帯の中心周波数の2倍の周波数より低い周波数帯をトラップする。

(もっと読む)

高周波増幅器

【課題】広帯域な基本波整合を保ちつつ、高調波整合による高効率動作を提供することができる高周波増幅器を得る。

【解決手段】トランジスタチップ3と、トランジスタチップ3のドレイン側に直接接続される出力側プリマッチ基板4と、出力側プリマッチ基板4に接続され、出力整合のための出力整合高誘電率基板5とを設けた高周波増幅器であって、出力側プリマッチ基板4の誘電率が出力整合高誘電率基板5の誘電率よりも低く選ばれている。

(もっと読む)

LINC技術と組み合わされた出力ネットワーク

本発明は、Chireixのようなアウトフェージング技術と組み合わされた平衡型電力増幅器のネットワークに関する。本発明の目的はカレントモードクラスD(CMCD)又はクラスE/Fのような平衡型増幅器をLINCネットワークと組み合わせるための解決方法を提供することである。主な問題点として、いくつかの電力増幅器が平衡出力を有し、そして、LINCネットワークがシングルエンデッド型であるという点が挙げられる。その結果、さまざまなインピーダンスレベルで作動する高出力低損失変圧器を必要とすることになるが、セルラ周波数でこの変圧器を実現することは困難である。  (もっと読む)

(もっと読む)

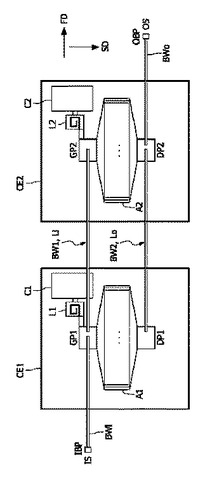

高出力集積RF増幅器

入力ボンド・パッド(IBP)と第1の方向(FD)に互いに変位された複数のセル(CE1、CE2)と出力ボンド・パッド(OBP)とをこの順序で第1の方向(FD)に備えた集積HF増幅器構造体。セル(CE1、CE2)の各々は入力パッド(GP1、GP2)とアクティブ領域(A1、A2)と出力パッド(DP1、DP2)とを有する増幅器を備える。アクティブ領域(A1、A2)は、入力パッド(GP1、GP2)と出力パッド(DP1、DP2)の間に配置され、入力パッド(GP1、GP2)とアクティブ領域(A1、A2)と出力パッド(DP1、DP2)は第1の方向(FD)に対してほぼ直角な第2の方向(SD)に互いに変位される。第1の回路網(N1)は、複数のセル(CE1、CE2)のうちの隣接するセルの入力パッド(GP1、GP2)を相互接続するための第1の相互接続手段(Li、Ci;Li1、Li2、Ci1)を備え、且つ第1の方向(FD)に延びる。第2の回路網(N2)は、複数のセル(CE1、CE2)のうちの隣接するセルの出力パッド(DP1、DP2)を相互接続するための第2の相互接続手段(Lo、Co;Lo1、Lo2、Co1)を備え、且つ第1の方向(FD)に延びる。第1の回路網(N1)及び第2の回路網(N2)は、すべての相互接続されたセル(CE1、CE2)について、出力ボンド・パッド(OBP)にて、入力ボンド・パッド(IBP)での同じ入力信号(IS)に対して等しい位相シフト及び振幅を有する出力信号(OS)を得るように構成される。特定のバイアス及び位相シフト条件において、構造体は出力バックオフでの効率が改善されたドハティ増幅器を実現する。  (もっと読む)

(もっと読む)

電力増幅器

【課題】F級電力増幅器の特徴である高効率を維持しつつ、線形性を実現できるようにする。

【解決手段】本発明においては、入力された高周波入力信号のレベルを検出する入力レベル検出回路と、A/Dコンバータと、前記入力されたレベル信号に応じて各々の振幅線分を増幅するための複数の増幅器のON/OFFを制御するCPUと、から構成され、

前記ONが選択された増幅器のみを増幅し、増幅された信号を1/4波長線路を通して、合成し、同調回路にて必要な成分のみ選択して、高周波出力として出力することを特徴としている。本発明を実施することにより、(1)非線形増幅器を使用するため消費電力が低減できる。(2)高効率が期待できる。(3)MTFB(Mean Time Between Failure:平均故障間隔)の向上が期待できる。(4)高効率のため、小型・軽量化が実現できる。という効果がある。

(もっと読む)

81 - 100 / 157

[ Back to top ]