Fターム[5J067FA16]の内容

Fターム[5J067FA16]に分類される特許

1 - 20 / 129

高周波増幅器

高周波増幅器

無線装置およびその製造方法

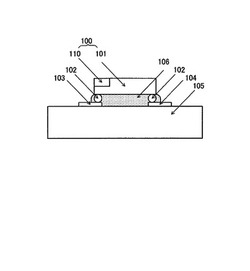

【課題】ICチップのプロセスばらつきによって高周波特性がばらついた場合でも、回路特性を最適化できるICチップを基板にフリップチップ実装する無線装置を提供する。

【解決手段】無線装置は、マイクロ波、ミリ波帯の電力増幅器用高周波ICチップ100、バンプ102、入力端子103、出力端子104、基板105、アンダーフィル106、プロセスばらつき検出部110を有する。プロセスばらつき検出部は、プロセスばらつきによる回路特性の変動量をモニタし、モニタされた回路特性の変動量を用いて、算出されたパラーメータを有するアンダーフィル106が、基板105とミリ波帯の電力増幅器用高周波ICチップ100との間に充填されることで、プロセスばらつき及びアンダーフィルの影響があっても、所望の回路特性が得られる無線装置を提供できる。

(もっと読む)

半導体パッケージ、及び半導体パッケージの製造方法

【課題】高周波電力増幅器の汎用性を確保しつつ、低コスト化及び小型化が可能な半導体パッケージ(P)を提供すること。

【解決手段】接地導体(131)と、前記接地導体(131)の上部に設けられた2層の高周波基板(130)と、上層の前記高周波基板(130)を挟むように設けられた一対の導体(134)と、を含む、半導体パッケージ(P)が提供される。また、この半導体パッケージ(P)を含む高周波電力増幅器(100)が提供される。

(もっと読む)

ドハティ増幅装置及び通信装置

【課題】ドハティ増幅装置の効率低下を防止する。

【解決手段】ドハティ増幅装置は、メインアンプを構成するメインアンプデバイス1と、ピークアンプを構成するピークアンプデバイス2と、メインアンプデバイス1及びピークアンプ2が実装された基板15とを有している。メインアンプデバイス1は、第1デバイス本体1c、第1入力端子1a、及び、第1出力端子1bを備え、第1入力端子1a及び第1出力端子1bが第1デバイス本体1cを挟んで対向して配置されている。ピークアンプデバイス2は、第2デバイス本体2c、第2入力端子2a、及び、第2出力端子2bを備え、第2入力端子2a及び第2出力端子2bが第2デバイス本体2cを挟んで対向して配置されている。ピークアンプデバイス2は、メインアンプデバイス1の位置に対して、メインアンプデバイス1の第1入力端子から第1出力端子に向かう入出力方向Dsにずれた位置に、実装されている。

(もっと読む)

半導体電力増幅器

【課題】ビアホールの数を少なくしてもループ発振などの特性劣化が生じにくい半導体電力増幅器を提供する。

【解決手段】半導体電力増幅器は、ゲート電極Gと、ドレイン電極Dと、前記ゲートフィンガー電極に対向して配置されるソースフィンガー電極横手方向の両サイドに引き出される2つのソース電極Sと、を有するユニットFETと、前記ユニットFETが、前記ソース電極間を結ぶ略直線方向に複数個並列配置され、隣り合うユニットFET間に存在する2つのソース電極の両方を共通して高周波グランド面と接続する第1の接地インダクタンス値を有する第1のビアホール18Kと、隣り合うユニットFETが存在しない側のソース電極上に配置され、接地インダクタンスを等しくするために前記高周波グランド面に接続する第2の接地インダクタンス値を有する第2のビアホール18Dと、を有する。

(もっと読む)

高調波抑圧回路

【課題】高周波動作と、低コスト化および小型化とを両立させることが可能な高調波抑圧回路を得ること。

【解決手段】基本波の1/8波長の長さを有し、一端が入力端16aを形成し、他端が出力端16bを形成する主線路10と、一端が主線路10の入力端16aに接続された基本波の1/4波長の長さを有する第1の線路11aと、第1の線路11aの他端に一端が接続された抵抗体14および基本波の1/4波長の長さを有する第1のオープンスタブ12aと、抵抗体14の他端に接続された基本波の1/8波長の長さを有する第2のオープンスタブ13aと、一端が主線路10の出力端16bに接続された基本波の1/4波長の長さを有する第2の線路11bと、第2の線路11bの他端に接続された基本波の1/4波長の長さを有する第3のオープンスタブ12bおよび基本波の1/8波長の長さを有する第4のオープンスタブ13bと、を備える。

(もっと読む)

半導体装置

【課題】差分周波数Δfが数百MHzにおいても高周波半導体チップのドレイン端面の電圧が平滑化された半導体装置を提供する。

【解決手段】高周波半導体チップと、高周波半導体チップの入力側に配置された入力側分布回路と、高周波半導体チップの出力側に配置された出力側分布回路と、入力側分布回路に接続された高周波入力端子と、出力側分布回路に接続された高周波出力端子と、高周波半導体チップのドレイン端子電極近傍に配置された平滑化キャパシタとを備え、高周波半導体チップと、入力側分布回路と、出力側分布回路と、平滑化キャパシタとが1つのパッケージに収納されたことを特徴とする半導体装置。

(もっと読む)

モジュール

【課題】 平衡型増幅器の性能を損なわず、小型のモジュールを提供すること、他の回路機能とともに複合して無線通信装置の高周波回路部を構成可能なモジュールを提供することを目的とする。

【解決手段】

絶縁体層と導体パターンとを含む多層基板に、一対の増幅器の入力側に第1ハイブリッド回路を出力側に第2ハイブリッド回路を有する平衡型増幅器を構成したモジュールで、 積層方向に連なる複数のビアホールでなるビアホール群を縦列して構成されたシールドによって、前記第1ハイブリッド回路と前記第2ハイブリッド回路とを区画した。

(もっと読む)

電力合成器

【課題】 電力合成器の横寸法を低減しつつ、横寸法の低減に伴う特性劣化を防止する。

【解決手段】 入力側から第1線路、折返し線路、第2線路、直線線路が接続される直列回路を構成し、入力側が入力端子に接続される第1インピーダンス変成器と、第1インピーダンス変成器と同構成の第2インピーダンス変成器と、第1及び第2インピーダンス変成器とループを構成するアイソレーション回路と、第1及び第2インピーダンス変成器が共有する出力接点と出力端子との間に配置される出力インピーダンス変成器とを有する電力合成器であって、第1線路と第2線路は互いに平行に配置され、ループの横縦アスペクト比が1より小さく、第1線路の線幅を第1折返し線路の線幅より狭くして入力信号位相を90度回転し、アイソレーション回路で入力インピーダンスと整合し、出力インピーダンス変成器で出力インピーダンスと整合する。

(もっと読む)

2段のマイクロ波のE級電力増幅器

【課題】より広い周波数範囲で同時的な高電力と高電力付加効率(PAE)をもたらす改良されたE級増幅器を提供する。

【解決手段】2段のE級の高電力増幅器100は駆動装置段102、E級段間整合ネットワーク(ISMN)104、負荷回路を使用する高電力段106を含んでいる。負荷回路はスイッチングモード回路の出力に結合されている直列の誘導性−容量性ネットワークと、スイッチングモード回路の出力に結合されているキャパシタンスを提供するための回路を含んでいる。

(もっと読む)

可変整合回路

【課題】所望の数の周波数帯で動作する可変整合回路に必要な構成回路素子数を減らす。

【解決手段】伝送線路11Lに、第1の線路スタブSB1と、2つのスイッチSW1, SW2の一端を入力端から順次間隔L1, L2, L3をあけてそれぞれ接続し、2つのスイッチの他端は第2の線路スタブSB2接続し、第1及び第2線路スタブは開放端あるいは短絡端を有し、スイッチSW1, SW2のON,OFFの組み合わせにより4つの周波数帯での整合を選択可能にされている。

(もっと読む)

高周波増幅器及び整合回路

【課題】全てのトランジスタに対して最適かつ等位相で高調波を反射させ、高い出力かつ高い効率で動作する高周波増幅器を得る。

【解決手段】FET1Aのドレイン(D)に一端が接続された四角形線路部5A、FET1BのDに一端が接続された四角形線路部5B、並びに四角形線路部5A及び5Bの他端を接続する弓形線路部5Cを有する伝送線路5と、四角形線路部5A及び5Bの間に配置された伝送線路6Bと、四角形線路部5Aに対して伝送線路6Bと反対側に配置された伝送線路6Aと、四角形線路部5Bに対して伝送線路6Bと反対側に配置された伝送線路6Cとを備え、伝送線路6A、6B、6Cの電気長は、高調波の1/4波長であり、伝送線路6A、6B、6Cのそれぞれのビアホール7A、7B、7Cは、伝送線路6A、6B、6Cの一端に接続される。

(もっと読む)

半導体装置

【課題】差分周波数Δfが数百MHzにおいても高周波半導体チップのドレイン端面の電圧が平滑化された半導体装置を提供する。

【解決手段】高周波半導体チップと、高周波半導体チップの入力側に配置された入力整合回路と、高周波半導体チップの出力側に配置された出力整合回路と、入力整合回路に接続された高周波入力端子と、出力整合回路に接続された高周波出力端子と、高周波半導体チップに接続される平滑化キャパシタ用端子とを備え、高周波半導体チップと、入力整合回路と、出力整合回路とが1つのパッケージに収納された半導体装置。

(もっと読む)

電子回路

【課題】分布定数線路の長さの誤差または製造ばらつき等による特性変動を抑制すること。

【解決手段】制御端子と、第1端子と、第2端子と、を有する第1トランジスタT1と、制御端子に前記第1トランジスタの第2端子が接続し、第2端子に直流電源が接続される第2トランジスタT2と、前記第2トランジスタの第1端子から前記第1トランジスタの第2端子に直流電流を供給する、互いに独立した配線からなる複数の直流経路11、12と、前記複数の直流経路内にそれぞれ直列に設けられた分布定数線路L11、L12と、を具備する電子回路。

(もっと読む)

高周波半導体装置

【課題】パッケージの電極部と整合回路との間で生ずるインピーダンスの不整合を改善することができる高周波半導体装置を提供すること。

【解決手段】入出力用電極部16、17を有するパッケージ11とパッケージ内部に載置された半導体チップ12と半導体チップおよび入出力用電極部にそれぞれ電気的に接続された入出力整合回路パターン22、31と、入出力整合回路パターンと入出力用電極部16、17とをそれぞれ接続する第1、第5の導体線23、32と、入力整合回路パターン22および出力整合回路パターン31上にそれぞれ載置された小型チップコンデンサ24、33と、これらの小型チップコンデンサと入力用電極部とを接続する第2、第6の導体線25、34と、を具備し、小型チップコンデンサは、小型チップコンデンサの容量および第2、第6の導体線25、34のインダクタンスによって決定される共振周波数が、使用周波数帯に含まれる容量を有する。

(もっと読む)

III族窒化物系高電子移動度トランジスタを含む低雑音増幅器

【課題】高い入力電力耐性と、低い雑音指数の両者を達成する低雑音増幅器を提供すること。

【解決手段】低雑音増幅器は、第一のIII族窒化物系トランジスタと、第一のIII族窒化物系トランジスタに結合された第二のIII族窒化物系トランジスタとを含んでいる。第一のIII族窒化物系トランジスタは、入力信号に対する第一増幅段を提供するように構成され、第二のIII族窒化物系トランジスタは、入力信号に対する第二増幅段を提供するように構成される。

(もっと読む)

電力合成分配器および電力合成分配器を用いた送信機

【課題】複数の増幅器のうちの一部が故障しても、電力合成分配器の分配損、合成損を最小とする。

【解決手段】複数の並列接続された第1の分岐側端子(113、114)と1つの第1の合成側端子(115)が第1の電力合成点(116)を介して接続された第1の分岐回路(127)と、複数の並列接続された第2の分岐側端子(133、134)と1つの第2の合成側端子(135)が第2の電力合成点(136)を介して接続された第2の分岐回路(137)とを有し、第1の合成側端子と複数の第2の分岐側端子が接続された電力合成あるいは電力分配を行う電力合成分配器において、第1の電力合成点から第2の電力合成点までの長さが1/2波長の整数倍である。

(もっと読む)

バイアス回路

【課題】バイアス回路を組み込んだ通信機器や電子機器の小型化を促進させるため、1つのチップにて構成することができるバイアス回路を提供する。

【解決手段】RFチョークとバイパスコンデンサとを有するバイアス回路において、少なくとも下面もしくはその内部にグランド電極40が形成された誘電体基板30と、前記誘電体基板30の表面に形成された入力端子32及び出力端子34と、前記誘電体基板30内もしくは表面に形成され、一端が前記入力端子32に接続され、且つ、他端が前記出力端子34に接続され、前記RFチョークを形成するRFチョーク形成電極36と、前記誘電体基板30内に、前記グランド電極40に対向して形成され、且つ、一端が前記出力端子34に接続され、前記バイパスコンデンサを形成するためのコンデンサ形成電極38とを有する。

(もっと読む)

高周波増幅器

【課題】高利得の増幅器であっても空間ループを原因とした異常発振を確実に防止することができる高周波増幅器を提供する。

【解決手段】誘電体基板2上に形成されたマイクロストリップ線路3と、このマイクロストリップ線路3に接続された増幅素子1と、誘電体基板2上に載置された増幅素子1を収容する収容部7aが形成された金属筐体7と、この金属筐体7の収容部7aに嵌合するとともに、増幅素子1と対向する面側に第1の溝部8bが形成された金属体8と、金属体8の第1の溝部8bに嵌挿される第1の導電性ラバー9とを備え、金属筐体7の収容部7aに金属体8を嵌合した時、第1の導電性ラバー9が誘電体基板2上に実装されている増幅素子1を押圧して、増幅素子1上の空間ループを遮断する。

(もっと読む)

1 - 20 / 129

[ Back to top ]