Fターム[5J067HA33]の内容

Fターム[5J067HA33]の下位に属するFターム

Fターム[5J067HA33]に分類される特許

1 - 20 / 138

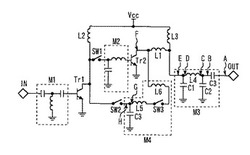

電力増幅器

【課題】素子ばらつきや周波数特性に対して鈍感であり低損失な電力増幅器を得る。

【解決手段】入力端子INから入力した入力信号を増幅素子Tr1が増幅する。増幅素子Tr1の出力信号を増幅素子Tr2が増幅する。増幅素子Tr2の出力信号は出力端子OUTから出力される。増幅素子Tr2の出力と出力端子OUTとの間に整合回路M3が接続されている。増幅素子Tr1の出力と増幅素子Tr2の入力との間にスイッチSW1が接続されている。増幅素子Tr1の出力にスイッチSW2の一端が接続されている。整合回路M4の一端がスイッチSW2の他端に接続され、整合回路M4の他端が増幅素子Tr2の出力に直接に接続されている。

(もっと読む)

高周波増幅器

【課題】ユニットセルの組み合わせで形成されるすべてのループ発振を抑制することができる高周波増幅器を提供する。

【解決手段】実施の形態に係る高周波増幅器は、入力された信号を分配する分配回路と、分配回路が分配した信号を増幅するFETセルと、分配回路とFETセルのゲート端子との間に直列に接続され、キャパシタと抵抗との並列回路から構成される安定化回路と、FETセルが増幅した信号を合成する合成回路とを備え、安定化回路をFETセルごとに配置する。

(もっと読む)

増幅装置、無線通信装置、及び負荷変動器

【課題】新規な負荷変動器を提供する。

【解決手段】 可変位相器を用いた負荷変動器3001であって、前記可変位相器は、信号が入力される第1ポートP1と、信号が出力される第2ポートP2と、第1可変インピーダンス3021が接続される第3ポートP3と、第2可変インピーダンス3022が接続される第4ポートP4と、を備えている。可変位相器は、第1ポートP1から入力された信号の位相が第1可変インピーダンス2021及び第2可変インピーダンス3022によって変化するものである。第1可変インピーダンス3021及び第2可変インピーダンス3022は、前記第1可変インピーダンスと第2可変インピーダンスとの間のインピーダンス差を調整可能に設けられている。インピーダンス差の調整によって、第1ポートP1及び第2ポートP2間の負荷が変動する。

(もっと読む)

F級増幅回路及びこれを用いた送信装置

【課題】基本波周波数の異なる複数の入力信号が入力する場合でも、各基本周波数に応じた高周波処理が行えるようにする。

【解決手段】 基本角周波数の異なる複数の信号をF級増幅し、該基本角周波数の信号成分及び、その高調波の信号成分を含んだ信号を出力するF級増幅器と、F級増幅器の後段に設けられて、当該F級増幅器に寄生する寄生回路のインピーダンスを取り込んで回路設定されることにより、信号の直流成分及び偶数次高調波の信号成分に対しては短絡状態とし、奇数次高調波の信号成分に対しては開放状態となる高調波処理部と、高調波処理部の後段に設けられて、高調波の信号成分に対しては短絡状態にする短絡部と、を備える。

(もっと読む)

能動回路

【課題】2倍波処理回路の動作の阻害を防ぎ、動作効率の劣化を防ぐ能動回路を得る。

【解決手段】バイアス回路5において、基本波整合回路4の出力側に接続され、基本波周波数成分を全通過させ、2倍波周波数成分を反射するフィルタ回路51と、基本波整合回路4の出力側とフィルタ回路51との間に接続され、基本波周波数で並列共振し、2倍波周波数に対してほぼ純抵抗となる2倍波吸収回路52と、2倍波吸収回路52に接続され、バイアス電圧を供給するバイアス電圧供給回路53とを備えた。

バイアス回路5において、2倍波周波数成分を高周波トランジスタ2側に反射させずに吸収することによって、2倍波処理回路3とバイアス回路5とで並列共振を起こすことがなく、その結果、2倍波処理回路3の動作の阻害を防ぎ、動作効率の劣化を防ぐ能動回路を得ることができる。

(もっと読む)

半導体装置

【課題】差分周波数Δfが数百MHzにおいても高周波半導体チップのドレイン端面の電圧が平滑化された半導体装置を提供する。

【解決手段】高周波半導体チップと、高周波半導体チップの入力側に配置された入力側分布回路と、高周波半導体チップの出力側に配置された出力側分布回路と、入力側分布回路に接続された高周波入力端子と、出力側分布回路に接続された高周波出力端子と、高周波半導体チップのドレイン端子電極近傍に配置された平滑化キャパシタとを備え、高周波半導体チップと、入力側分布回路と、出力側分布回路と、平滑化キャパシタとが1つのパッケージに収納されたことを特徴とする半導体装置。

(もっと読む)

広帯域マイクロ波増幅器

【課題】クラスEのHPAが広い帯域幅にわたって同時に高いPAE及び電力を維持することを可能にする。

【解決手段】スイッチングモード電力増幅器の出力に結合されたシャント誘導素子と、前記増幅器の前記出力に結合されている直列の誘導素子と、前記直列の誘導素子に結合されている直列の容量素子とを含む構成とした。

(もっと読む)

高調波処理回路、高周波増幅器及び高周波発振器

【課題】広帯域での2倍波整合を取れず、高効率化できる周波数範囲が狭い。

【解決手段】伝送線路2から構成されるメイン線路と、抵抗6と伝送線路5、7とが直列接続された回路から構成され、メイン線路と並列接続されたサブ線路と、一端がメイン線路とサブ線路との接続点に接続されたオープンスタブ3、4とを含んで構成される。

(もっと読む)

分配回路、送信用フェーズドアレイアンテナ回路、合成回路及び受信用フェーズドアレイアンテナ回路

【課題】入力信号を複数の信号に低損失で分配することができる分配回路を提供することを課題とする。

【解決手段】分配回路は、信号入力ノードに直列接続される複数のインダクタ(401〜40n+1)と、入力容量を有する入力端子及び出力端子を有し、前記複数のインダクタのそれぞれの間に前記入力端子が接続され、前記入力端子に入力される信号を増幅して前記出力端子から出力する複数の増幅素子(421〜42n)と、前記複数の増幅素子の出力端子と複数の信号出力ノードとの間にそれぞれ接続される複数の整合回路(431〜43n)とを有する。

(もっと読む)

電力合成器

【課題】 電力合成器の横寸法を低減しつつ、横寸法の低減に伴う特性劣化を防止する。

【解決手段】 入力側から第1線路、折返し線路、第2線路、直線線路が接続される直列回路を構成し、入力側が入力端子に接続される第1インピーダンス変成器と、第1インピーダンス変成器と同構成の第2インピーダンス変成器と、第1及び第2インピーダンス変成器とループを構成するアイソレーション回路と、第1及び第2インピーダンス変成器が共有する出力接点と出力端子との間に配置される出力インピーダンス変成器とを有する電力合成器であって、第1線路と第2線路は互いに平行に配置され、ループの横縦アスペクト比が1より小さく、第1線路の線幅を第1折返し線路の線幅より狭くして入力信号位相を90度回転し、アイソレーション回路で入力インピーダンスと整合し、出力インピーダンス変成器で出力インピーダンスと整合する。

(もっと読む)

高周波増幅器及び整合回路

【課題】全てのトランジスタに対して最適かつ等位相で高調波を反射させ、高い出力かつ高い効率で動作する高周波増幅器を得る。

【解決手段】FET1Aのドレイン(D)に一端が接続された四角形線路部5A、FET1BのDに一端が接続された四角形線路部5B、並びに四角形線路部5A及び5Bの他端を接続する弓形線路部5Cを有する伝送線路5と、四角形線路部5A及び5Bの間に配置された伝送線路6Bと、四角形線路部5Aに対して伝送線路6Bと反対側に配置された伝送線路6Aと、四角形線路部5Bに対して伝送線路6Bと反対側に配置された伝送線路6Cとを備え、伝送線路6A、6B、6Cの電気長は、高調波の1/4波長であり、伝送線路6A、6B、6Cのそれぞれのビアホール7A、7B、7Cは、伝送線路6A、6B、6Cの一端に接続される。

(もっと読む)

電力増幅器用バイアス回路

【課題】差分周波数Δfが数百MHzにおいても電力増幅器用バイアス回路のリップル電圧ΔVが抑制されてバイアス回路電圧が平滑化され、マイクロ波/ミリ波/サブミリ波帯の高周波に適用可能な電力増幅器用バイアス回路を提供する。

【解決手段】電力増幅器の出力側整合伝送線路のバイアス回路接続点に接続された第1ボンディングワイヤと、第1ボンディングワイヤの終端に接続された第2ボンディングワイヤと、第1ボンディングワイヤの終端に接続されたオープンスタブ伝送線路と、第2ボンディングワイヤの終端に接続されたバイパスリザバーキャパシタとを備える電力増幅器用バイアス回路。

(もっと読む)

高周波半導体装置

【課題】パッケージの電極部と整合回路との間で生ずるインピーダンスの不整合を改善することができる高周波半導体装置を提供すること。

【解決手段】入出力用電極部16、17を有するパッケージ11とパッケージ内部に載置された半導体チップ12と半導体チップおよび入出力用電極部にそれぞれ電気的に接続された入出力整合回路パターン22、31と、入出力整合回路パターンと入出力用電極部16、17とをそれぞれ接続する第1、第5の導体線23、32と、入力整合回路パターン22および出力整合回路パターン31上にそれぞれ載置された小型チップコンデンサ24、33と、これらの小型チップコンデンサと入力用電極部とを接続する第2、第6の導体線25、34と、を具備し、小型チップコンデンサは、小型チップコンデンサの容量および第2、第6の導体線25、34のインダクタンスによって決定される共振周波数が、使用周波数帯に含まれる容量を有する。

(もっと読む)

非常に高効率のフレキシブルな進行波増幅器

【課題】 非常に高効率のフレキシブルな進行波増幅器を提供する。

【解決手段】 カソード、ヘリックス、RF入力部、RF出力部、および複数のコレクタを備える進行波管(226)と、

前記進行波管(226)に電源および電極分極を与える電子電力調整器と

を少なくとも備える進行波管増幅器であって、

前記電子電力調整器が、データバスによって送られる制御コマンドにより、ヘリックス・カソード間電圧およびコレクタ電圧を調節することを可能にするフレキシビリティ制御手段(24)を備える、進行波管増幅器。

(もっと読む)

不均等入力電力分割を用いた増加されたバックオフ能力および電力付加効率を持つNウェイRF電力増幅器回路

【課題】RF電力増幅器の高効率動作

【解決手段】入力電力は分割され、不均等にキャリア増幅器および複数のピーク増幅器に供給されることによって、増加された電力負荷効率(PAE)および直線性を実現できる。それぞれのピーク増幅器は、キャリア増幅器へ提供される入力信号レベルより高い入力信号レベルを提供される。ピーク増幅器は、均等電力分割を用いて達成されえるよりも、より効率的にRF信号によって持ち上げられえ、よってスレッショルド近くにトランジスタのトランスコンダクタンス特性を補償し、同じ効率についてのバックオフ能力を増し、または同じバックオフ点における直線性を改善しえる。

(もっと読む)

アナログ回路

【課題】高い歩留りを得ながらゲートスロープを抑制することができるアナログ回路を提供する。

【解決手段】アナログ回路には、発振トランジスタ27と、発振トランジスタ27に対する負性抵抗を変更する負性抵抗変更回路と、が設けられている。負性抵抗変更回路には、可変抵抗回路及び可変容量回路が含まれている。可変抵抗回路には、抵抗体29、抵抗体31及びトランジスタ(スイッチ)35が含まれ、可変容量回路には、キャパシタ30及び可変容量ダイオード36が含まれている。

(もっと読む)

高周波多段能動回路

【課題】シャントの寄生キャパシタンス成分を相殺することができ、高域周波数帯における特性劣化を抑圧することができる高周波多段能動回路を得る。

【解決手段】高周波多段能動回路の段間インピーダンス整合回路20として、誘電体基板21上において一対の長さ1/4波長未満のくし型の導体電極パターンを対向して形成されるインターデジタルキャパシタを含み、かつこのインターデジタルキャパシタのくし型電極23a、23bの要部に誘導性スタブを接続し、かつこの誘導性スタブを介して能動デバイス10、30へのバイアス電圧を印加した。

(もっと読む)

高周波回路

【課題】低周波発振と高周波発振とを共に抑制することができる高周波回路を提供する。

【解決手段】高周波回路は、複数のトランジスタ12、複数の入出力整合回路14−1,14−2、複数の抵抗体18、低周波発振抑制回路17を含む。複数のトランジスタは、半導体基板11上に並列に配列形成される。複数の入出力整合回路は、それぞれ第1の絶縁基板13−1上、第2の絶縁基板13−2上に、複数のトランジスタにそれぞれ接続されて設けられている。低周波発振抑制回路は、所望の周波数帯域を透過帯域として有し、並列に配列形成された複数のトランジスタのうち、両側のトランジスタのゲート端子に接続される。複数の抵抗体は、複数の入出力整合回路間のうち、トランジスタに最も近い位置に形成されるとともに、透過帯域の最も低い周波数の発振に対して低周波発振抑制回路を作用させることが可能な長さで、複数の入出力整合回路間に形成される。

(もっと読む)

III族窒化物系高電子移動度トランジスタを含む低雑音増幅器

【課題】高い入力電力耐性と、低い雑音指数の両者を達成する低雑音増幅器を提供すること。

【解決手段】低雑音増幅器は、第一のIII族窒化物系トランジスタと、第一のIII族窒化物系トランジスタに結合された第二のIII族窒化物系トランジスタとを含んでいる。第一のIII族窒化物系トランジスタは、入力信号に対する第一増幅段を提供するように構成され、第二のIII族窒化物系トランジスタは、入力信号に対する第二増幅段を提供するように構成される。

(もっと読む)

バイアス回路

【課題】バイアス回路を組み込んだ通信機器や電子機器の小型化を促進させるため、1つのチップにて構成することができるバイアス回路を提供する。

【解決手段】RFチョークとバイパスコンデンサとを有するバイアス回路において、少なくとも下面もしくはその内部にグランド電極40が形成された誘電体基板30と、前記誘電体基板30の表面に形成された入力端子32及び出力端子34と、前記誘電体基板30内もしくは表面に形成され、一端が前記入力端子32に接続され、且つ、他端が前記出力端子34に接続され、前記RFチョークを形成するRFチョーク形成電極36と、前記誘電体基板30内に、前記グランド電極40に対向して形成され、且つ、一端が前記出力端子34に接続され、前記バイパスコンデンサを形成するためのコンデンサ形成電極38とを有する。

(もっと読む)

1 - 20 / 138

[ Back to top ]