Fターム[5J067QA04]の内容

Fターム[5J067QA04]に分類される特許

1 - 20 / 108

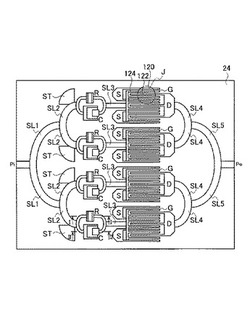

高周波増幅器

【課題】ユニットセルの組み合わせで形成されるすべてのループ発振を抑制することができる高周波増幅器を提供する。

【解決手段】実施の形態に係る高周波増幅器は、入力された信号を分配する分配回路と、分配回路が分配した信号を増幅するFETセルと、分配回路とFETセルのゲート端子との間に直列に接続され、キャパシタと抵抗との並列回路から構成される安定化回路と、FETセルが増幅した信号を合成する合成回路とを備え、安定化回路をFETセルごとに配置する。

(もっと読む)

半導体パッケージ、及び半導体パッケージの製造方法

【課題】高周波電力増幅器の汎用性を確保しつつ、低コスト化及び小型化が可能な半導体パッケージ(P)を提供すること。

【解決手段】接地導体(131)と、前記接地導体(131)の上部に設けられた2層の高周波基板(130)と、上層の前記高周波基板(130)を挟むように設けられた一対の導体(134)と、を含む、半導体パッケージ(P)が提供される。また、この半導体パッケージ(P)を含む高周波電力増幅器(100)が提供される。

(もっと読む)

電力増幅回路

【課題】電力増幅回路の周波数特性を広帯域化する。

【解決手段】それぞれが互いに異なる周波数(f1−fn)で整合が取られた差動プッシュプル増幅器(PA1−PAn)の出力を、二次インダクタ(L12−Ln2)で共通に合成して出力する。各差動プッシュプル増幅器は、差動信号入力端子にぞれぞれ接続される増幅器対で構成され、差動プッシュプル増幅器の出力にはキャパシタ(C1−Cn)とインダクタ(L11−L1n)の並列共振回路を接続し、共振周波数を変更して整合周波数を調整する。

(もっと読む)

ドハティ増幅装置及び通信装置

【課題】ドハティ増幅装置の効率低下を防止する。

【解決手段】ドハティ増幅装置は、メインアンプを構成するメインアンプデバイス1と、ピークアンプを構成するピークアンプデバイス2と、メインアンプデバイス1及びピークアンプ2が実装された基板15とを有している。メインアンプデバイス1は、第1デバイス本体1c、第1入力端子1a、及び、第1出力端子1bを備え、第1入力端子1a及び第1出力端子1bが第1デバイス本体1cを挟んで対向して配置されている。ピークアンプデバイス2は、第2デバイス本体2c、第2入力端子2a、及び、第2出力端子2bを備え、第2入力端子2a及び第2出力端子2bが第2デバイス本体2cを挟んで対向して配置されている。ピークアンプデバイス2は、メインアンプデバイス1の位置に対して、メインアンプデバイス1の第1入力端子から第1出力端子に向かう入出力方向Dsにずれた位置に、実装されている。

(もっと読む)

半導体装置

【課題】差分周波数Δfが数百MHzにおいても高周波半導体チップのドレイン端面の電圧が平滑化された半導体装置を提供する。

【解決手段】高周波半導体チップと、高周波半導体チップの入力側に配置された入力側分布回路と、高周波半導体チップの出力側に配置された出力側分布回路と、入力側分布回路に接続された高周波入力端子と、出力側分布回路に接続された高周波出力端子と、高周波半導体チップのドレイン端子電極近傍に配置された平滑化キャパシタとを備え、高周波半導体チップと、入力側分布回路と、出力側分布回路と、平滑化キャパシタとが1つのパッケージに収納されたことを特徴とする半導体装置。

(もっと読む)

モジュール

【課題】 平衡型増幅器の性能を損なわず、小型のモジュールを提供すること、他の回路機能とともに複合して無線通信装置の高周波回路部を構成可能なモジュールを提供することを目的とする。

【解決手段】

絶縁体層と導体パターンとを含む多層基板に、一対の増幅器の入力側に第1ハイブリッド回路を出力側に第2ハイブリッド回路を有する平衡型増幅器を構成したモジュールで、 積層方向に連なる複数のビアホールでなるビアホール群を縦列して構成されたシールドによって、前記第1ハイブリッド回路と前記第2ハイブリッド回路とを区画した。

(もっと読む)

高周波増幅器及び整合回路

【課題】全てのトランジスタに対して最適かつ等位相で高調波を反射させ、高い出力かつ高い効率で動作する高周波増幅器を得る。

【解決手段】FET1Aのドレイン(D)に一端が接続された四角形線路部5A、FET1BのDに一端が接続された四角形線路部5B、並びに四角形線路部5A及び5Bの他端を接続する弓形線路部5Cを有する伝送線路5と、四角形線路部5A及び5Bの間に配置された伝送線路6Bと、四角形線路部5Aに対して伝送線路6Bと反対側に配置された伝送線路6Aと、四角形線路部5Bに対して伝送線路6Bと反対側に配置された伝送線路6Cとを備え、伝送線路6A、6B、6Cの電気長は、高調波の1/4波長であり、伝送線路6A、6B、6Cのそれぞれのビアホール7A、7B、7Cは、伝送線路6A、6B、6Cの一端に接続される。

(もっと読む)

半導体装置

【課題】差分周波数Δfが数百MHzにおいても高周波半導体チップのドレイン端面の電圧が平滑化された半導体装置を提供する。

【解決手段】高周波半導体チップと、高周波半導体チップの入力側に配置された入力整合回路と、高周波半導体チップの出力側に配置された出力整合回路と、入力整合回路に接続された高周波入力端子と、出力整合回路に接続された高周波出力端子と、高周波半導体チップに接続される平滑化キャパシタ用端子とを備え、高周波半導体チップと、入力整合回路と、出力整合回路とが1つのパッケージに収納された半導体装置。

(もっと読む)

高周波処理回路

【課題】発振抑制用の抵抗を備えながら高周波処理による高効率化を図る。

【解決手段】分配された高周波信号を伝送線路14a,14bの一端の入力部13a,13bに供給し、伝送線路14aは直列接続された伝送線路15aを介して被増幅用高周波信号として出力部16aから次段の増幅用トランジスタに供給する。伝送線路14bは直列接続された伝送線路15bを介して被増幅用高周波信号として出力部16bから次段の増幅用トランジスタに供給する。伝送線路14a,15aの接続点Paに一端を接続したスタブ19aと伝送線路14b,15bの接続点Pbに一端を接続したスタブ19bとの間に発振抑制用の抵抗R1を介挿接続した。接続点Pa,Pbの電位差がない場合は、抵抗R1が見えない状態となり、スタブ19a,19bは高周波信号処理の効率化に寄与し、抵抗R1はセルA,B間のループ発振の抑制させることが可能となる。

(もっと読む)

高周波回路

【課題】低周波発振と高周波発振とを共に抑制することができる高周波回路を提供する。

【解決手段】高周波回路は、複数のトランジスタ12、複数の入出力整合回路14−1,14−2、複数の抵抗体18、低周波発振抑制回路17を含む。複数のトランジスタは、半導体基板11上に並列に配列形成される。複数の入出力整合回路は、それぞれ第1の絶縁基板13−1上、第2の絶縁基板13−2上に、複数のトランジスタにそれぞれ接続されて設けられている。低周波発振抑制回路は、所望の周波数帯域を透過帯域として有し、並列に配列形成された複数のトランジスタのうち、両側のトランジスタのゲート端子に接続される。複数の抵抗体は、複数の入出力整合回路間のうち、トランジスタに最も近い位置に形成されるとともに、透過帯域の最も低い周波数の発振に対して低周波発振抑制回路を作用させることが可能な長さで、複数の入出力整合回路間に形成される。

(もっと読む)

高周波モジュールおよびその動作方法

【課題】高温通電時にはバイアスジャンプを回避し、実運用時には外部電源を製品によらず共通化し、かつ端子数を削減する。

【解決手段】半導体装置24と、入力整合回路17と、出力整合回路18と、運用時用ゲートバイアス回路70と、運用時用ゲートバイアス回路70に接続された運用時用ゲートバイアス端子41aと、入力整合回路17に接続された高周波入力端子兼高温動作時用ゲートバイアス端子21aと、出力整合回路18に接続されたドレインバイアス回路80と、ドレインバイアス回路80に接続されたドレインバイアス端子41bと、出力整合回路18に接続された高周波出力端子21bとを備え、1つのパッケージに収納された高周波モジュール1およびその動作方法。

(もっと読む)

高周波モジュール

【課題】高温通電時には、バイアスジャンプを回避することができ、実運用時には、外部電源を製品によらず共通化することができる。

【解決手段】半導体装置24と、入力整合回路17と、出力整合回路18と、入力整合回路17に接続された高温動作用ゲートバイアス回路60および運用時用ゲートバイアス回路70と、高温動作用ゲートバイアス回路60に接続された高温動作用ゲートバイアス端子31aと、運用時用ゲートバイアス回路70に接続された運用時用ゲートバイアス端子41aと、入力整合回路17に接続された高周波入力端子21aと、出力整合回路18に接続されたドレインバイアス回路80と、ドレインバイアス回路80に接続されたドレインバイアス端子41bと、出力整合回路18に接続された高周波出力端子21bとを備え、1つのパッケージに収納された高周波モジュール1。

(もっと読む)

バイアス回路

【課題】バイアス回路を組み込んだ通信機器や電子機器の小型化を促進させるため、1つのチップにて構成することができるバイアス回路を提供する。

【解決手段】RFチョークとバイパスコンデンサとを有するバイアス回路において、少なくとも下面もしくはその内部にグランド電極40が形成された誘電体基板30と、前記誘電体基板30の表面に形成された入力端子32及び出力端子34と、前記誘電体基板30内もしくは表面に形成され、一端が前記入力端子32に接続され、且つ、他端が前記出力端子34に接続され、前記RFチョークを形成するRFチョーク形成電極36と、前記誘電体基板30内に、前記グランド電極40に対向して形成され、且つ、一端が前記出力端子34に接続され、前記バイパスコンデンサを形成するためのコンデンサ形成電極38とを有する。

(もっと読む)

ドハティ増幅器及び高周波伝送線路

【課題】インピーダンス変換の特性を低損失で容易に調整し、高周波大電力への耐用性が高く、小型化を実現するドハティ増幅器及び高周波伝送線路を提供する。

【解決手段】誘電体101は、厚さHAとHBの2層からなり、基板を構成する。2層の誘電体101の間には電極層102が積層されている。また、誘電体101の一面には、マイクロストリップ線路103が配設され、他面がグランド(GND)に接地されている。電極層102とGNDとはスイッチ104を介して接続されており、制御部105がスイッチ104を制御して、電極層102とGNDとの接続と開放を切り替える。

(もっと読む)

インピーダンス変換器、集積回路装置、増幅器および通信機モジュール

【課題】小型で伝送損失の少ないインピーダンス変換器、集積回路装置を実現する。

【解決手段】集積回路装置は、インピーダンス変換器15と、集積回路11A,11Bとを有し、インピーダンス変換器15は、第1の誘電率を有する第1の基板21の上方に設けられ、第1のインピーダンスを有する第1の伝送線路22A,22Bと、第1の誘電率より高い誘電率を有する第2の基板31の上方に設けられ、第1の伝送線路22A,22Bと電気的に接続され、第1のインピーダンスよりも低い特性インピーダンスを有する第2の伝送線路32AA,32ABおよび第3の伝送線路32BA,32BBと、第2の伝送線路32AA,32ABと第3の伝送線路32BA,32BBとの間に接続される抵抗35A,35Bとを有し、集積回路11A,11Bは、第2の伝送線路32AA,32ABおよび第3の伝送線路32BA,32BBと電気的に接続される。

(もっと読む)

バイアス回路

【課題】 不要波の出力を抑制することのできる小型なバイアス回路を得ることを目的とする。

【解決手段】 半導体素子3に電力を供給するバイアス回路において、インダクタ5及びキャパシタ6が直列に接続された直列回路と、直列回路に並列に接続されて並列回路を構成するインダクタ7と、接地されたキャパシタ8とインダクタ7との間に接続され、外部から電力が供給されるバイアス端子9を備えて、直列回路および並列回路の共振により、半導体素子3の不要波を除去し所望の周波数のみを伝達する。

(もっと読む)

高周波増幅器

【課題】本発明は、整合条件を変更するための制御回路を必要とせずに、複数の周波数帯で利用可能となる簡素な構成の高周波増幅器を提供することを目的とする。

【解決手段】パッケージ基板と、該パッケージ基板の表面に設置された増幅能動素子と、該増幅能動素子と接続されて高周波信号を伝送する伝送線路とを有する。そして、一端が該伝送線路にシャント接続されたSMD部品と、該SMD部品の他端と接続され一部が該パッケージ基板の裏面に露出するSMD部品用端子と、該伝送線路のうち該増幅能動素子と接続された部分と反対側の端部と接続され、一部が該パッケージ基板の裏面に露出する外部端子とを備えたことを特徴とする。

(もっと読む)

信号合成分配回路、電力増幅器および信号合成分配回路の製造方法

【課題】 簡単な構造で枝回路間の位相ずれによる利得低下を防止可能な信号合成分配回路を提供する。

【解決手段】 本発明の信号合成分配回路10は、基板11に、信号合成点または信号分配点14を有する複数の枝回路12a、12bおよび12cが配線され、前記複数の枝回路の少なくとも1本の枝回路12bが、他の枝回路12aおよび12cと異なる線路長であり、前記異なる線路長の枝回路12bの一部または全部15が、前記基板11中に配線されていることを特徴とする。

(もっと読む)

電力増幅装置

【課題】トランスを用いて複数の増幅器対の出力を合成する電力増幅装置において、各増幅器対の差動動作のずれによって生じる出力の低下を抑制する。

【解決手段】電力増幅装置110は、基板上に全体で環状に設けられた複数の一次インダクタ7,8と、複数の増幅器対3〜6と、二次インダクタ9と、接続配線10とを備える。各増幅器対は、対応の一次インダクタの両端に接続され、差動入力信号として与えられた一対の第1および第2の信号IN(+),IN(−)をそれぞれ増幅して対応の一次インダクタに出力する。二次インダクタ9は、複数の一次インダクタ7,8に隣接して環状に設けられ、各一次インダクタで合成された第1および第2の信号の合成信号をさらに合成して出力する。接続配線10は、基板上で複数の一次インダクタ7,8の内側に設けられ、各一次インダクタの中点MP1,MP2を互いに電気的に接続する。

(もっと読む)

高出力増幅器

【課題】基板やレイアウトの制限がある場合においても、実現可能なレイアウトで広帯域に出力整合することが可能な高出力増幅器を得る。

【解決手段】入力端子1に入力される高周波信号を整合する入力整合回路4と、入力整合回路4で整合された高周波信号を増幅させる増幅素子3と、増幅素子3で増幅された高調波信号の出力インピーダンスを、出力端子2の特性インピーダンスに整合する出力整合回路7,8と、増幅素子3と出力整合回路7,8とを接続する出力ワイヤ6とを備え、出力ワイヤ6のワイヤ長を、増幅素子3の出力容量を打ち消すインダクタ成分が得られる長さに略々設定した高出力増幅器である。

(もっと読む)

1 - 20 / 108

[ Back to top ]