Fターム[5J067TA06]の内容

Fターム[5J067TA06]に分類される特許

1 - 20 / 20

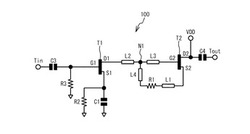

電子回路

【課題】、高出力動作が可能なカレントリユース電子回路を提供すること。

【解決手段】第1端子、第2端子および制御端子を有し、前記第1端子が接地された第1トランジスタT1と、第1端子、第2端子および制御端子を有し、前記制御端子に前記第1トランジスタの第2端子が接続され、前記第1端子が前記第1トランジスタの前記第2端子と高周波的に接続され、前記第2端子に直流電源が接続される第2トランジスタT2と、前記第1トランジスタの第2端子と前記第2トランジスタの制御端子との間のノードに一端が接続され、他端が前記第2トランジスタの第1端子に接続された第1抵抗R1と、を具備した電子回路。

(もっと読む)

パルス電力増幅装置

【課題】熱時定数による増幅利得の時間的な変化を補償でき、良好な直線性を有するパルス増幅装置を提供する。

【解決手段】パルス電力増幅装置10は、高周波信号を変調するパルス信号を入力され、前記パルス信号を入力され第1の増幅器の熱時定数に対応する時定数を有する第1の微分回路と、前記パルス信号を入力され第2の増幅器の熱時定数に対応する時定数を有する第2の微分回路と、励振回路及び最終段増幅器の入力側の負バイアス端子に供給される負バイアス電圧を出力する負バイアス電源18と、この負バイアス電源の出力する負バイアス電圧に前記第1の微分回路の出力を加算して前記第1の増幅器の入力側の負バイアス端子に供給する第1の加算回路と、前記負バイアス電源の出力する負バイアス電圧に前記第2の微分回路の出力を加算して前記第2の増幅器の入力側の負バイアス端子に供給する第2の加算回路と、を有する。

(もっと読む)

光変調器駆動回路

【課題】分布定数型増幅器を用いた光変調器の駆動回路であって、光変調器からの光出力の立ち上がり時間や立ち下がり時間を短くし得る駆動回路を提供する。

【解決手段】光変調器駆動回路は、複数の第1の非反転増幅器及び反転増幅器を備える。第1の非反転増幅器は、入力端と出力端との間に設けられている。第1の非反転増幅器はそれぞれ、入力端からの入力信号を固有の遅延時間で受け、出力端において第1の遅延時間で出力信号を与える。反転増幅器は、入力端と出力端との間に設けられている。反転増幅器は、入力信号を受け、出力端において第1の遅延時間より大きい第2の遅延時間で出力信号を与える。

(もっと読む)

増幅回路

【課題】広い入力レベル範囲にわたって高い効率を実現することが可能な増幅回路を提供する。

【解決手段】増幅回路101において、入力側高調波整合回路3および出力側高調波整合回路4により、トランジスタTRの制御電極から前段側を見たインピーダンスのうち基本周波数の高調波に対するインピーダンスと、トランジスタTRの導通電極から後段側を見たインピーダンスのうち基本周波数の高調波に対するインピーダンスとが、それぞれ、対象信号のレベルが異なる条件下において整合されている。

(もっと読む)

電力増幅器

【課題】異なる周波数、出力電力または変調方式において動作可能な電力増幅器および通信機器を提供できる。

【解決手段】入力端子および出力端子を有する第1増幅器PA2と、入力端子および出力端子を有する受動回路PC3と、単極端子と、2つの多投端子とを有する第1スイッチSW2と、を備えた電力増幅器であって、該第1スイッチSW2の該多投端子の一方は、該第1増幅器PA201の該入力端子に接続されており、該第1スイッチSW2の該多投端子の他方は、該受動回路PC3の該入力端子に接続されている。

(もっと読む)

電力増幅器

【課題】パルス増幅動作時間の近傍において不要な信号の送出を制限できる化合物半導体デバイスを使用した電力増幅器を提供する。

【解決手段】電力増幅器100は、電力増幅する高周波増幅素子11への電源を電源制御トランジスタ21が遮断する。放電用トランジスタ31は、電源制御トランジスタ21による電源遮断に同期して電源制御トランジスタ21及び高周波増幅素子11に残留する電荷を放電する。

(もっと読む)

高周波増幅装置

【課題】入力信号が過大レベルになっても半導体増幅素子に機能破壊が生じないようにした高周波増幅装置を提供すること。

【解決手段】FET101を用いた高周波増幅装置において、FET101対する電源電流Iの供給ラインに直列にパワーサーミスタ131を設け、入力信号のレベルの増加による電源電流Iの急激な増加に対する抑制機能がパワーサーミスタ131の電圧降下により与えられるようにしたもの。

(もっと読む)

電力増幅装置

【課題】

トランジスタを高効率動作させるために流通角を狭くする方法がある。しかしながら、高い入力電力によりトランジスタのゲート−ドレイン間に高い電位差が発生する。その結果、出力電力はトランジスタのゲート−ドレイン間耐圧により制限される。また、高い入力電力を得るためには、高出力ドライバ増幅器が必要となり、電力増幅装置全体の効率は低下する。

課題は高い入力電力による増幅手段の耐圧の問題を緩和し、また、高い電力を与えるためのドライバ増幅器の電力消費を低減し、高出力・高効率電力装置を提供することである。

【解決手段】

解決手段として、増幅手段の入力信号に基本波に対して同相の3倍波を重畳し、入力信号の波高率(最大値/実効値)を高め、入力電力を高めることなく狭流通角動作を実現する。

(もっと読む)

増幅器

【課題】J級動作をする増幅器において、電圧波形と電流波形の重なりを小さくする。

【解決手段】電界効果トランジスタ部と、そのドレインとソースとの間に接続された容量性インピーダンス部とを有してEJ級動作を行う増幅器であって、容量性インピーダンス部よりも後段に位置するように、ドレインに接続されたインダクタと、このインダクタを介して容量性インピーダンス部に並列接続されたキャパシタとを備えたものにおいて、インダクタは、マイクロストリップ基板208上に形成されたマイクロストリップライン209によって所定のインダクタンスを確保するものであり、その基本波周波数でのインピーダンスが、容量性インピーダンス部のインピーダンス以上の値に設定されているように構成する。

(もっと読む)

電力増幅器

【課題】特別な信号源の搭載を不要にして、回路の簡単化を図ることができるとともに、タイミングの調整精度を高めて、高効率化と低歪み化を実現することができるようにする。

【解決手段】RF電力増幅トランジスタ2により増幅されたRF信号の電力を検波する電力検波装置7と、電力検波装置7により検波されたRF信号の電力から、RF電力増幅トランジスタ2に対するRF信号と制御信号AFに対応するドレイン電圧信号の入力タイミングのずれを検出する位相制御装置8とを設け、入力タイミングのずれの検出結果に応じて制御信号AFの位相を調整して、入力タイミングのずれを解消する。

(もっと読む)

電源装置及び高周波回路システム

【課題】進行波管の通常動作時における最大ゲインの低下を招くことなく、安価な汎用部品を用いて、ヘリックス電圧及びコレクタ電圧の立ち上がり時にヘリックスに流れる電流を低減できる電源装置及びそれを備えた高周波回路システムを提供する。

【解決手段】へリックス電極とアノード電極間に接続されたツェナーダイオードと、ツェナーダイオードのカソードとアノード間を短絡または開放するトランジスタと、フォトトランジスタによりトランジスタをオン/オフするフォトカプラと、フォトカプラのフォトダイオードに対して直流電圧を供給または遮断するための第1のスイッチと、フォトダイオードに供給する直流電圧が印加されるコンデンサと、予め第1のスイッチをオンにしてフォトカプラ及びコンデンサに直流電圧を印加しておき、ヘリックス電圧の投入と同時に第1のスイッチをオフさせる制御部とを有する。

(もっと読む)

高周波増幅回路とこれを有する無線通信装置

【課題】 電源電圧が変動しても効率の低下を緩和することができ、しかも、製造時の歩留まりを向上し得るエンベロープトラッキング法に基づく高周波増幅回路を提供する。

【解決手段】 本発明の高周波増幅回路12aは、マイクロ波帯の高周波の入力信号が入力される半導体増幅素子21と、入力信号の包絡線の変動に追随する電源電圧を半導体増幅素子21に印加する電源回路22と、半導体増幅素子21の出力側に接続された出力整合回路24と、電源電圧が変動しても半導体増幅素子21の効率が最大となるように当該出力整合回路24のインピーダンスを調整するインピーダンス調整部とを備えている。

(もっと読む)

高周波電力増幅器

【課題】出力整合回路のインピーダンス可変素子を、構成が簡単で実装が容易な出力電力検出器により制御した高周波電力増幅器を提供する。

【解決手段】負荷インピーダンスを構成する整合回路30中の可変容量ダイオードを制御する情報源として、FET16の消費電流Ipを電圧降下によりモニタ電圧Vpとして抵抗器20により検出し、検出したモニタ電圧Vpに応じた制御電圧Vcにより整合回路30に設けられた可変容量ダイオードのインピーダンスであるキャパシタンスを電力効率が大きくなるように変化させているので、出力高周波電力に応じて電力効率が増加するように負荷インピーダンスを変化させることができる。抵抗器20は構成が簡単で又電源側に挿入しているので実装が容易である。

(もっと読む)

高周波電力増幅器

【課題】高周波電力増幅器に関し、速やかに高効率動作を開始し、また、広帯域信号にも速やかに効率を落すことなく対応にする。

【解決手段】インダクタL1,L2とキャパシタC1,C2とから成る第1及び第2のタンク回路を、それぞれ、バランス型増幅器を構成する第1及び第2のトランジスタZ1,Z2に接続し、第1及び第2のトランジスタZ1,Z2のドレーン間に出力負荷抵抗R1を接続し、入力信号の極性を互いに反転した差動電圧信号を入力するバランス型増幅器に、両側のタンク回路に共通に、給電エネルギーを蓄積するインダクタL0を接続し、片側のタンク回路から非並衡にスイッチングトランジスタZ0を導通して、インダクタL0に給電エネルギーを蓄え、スイッチングトランジスタZ0をカットオフしたときに、該インダクタL0からバランス型増幅器給電が開始され、出力負荷抵抗R1から出力電力が立ち上がる。

(もっと読む)

高周波電力増幅装置

【課題】インピーダンスの調整および切替えを容易に行い、これらの機能を有する小型高性能の高周波増幅装置を提供する。

【解決手段】1個または複数の高周波増幅素子を含む第一の半導体チップと、1個または複数の高周波整合回路素子および1個または複数のスイッチ素子を含む第二の半導体チップからモジュール等の高周波増幅装置を構成する。第二の半導体チップは高周波増幅素子の整合回路を有している。さらに、第二の半導体チップが、容量および容量と直列または並列に接続されたスイッチ素子からなる回路を含んでおり、スイッチ素子のオンまたはオフにより容量が整合回路の一部として接続、非接続の状態となるような切替えを行う。

(もっと読む)

カスコード接続回路

【課題】 利得、出力電力及び効率を劣化させることなく動作の安定性を向上させることができるカスコード接続回路を得る。

【解決手段】 2つの電解効果型トランジスタ(以下、「FET」という。)がカスコード接続されたカスコード接続回路であって、ソース端子が接地された第1のFETと、ソース端子が第1のFETのドレイン端子に接続された第2のFETと、第1のFETのソース端子と第2のFETのゲート端子との間に直列接続された第1の抵抗及び第1のコンデンサとを備え、第1の抵抗の抵抗値と第1のコンデンサの容量値との積が、動作周波数に対応する周期の0.1倍以下である。

(もっと読む)

ドハティ型増幅器

【課題】 電力効率をより高めたドハティ型増幅器を提供する。

【解決手段】 平均電力増幅器及びピーク電力増幅器へ共通の電源電圧を供給する第1の直流電源と、変調波信号のピーク振幅よりも高い直流電圧を生成する第2の直流電源と、変調波信号の電力の一部を分岐して出力する方向性結合器と、方向性結合器の出力信号から変調波信号の振幅エンベロープを電圧信号として出力する振幅エンベロープ検出回路と、振幅エンベロープ検出回路から出力された電圧信号のうち、所定のしきい値電圧を越える電圧信号を出力する比較器と、第2の直流電源から出力された直流電圧を比較器から出力された電圧信号で振幅変調し、ピーク電力増幅器へ供給する電圧変調器と、平均電力増幅器及びピーク電力増幅器へ供給する変調波信号を、振幅エンベロープ検出回路、比較器及び前記電圧変調器の処理による遅れに合わせて遅延させる遅延回路とを有する構成とする。

(もっと読む)

電力増幅器およびそれを用いた送信機

【課題】 ドハーティ型電力増幅器の出力電力合成回路の電気長を可変にし、マルチバンドまたは広帯域に対して高電力付加効率を図る。

【解決手段】 キャリアアンプAmp1とピークアンプAmp2との入力側に、90度位相遅延電力分配部PSPDを接続し、出力側に可変電気長電力合成部VTL2を接続する。搬送波信号RFsの搬送波周波数帯域に応じて、その搬送波周波数帯域の中心周波数に対して可変電気長電力合成部VTL2の電気長がほぼ90度になるように、可変電気長電力合成部VTL2の制御端子Ctrlから制御信号Sigを印加することにより調整する。

(もっと読む)

ミリメートル波用途の電力増幅器の実施のための回路及び方法

【課題】 ミリメートル波用途のための電力増幅器の実装のための回路及び方法を提供すること。

【解決手段】 ミリメートル波周波数において、能動スイッチング・デバイスとしてBJTのベース(バイポーラ接合型トランジスタ)を用いる、高効率なスイッチ・モード電力増幅器を実装するための回路及び方法が提供される。より詳細には、BJTスイッチング・デバイスを備えた電力増幅器を駆動して、ミリメートル波の周波数(例えば、60GHz)で高効率スイッチ・モード(例えば、E級)動作を達成するための回路及び方法が提供される。

(もっと読む)

高周波増幅装置

【課題】 送信信号のスロット数が変わった場合にABクラスで増幅動作していても歪み特性を悪化させることが少ない高周波増幅装置を提供する。

【解決手段】 この発明の高周波増幅装置には、増幅素子のMOS-FET101が配置されている。そのドレインDにはストリップライン112による整合パターンを介してドレイン電源が供給され、ソースにはソース電圧が印加されている。そして、整合パターンとドレイン電源を接続するライン上にあって、前記高周波信号で整合パターン側からドレイン電源側を見た場合にオープン状態に見える位置に配置された第1のコンデンサ107を有するとともに、ビート成分を最小にさせる位置で整合パターンに配置された第2のコンデンサ113を有する。第2のコンデンサは、第1のコンデンサと協働して、整合パターンに現れるビート成分を最小にするので、MOS-FETのドレイン電流は安定し、出力に現れる歪み成分は少なくなる。

(もっと読む)

1 - 20 / 20

[ Back to top ]