Fターム[5J079FB13]の内容

電気機械共振器を用いた発振回路 (23,106) | 回路要素 (2,263) | 同調回路 (17)

Fターム[5J079FB13]に分類される特許

1 - 17 / 17

発振器

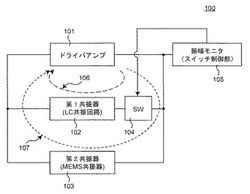

【課題】消費電流を増大させることなしに高速起動可能なMEMS発振器の提供。

【解決手段】ドライバアンプと、LC共振回路を備える第1共振器と、MEMS共振器を備える第2共振器と、接続および開放を切り換え可能なスイッチ回路と、スイッチ回路を制御するスイッチ制御部と、を有するMEMS発振器であって、ドライバアンプ、第1共振器、および、スイッチ回路は、ドライバアンプの出力信号の少なくとも一部をドライバアンプへ帰還させる第1閉ループ回路を形成し、ドライバアンプ、および、第2共振器は、第1閉ループ回路とは別の、ドライバアンプの出力信号の少なくとも一部をドライバアンプへ帰還させる第2閉ループ回路を形成し、スイッチ制御部は、MEMS発振器の起動期間の少なくとも一部においてスイッチ回路を接続し、所定の条件が満たされる場合に、スイッチ回路を開放する、MEMS発振器。

(もっと読む)

温度補償型水晶発振制御用集積回路

【課題】温度補償型水晶発振制御用集積回路の端子の共用化を実現する。

【解決手段】温度補償型水晶発振制御用集積回路100は、電源電圧が入力される電源端子と、水晶振動子の両端と接続される二つの水晶振動子接続端子と、水晶振動子の周波数調整を行う周波数調整部112に接続され、外部制御電圧が入力される外部制御端子と、水晶振動子の発振出力が出力される発振出力端子と、書込み許可部116と、を備え、電源端子、外部制御端子、及び発振出力端子のうちいずれかは、プログラムイネーブル信号がさらに入力される共用端子であり、共用端子への入力からプログラムイネーブル信号を検出するプログラムイネーブル信号検出部115をさらに備え、かつ、書込み許可部116は、プログラムイネーブル信号検出部115によってプログラムイネーブル信号が検出されたとき、PROM回路113への周波数調整データの書込みを許可するように構成されている。

(もっと読む)

発振回路及び霧化装置

【課題】 少ない部品点数で電源電圧の2倍以上の振幅を得ることができ、かつ、回路を構成する電子部品の定数ばらつきに起因する発振周波数変動を低減することが可能な発振回路を提供する。

【解決手段】 発振回路1は、入力される信号を増幅する増幅部10と、一次側コイルL1と二次側コイルL2とを有し、増幅部10の出力端に一次側コイルL1が接続されたトランス20と、トランス20の二次側コイルL2に一端が接続されるとともに、他端が圧電振動子40を介して増幅部10の入力端に接続される帰還部30とを備える。増幅部10及び前記トランス20は特定の共振周波数を持たず、帰還部30は、トランス20の二次側コイルL2から出力される信号の内、圧電振動子40を共振させる周波数の発振信号を選択して増幅部10へ帰還させる。

(もっと読む)

圧電発振器

【課題】圧電発振器の低電源電圧化に対応可能とすると共に、安定した性能を有する圧電

発振器を提供することを目的とする。

【解決手段】圧電発振器1は、コルピッツ型の発振回路2と、発振回路2が出力する発振

信号より基本波周波数を濾波し、即ち通過させるフィルタ回路3と、発振回路2とフィル

タ回路3との間に接続されたダイオードD1とにより構成し、圧電発振器1には、ノイズ

を除去するためのバイパスコンデンサC5を介して電源電圧(Vcc)を印加している。

本発明においては、発振回路2とフィルタ回路3とをダイオードD1を経由して接続した

。

(もっと読む)

圧電発振器の逓倍発振回路

【課題】最終段の同調回路とその手前の同調回路との間にあるカップリングコンデンサを外してもデカップリング抵抗の抵抗値の設計の自由度が確保された逓倍発振回路を提供する。

【解決手段】圧電振動子を励振する発振回路11と、前記発振回路11の発振波形に含まれる高調波に同調する複数段の同調回路と、を備えた逓倍発振回路10であって、最終段の同調回路15と、前記最終段の前段の同調回路とを接続するデカップリング抵抗R11を備えるとともに、一端を電源側に接続し、他端を前記デカップリング抵抗R11と最終段の同調回路15を構成するコンデンサC16との接続中点に接続するインダクタL5を備えてなる。

(もっと読む)

水晶発振器

【課題】 従来のオーバートン水晶発振器では、オフセット周波数が数十kHz〜1MHz付近にかけてフロアノイズの盛り上がりが発生し、位相雑音特性が劣化してしまうという問題点があり、フロアノイズの盛り上がりを無くし、位相雑音特性の優れたオーバートン水晶発振器を提供する。

【解決手段】 3次オーバートン水晶振動子X1とトランジスタQ1とを備えた発振ループと、同調回路とを備え、3次オーバートン水晶振動子X1に直列にインダクタL1及びL2を接続し、当該インダクタL1及びL2の中間点又は一定比で分割された点から、バッファアンプを介して発振出力を取り出す水晶発振器としている。

(もっと読む)

3次オーバトーンの水晶発振器

【課題】基本波用の発振回路が集積化された発振用ICを用いて3次オーバトーンの水晶発振器を提供する。

【解決手段】コレクタとベース間にバイアス抵抗Rを有して、コレクタに定電流源Iからの定電流を供給し、エミッタ接地とした発振用トランジスタTrと、ベースに直流阻止コンデンサCsを経てアース電位との間に接続した発振用の第1コンデンサC1及びコレクタとアース電位との間に接続した発振用の第2コンデンサC2とを有する発振用IC1を備え、第1コンデンサ及び第2コンデンサとの間に接続した水晶振動子2を有する水晶発振器において、第1コンデンサと並列共振回路を形成するインダクタLを発振用ICとは別個に独立して接続し、第1コンデンサとインダクタとによる並列共振周波数を、水晶振動子の基本波での発振周波数よりも高くかつ水晶振動子の3次オーバトーンでの発振周波数よりも低く設定して3次オーバトーンでの発振とする。

(もっと読む)

発振装置

【課題】従来の発振装置では、負性抵抗は、比較的小さい値であった。

【解決手段】PNP型トランジスタと、NPN型トランジスタと、水晶振動子と、第1のキャパシタと、第2のキャパシタと、を含み、PNP型トランジスタのエミッタが、電源電位に接続されており、NPN型トランジスタのエミッタが、接地電位に接続されており、第1のキャパシタの一端が、接地電位に接続されており、第2のキャパシタの一端が、接地電位に接続されており、PNP型トランジスタのベース、NPN型トランジスタのベース、第1のキャパシタの他端、及び、水晶振動子の一端が相互に接続されており、PNP型トランジスタのコレクタ、NPN型トランジスタのコレクタ、第2のキャパシタの他端、及び、水晶振動子の他端が相互に接続されている。

(もっと読む)

感知装置

【課題】水晶振動子とトランジスタ増幅回路で構成したコルピッツ発振回路で、十分な負性抵抗を確保して安定発振を得るとともに、振幅制御回路を不要にし、さらに温度変化に対する安定化も可能とする。

【解決手段】トランジスタのコレクタに設ける同調回路のインピーダンスが発振周波数において誘導性を呈する構成にする。トランジスタのベース・エミッタ間に接続されるコンデンサC2とエミッタ・GND間に接続されるコンデンサC3との発振周波数におけるインピーダンス比が3対1以上、かつベース・エミッタ間に接続される容量C2の発振周波数におけるインピーダンスが300Ω以上とする。トランジスタのコレクタ・ベース間に接続されるバイアス抵抗R1が3kΩ以下とする。トランジスタのベース・GND間に温度補償用ダイオードD1を直列に介挿する。

(もっと読む)

高周波スプリアス抑制逓倍発振回路

【課題】高周波スプリアスを抑制することができるスプリアス抑制発振回路を提供する。

【解決手段】水晶発振回路11と、水晶発振回路11の発振出力に含まれる所定の高調波

出力に同調する複数段の同調回路12、13、15、16と、複数段の同調回路間を結合

する結合コンデンサC4、C6、C9と、複数段の同調回路12、13、15、16のう

ち、最終段の同調回路16と最終段の同調回路16を結合する結合コンデンサC9との間

に直列に接続されるデカップリング抵抗R7と、を備えるようにした。このように構成す

ると、最終段の同調回路16を結合コンデンサC9のみにより結合する場合に比べて、高

周波スプリアス成分に対するインピーダンスを大きくできるため、デカップリング抵抗R

7により所定の高調波出力より周波数が高い高周波スプリアス成分を抑制することが可能

になる。

(もっと読む)

発振装置

【課題】発信回路内のトランジスタに関わる合成容量が変動し、生成される発振信号の発

振周波数が変動していた。

【解決手段】バイポーラトランジスタと、当該バイポーラトランジスタのベース及び接地

電位間に、相互に並列接続されて設けられた水晶振動子及び発振用コンデンサとを有する

コルピッツ型発振回路であって、前記水晶振動子により規定される発振周波数を有する発

振信号を生成する前記コルピッツ型発振回路と、前記バイポーラトランジスタのコレクタ

及び電源電位間に、相互に並列接続されて設けられたコイル及びコンデンサを有する逓倍

回路であって、前記発振信号に付随する、前記発振周波数の逓倍である逓倍周波数を有す

る逓倍信号を濾波するための前記逓倍回路と、前記コイルに並列接続され、又は、直列接

続された抵抗器とを含む。

(もっと読む)

発振装置

【課題】2つの動作を規定する2つの電流が別個に独立して流れることから、多大な消費

電流が流れていた。

【解決手段】発振周波数を有する発振信号を生成する発振回路であって当該生成に必要な

第1の電流の供給を受ける前記発振回路と、前記発振信号に付随する、前記発振周波数の

逓倍である逓倍周波数を有する逓倍信号を増幅する増幅回路であって当該増幅に必要な第

2の電流の供給を受ける前記増幅回路とを含み、前記第1の電流及び前記第2の電流は、

少なくとも一部が共通に流れる。

(もっと読む)

コルピッツ型発振回路

【課題】比較的安価なトランジスタを使用して、高周波域で高い負性抵抗が得られ、しかも高い発振出力も得られる。

【解決手段】回路ブロックAは、トランジスタQ1と水晶振動子X等によってコルピッツ型発振回路に構成する。回路ブロックBは、ベース接地形増幅回路に構成されたトランジスタQ2でトランジスタQ1のエミッタ出力を増幅し、このコレクタ出力をベース回路(またはコレクタ)に同相で正帰還させる。回路ブロックCはトランジスタQ2の出力を発振出力として取り出す。トランジスタQ2のコレクタに発振周波数も同調させた同調回路を設けた構成、または発振周波数に同調させた同調回路を正帰還の回路に介挿させた構成も含む。

(もっと読む)

始動制御装置を含む発振器

発振装置(1)には、発振器コア(2)と、制御可能な静電容量値を有する、発振器コア(2)に接続された容量性ローディングユニット(3、3a、3b)と、第1および第2のメモリユニット(5a、5b)を含む、容量性ローディングユニットに接続されたメモリ装置(4)と、が含まれる。第1のメモリユニット(5a)は、始動期間中に、静電容量値を制御するために容量性ローディングユニット(3、3a、3b)に供給される第1の値を格納するように構成される。第2のメモリユニット(5b)は、動作期間中に、静電容量値を制御するために容量性ローディングユニット(3、3a、3b)に供給される第2の値を格納するように構成される。発振装置(1)の始動方法によれば、発振信号の振幅が測定される。さらに、動作期間の開始時点が、発振信号が所定の閾値を超える時点として選択される。  (もっと読む)

(もっと読む)

逓倍型の水晶発振器

【目的】小型を促進してn次高調波成分よりも低い雑音成分を抑圧した逓倍型発振器を提供する。

【構成】アース電位に接地した並列共振回路及び増幅回路を有する逓倍回路を発振回路に接続し、前記発振回路のn次高調波成分(但し、nは2以上の整数)を出力とする逓倍型の水晶発振器において、前記並列共振回路は、前記n次高調波成分よりも低い共振周波数とするインダクタとコンデンサの直列共振回路と、前記直列共振回路に並列接続したリアクタンス素子とから逓倍型の水晶発振器を構成する。

(もっと読む)

2周波出力圧電発振器

【課題】2周波出力の電圧制御圧電発振器において、二つの水晶発振器の出力周波数が大きく異なると、それぞれの発振器出力にLC同調回路を必要とするので、部品点数が増えて小型化の障害となる。

【解決手段】第1の圧電発振器と、第2の圧電発振器と、外部から供給された選択信号に基づき前記第1、第2の圧電発振器がそれぞれ出力する発振信号のうち、いずれか一方を選択し出力する切替手段とを備えた2周波出力圧電発振器において、前記切替手段の出力に少なくともインダクタンス素子と可変容量素子とを有するLC可変同調回路を備えたことを特徴とする2周波出力圧電発振器。

(もっと読む)

周波数選択性を有し低位相ノイズかつ低熱ドリフトの発振器

電圧制御発振器(200)は、3端子デバイス(203)と、このデバイスの第1の端子(208)と第2の端子(210)とに跨って結合された回路(205)とを具備する。回路(205)は好ましくは、デバイス(203)をバイアスするとともに、デバイス(203)によって発生した選択量のノイズをデバイス(203)にフィードバックしてデバイス(203)の第3の端子(216)に存在する比例量の位相ノイズを低減する働きをする。

(もっと読む)

(もっと読む)

1 - 17 / 17

[ Back to top ]