Fターム[5J079GA05]の内容

電気機械共振器を用いた発振回路 (23,106) | 発振のための増幅部の構成 (697) | MOS、CMOS (103) | MOS、CMOS2段以上 (23)

Fターム[5J079GA05]に分類される特許

1 - 20 / 23

半導体装置

【課題】消費電力の低減と、製造コストの低減とを両立する発振回路を提供する。

【解決手段】本発明の半導体装置によれば、直列に接続されて、かつ、それぞれがダイオード接続された複数のMOSトランジスタを用いて、発振回路部を駆動させる電圧を生成する。このとき、複数のMOSトランジスタで生成される電圧の値は、電源電圧と、各MOSトランジスタのスレッショルド電圧の比率とに基づいて得られる。したがって、各MOSトランジスタのスレッショルド電圧を小さく抑えることが出来て、各MOSトランジスタの面積を節約することが出来て、発振回路部の消費電力を削減することが出来る。

(もっと読む)

電子装置およびその製造方法、並びに発振器

【課題】高い信頼性を有する電子装置を提供する。

【解決手段】本発明に係る電子装置100は、基板10と、基板10の上方に形成された機能素子20と、機能素子20が配置された空洞部1を画成する包囲壁40と、基板10の上方に形成され、機能素子20に接続された配線層30,32と、を含み、配線層30,32は、基板10と包囲壁40との間を通って、包囲壁40の外側まで延出され、包囲壁40は、窒化シリコン層42と、金属層およびシリコン層の少なくとも1層である導電層と、を有し、配線層30,32と導電層44との間には、窒化シリコン層42が配置されている。

(もっと読む)

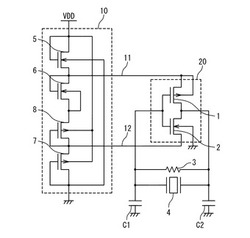

バッファ回路

【課題】出力波形を高調波が発生しない様に調整する事ができ、高次高調波の抑圧効果の高い水晶発振回路の提供。

【解決手段】水晶振動子を振動源とする発振回路部と、この発振回路部の出力信号を入力とするCMOSトランジスタのインバータからなる複数段のバッファ回路部11、12、13と、このバッファ回路部の出力から直流成分をカットするキャパシタCB1、CB2を介して増幅するCMOSプッシュプル型増幅回路14とを備えた水晶発振回路に於いて、バッファ回路部13のCMOSトランジスタTp4とCMOSトランジスタTn4間に抵抗素子R3、R4を接続し、その中間点はバッファ回路部13の出力として、前記抵抗素子と前記キャパシタとからなる時定数で出力信号の波形成形を行い、且つ前記抵抗素子のバイパス回路16をメモリ設定にて、MOSスイッチ手段17のオン/オフ切り替えにより可能とするメモリを備えてなる。

(もっと読む)

MEMS振動子および発振器

【課題】周波数精度の高いMEMS振動子を提供する。

【解決手段】MEMS振動子100は、基板10と、基板10の上方に配置された第1電極20と、少なくとも一部が前記第1電極20との間に空隙を有した状態で配置され、前記基板10の厚み方向に静電力によって振動可能となる梁部34、梁部34の一端34aを支持し基板10の上方に配置された支持部32を有する第2電極30と、を含み、支持部32の一端34aを支持する支持側面32aは、基板10の厚み方向からの平面視で屈曲している屈曲部を有し、一端34aは、屈曲部を含む支持側面32aにより支持されている。

(もっと読む)

発振回路

【課題】負荷のドライブ能力を変更できる、発振回路を提供すること。

【解決手段】定電圧生成回路70と、発振出力Voscを生成する発振出力生成回路80と、定電圧生成回路70によって生成された定電圧Vref’が電源電圧として供給される複数のMOSFET回路D1,D2,D3を並列に有し、複数のMOSFET回路D1,D2,D3のそれぞれの出力点P1,P2,P3が互いに接続された出力回路90と、複数のMOSFET回路D1,D2,D3の中から選択入力に応じて選択されたMOSFET回路を発振出力Voscに従って駆動する駆動回路91とを備え、前記選択入力に応じて選択されていないMOSFET回路の出力が、ハイインピーダンスである、発振回路。

(もっと読む)

発振装置

【課題】発振周波数を決定する容量値の変化に伴う発振周波数の変動を抑え、且つ、位相雑音を低減することのできる発振装置を提供する。

【解決手段】発振装置は、ドレイン接地回路からなる第1増幅回路10と、第1増幅回路10の出力を増幅する、ゲート接地回路からなる第2増幅回路20と、第2増幅回路20の出力を第1増幅回路の入力に帰還させるコンデンサC1と、第1増幅回路10の入力側に設けられた共振器2と、共振器2及び第1増幅回路10内のトランジスタQ1に動作用のバイアス電圧を印加するバイアス回路12と、第2増幅回路20内のトランジスタQ2に動作用のバイアス電圧を印加するバイアス回路22とから構成される。この結果、位相雑音の発生を、単一のトランジスタからなるコルピッツ発振回路と同程度に抑えつつ、容量変化によって発振を起動できなくなったり、発振周波数が変動するのを防止できる。

(もっと読む)

温度補償型圧電発振器

【課題】周波数が安定するまでの時間を短縮することができると共に、消費電力を低減出来る圧電発振器の提供。

【解決手段】温度補償を行う前の状態で、温度に対する変曲点近傍の変動が0ppm/℃又は、0ppm/℃近傍となる圧電振動素子120と、集積回路素子130には、圧電振動素子の共振周波数に基づいて発振信号を出力する第1のインバータINV1と、負荷容量になる可変容量ダイオードCV1、CV2を含む発振回路部Xと、発振信号を増幅する第2のインバータINV2を含む増幅回路部Yと、温度補償用制御データを記憶するためのメモリ部Mと、温度補償用制御データに基づき、温度補償を行なう温度補償信号制御回路部Tと、第1のインバータINV1と電源電圧端子Vddの接続間及び増幅回路部の第2のインバータINV2と電源電圧端子Vddの接続間に配置され、インヒビット端子INHからの信号により動作するスイッチSW1と、を備える。

(もっと読む)

発振回路

【課題】 クロック発振回路のジッタが音質に重要だとは気が付かなかったか、CMOSの発振回路のジッタ性能で十分だと思われていた。しかし、ジッタが多いと、音質的に十分でないことが判明した。そこで、高音質化のため低ジッタ化し、なおかつ高周波化、低電圧化、波形のエッジの急峻さ、波形の対称性を達成する必要性がある。

【解決手段】 CMOSよりもノイズ特性に優れるバイポーラトランジスタを使い、これをコンプリメンタリ接続にすることで、低ジッタ、高周波化、低電圧化、波形のエッジの急峻さ、高い対象性を得ることができた。

(もっと読む)

半導体集積回路及び発振回路

【課題】振動子が外付けされて発振回路を実現する半導体集積回路において、振動子が外付けされるパッドと内部回路間の配線による浮遊容量の影響を小さくする。

【解決手段】半導体集積回路は、半導体基板と、第1のパッドP1に第1の抵抗及R1及び第1のコンデンサCACを介して接続の入力端子、及び、第2のパッドP2に第2の抵抗R2及び第3の抵抗RDを介して接続の出力端子を有するインバータ32と、インバータ入力端子と第2の抵抗R2及び第3の抵抗RDの接続点との間に接続され、インバータと共に発振ブロックを構成する帰還素子33と、第1の抵抗R1及び第1のコンデンサの接続点と基板電位との間に接続され、第1のパッドと発振ブロックとの間に配置された第2のコンデンサCGと、第2の抵抗R2及び第3の抵抗RDの接続点と基板電位との間に接続され、第2のパッドP2と発振ブロック間に配置された第3のコンデンサCDとを具備する。

(もっと読む)

圧電発振器を用いた受信装置の衛星捕捉制御方法

【課題】温度補償回路を内蔵しない圧電発振器を用いて、GPS衛星の測位信号の捕捉時

間を短縮化させることができる圧電発振器、その圧電発振器を用いた受信装置および圧電

発振器を用いた受信装置の衛星捕捉制御方法を提供する。

【解決手段】圧電発振器用IC2と圧電振動子4を同一パッケージに組み立てて圧電発振

器1を構成すると、温度センサ7は精度よく圧電振動子4の温度を検出できる。圧電発振

器1を恒温槽に入れて、温度Tと出力周波数foutの周波数の関係を取得する。得られた

周波数−温度特性より、温度係数(A,B,C,D)とオフセット係数(E)を算出して

メモリ10に書き込む。この圧電発振器1を受信装置に組み込んだときにメモリ10から

温度係数とオフセット係数を抽出して近似曲線計算式から圧電発振器1の周波数偏差を求

め、周波数偏差分だけ、衛星からの探索範囲をオフセットさせて、GPS衛星の周波数を

捕捉する。

(もっと読む)

圧電発振器、および圧電発振器を用いた受信装置

【課題】温度補償回路を内蔵しない圧電発振器を用いて、GPS衛星の測位信号の捕捉時

間を短縮化させることができる圧電発振器、その圧電発振器を用いた受信装置および圧電

発振器を用いた受信装置の衛星捕捉制御方法を提供する。

【解決手段】圧電発振器用IC2と圧電振動子4を同一パッケージに組み立てて圧電発振

器1を構成すると、温度センサ7は精度よく圧電振動子4の温度を検出できる。圧電発振

器1を恒温槽に入れて、温度Tと出力周波数foutの周波数の関係を取得する。得られた

周波数−温度特性より、温度係数(A,B,C,D)とオフセット係数(E)を算出して

メモリ10に書き込む。この圧電発振器1を受信装置に組み込んだときにメモリ10から

温度係数とオフセット係数を抽出して近似曲線計算式から圧電発振器1の周波数偏差を求

め、周波数偏差分だけ、衛星からの探索範囲をオフセットさせて、GPS衛星の周波数を

捕捉する。

(もっと読む)

電子装置

【課題】発振特性の検査を行うことができると共に、発振不良の発生を抑制することができる電子装置を提供すること。

【解決手段】

振動子10と、振動子10と共に発振回路を形成する回路部20とを樹脂で封止してなる電子装置50であって、一方の端部が振動子10の両端にそれぞれ接続されると共に他方の端部が樹脂の外部に露出する振動子の発振特性検査用の検査端子41,42と、検査端子41,42と振動子10との間に設けられ、検査端子41,42の電位による影響から振動子10を保護する保護抵抗31,32とを備える。

(もっと読む)

発振器及び発振器を備えた電子機器

【課題】負性抵抗の減少を防止し、低消費電力化。

【解決手段】第1の端子Aと、第2の端子Bと、第1の端子Aと第2の端子Bとの間に接続された振動子OSCと、第1の端子Aと接地電位を供給する接地線GNDとの間に接続された第1のコンデンサCgと、第2の端子Bと接地線GNDとの間に接続された第2のコンデンサCdと、第1の端子Aと第2の端子Bとの間にm個(mは3以上の奇数)のインバータIN1〜IN3が直列に接続されたインバータ列と、インバータ列の入力側から数えてn番目(nは1≦n<mの整数)のインバータの入力端子とn+1番目のインバータの出力端子との間に接続された第3のコンデンサCfと、を含む、ことを特徴とする発振器100。

(もっと読む)

発振回路、発振器

【課題】発振に必要な負性抵抗を小さくすると同時に回路の低消費電力を図ることのできる発振回路及び発振器を提供する。

【解決手段】発振回路10は、トランジスタM1とトランジスタM2とが差動接続されるクロスカップル型回路からなり、振動子SAWの共振点帯域で発振する。トランジスタM1は第1ソース負荷回路としての抵抗器RL1に接続され、トランジスタM2は第2ソース負荷回路としての抵抗器RL2に接続されている。また、トランジスタM1は第1ドレイン負荷回路としての抵抗器Rs1に接続され、トランジスタM2は第2ドレイン負荷回路としての抵抗器Rs2に接続されている。第1ソース負荷回路のインピーダンスの大きさが第1ドレイン負荷回路のインピーダンスの大きさ以上であり、且つ、第2ソース負荷回路のインピーダンスの大きさが第2ドレイン負荷回路のインピーダンスの大きさ以上とする。

(もっと読む)

半導体装置

【課題】製造プロセスの微細化と、しきい電圧の低下により、通常オフ状態となっているMOSトランジスタにリーク電流が発生する。また、製造プロセスによっては、NチャンネルMOSトランジスタとPチャンネルトランジスタとのリーク電流が等しいとは限らない場合があり、発振回路のような回路構成によっては、動作に問題を引き起こす可能性が高い。

【解決手段】本発明にかかる半導体装置は、制御電圧により駆動力が変化する第1のトランジスタを有する保護回路と、前記保護回路と同一の回路構成を有するモニター回路と、前記モニター回路が出力する電圧と、基準電圧との比較結果に基づいて前記制御電圧を生成する制御電圧生成回路とを有する。

(もっと読む)

パルス発生回路

【課題】発振周波数が数MHz〜GHzの高周波用に適用可能であり、かつ消費電力が少ない、定電流回路を用いたパルス発生回路を提供すること。

【解決手段】パルス発生回路は、電源間に定電圧回路1を有し、電流制御素子7と波形発生部9とを直列に接続して、それらを定電圧回路1と並列に接続して構成されている。そして、波形発生部9は、平滑回路2と、水晶発振回路4と、水晶発振回路4からの出力を受けて最終出力波形のデューティ比を調整する出力デューティ調整回路5と、水晶発振回路4の発振波形と最終出力波形との位相差を調整する位相調整回路6と、を並列に接続して構成されている。使用する水晶振動子の周波数によっては、位相調整回路6の替わりに分周回路を並列に接続して構成されている。

(もっと読む)

発振回路

【課題】スイッチによる周波数の切り替え時に発生する発振波形の乱れを解消した発振回路を提供することにある。

【解決手段】第1のIDTとしてのIDT12aおよび第2のIDTとしてのIDT12bの極性を反転する際に、スイッチ手段としてのスイッチSW5〜SW8が遮断されて、第1のIDTとしてのIDT12aおよび第2のIDTとしてのIDT12bの並列接続状態が解除される期間である期間Tdにおいては、スイッチSW5〜SW8がすべて遮断状態となる。期間Tdを必要最小限にして十分な値に設定しておけば、何らかの要因で信号V11または信号V21のレベルが若干ずれたタイミングで切り替わったとしても、両信号が同時にハイレベルとなる事態を回避することができる。したがって、スイッチSW5とスイッチSW6、あるいは、スイッチSW7とスイッチSW8が、それぞれ同時に導通状態となることが回避される。

(もっと読む)

発振回路

【課題】低消費電力でありながら大きな負性抵抗を得ることができる発振回路を提供する。

【解決手段】発振回路は、SAW振動子Xと、SAW振動子Xと信号路を介して並列接続され発振駆動されるCMOSインバータA1〜A3と、CMOSインバータA1〜A3の出力側と入力側との間に、CMOSインバータA1〜A3の出力側から入力側に信号が正帰還するように、接続された負性抵抗増加回路10と、負性抵抗増加回路10とCMOSインバータA1〜A3の入力側との間に接続する容量素子としての帰還用コンデンサCfと、を含む。

(もっと読む)

水晶発振器回路および水晶発振器回路を内蔵する半導体装置

【課題】 対雑音に高い耐性をもつ差動回路を用いても、電源ノイズΔVに起因するジッタ特性を改善することはできなかった。

【解決手段】 水晶発振器回路は、水晶発振子(X0)を接続する第1端子(X1)及び第2端子(X2)と、第1増幅回路(1)と、第2増幅回路(2)とを具備する。第1増幅回路(1)は、第1端子(X1/OUT1)に入力を接続し、第2端子(X2/OUT2)に出力を接続する。第2増幅回路(2)は、第2端子(X2/OUT2)に入力を接続し、第1端子(X1/OUT1)に出力を接続する。水晶発振器回路は、第1端子(X1/OUT1)と第2端子(X2/OUT2)とを差動出力ノードとする。水晶発振器回路は、第1端子(X1/OUT1)から正電源(VCC)、負電源(VSS)をみたインピーダンスの比と、第2端子(X2/OUT2)から正電源(VCC)、負電源(VSS)をみたインピーダンスの比が等しくなるように構成される。

(もっと読む)

圧電発振器

【課題】電源変動特性に優れた圧電発振器に関して優れたノイズ特性が実現できないという問題を解決する。

【解決手段】圧電振動子と、該圧電振動子の周波数信号を増幅し、発振する為の第一のトランジスタと、該発振用トランジスタの出力信号を増幅する為の第二のトランジスタとを備え、前記第一のトランジスタと前記第二のトランジスタとをカスコード接続した圧電発振器に於いて、前記第二のトランジスタのベースと接地との間にMOSFETを順方向接続し、該MOSFETのゲートを前記第二のトランジスタのエミッタに接続するよう構成したことを特徴とする圧電発振器。

(もっと読む)

1 - 20 / 23

[ Back to top ]