Fターム[5J081BB03]の内容

LC分布定数、CR発振器 (9,854) | 用途 (545) | 映像・音響機器用 (19)

Fターム[5J081BB03]に分類される特許

1 - 19 / 19

電子機器およびクロック補正方法

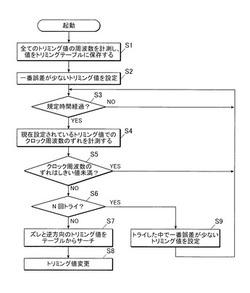

【課題】 RC発振器によりクロック信号を生成するシステムにおいて、クロック信号の周波数を大きく変動させずに補正して規定の範囲に保つことのできる電子機器およびクロック補正方法を提供することにある。

【解決手段】 RC発振器の抵抗または容量の設定を切り替えてクロック信号の周波数を複数段階に変更可能な周波数変更手段と、この複数段階の変更量を表わしたトリミングテーブルを記憶する記憶手段と、周波数変更手段の設定を切り替えてクロック信号の周波数を補正するクロック補正制御手段とを備えた電子機器およびそのクロック補正方法である。そして、クロック補正制御手段は、トリミングテーブルのデータに基づき、クロック信号の周波数を補正前の周波数から規定の周波数へ次第に近づいていくように周波数変更手段の設定を切り替えて(S7,S8)、クロック信号の周波数を補正する。

(もっと読む)

発振回路及びテレビジョン信号受信用チューナ

【課題】特別の部品を追加することなく、平衡型の発振回路のC/N特性を改善すること。

【解決手段】VHFローバンド及びVHFハイバンドのテレビジョン信号を受信するための局部発振器を不平衡型の発振回路11,12で構成し、UHFのテレビジョン信号を受信するための局部発振器を平衡型の発振回路13で構成し、VHFバンド用発振回路11,12のC/N特性改善のために設けている抵抗R2の接続点を、UHF用発振回路13に接続した共振回路23のインダクタンス素子23aの一端に接続し、平衡型のUHF用発振回路13に対してラインフィルタ31,32を両側に配置する。

(もっと読む)

発振回路、異常発振検査方法、高周波受信機、及び高周波送信機

【課題】複数の電圧制御発振器を有するにもかかわらず異常発振の有無検査の検査時間を短縮することができる発振回路を提供する。

【解決手段】動作電流がそれぞれ異なる値である第1から第n(nは2以上の自然数)の電圧制御発振器VCO1〜VCOnと、1つの基準電圧生成回路RV0と、第1から第n(nは2以上の自然数)のスイッチSW1〜SWnとを備え、すべてのk(k=1〜n)について、第kの電圧制御発振器VCOkの直流バイアス入力端子T_kと基準電圧生成回路RV0の直流バイアス出力端子T_0との間に第kのスイッチSWkが設けられており、第kのスイッチSWkがオン状態のときに基準電圧生成回路RV0から第kの電圧制御発振器VCOkの差動トランジスタにベースバイアス電圧が供給される発振回路。

(もっと読む)

FMチューナ

【課題】FMチューナのステレオ復調部における、パイロット信号をキャプチャするPLLを構成するVCOを、CR発振回路を用いて構成すると、温度に応じた発振周波数の変動に対応してキャプチャレンジが大きく設定される。そのため、パイロット信号の近傍周波数のノイズ等にPLLが誤って同期しやすくなる。

【解決手段】ステレオ復調部76を含むチューナ半導体チップ内に温度センサ回路94を設け、VCO部位の温度を検知する。温度センサ回路94の出力信号STPに基づいて、VCOの発振周波数fVCOを調整し、温度によるfVCOの変動を補償する。これによりキャプチャレンジの幅を、セラミックレゾネータ等を用いた場合のように狭く設定できる。

(もっと読む)

電圧制御発振器、PLL回路

【課題】 低周波の発振信号であっても安定して出力することが可能な電圧制御発振器及びPLL回路を提供する。

【解決手段】 本発明に係る電圧制御発振器1は、インダクタ4及び可変キャパシタ5を有するLC共振回路2と、複数の負性抵抗回路NR1、NR2、…、NRnを備える。各負性抵抗回路NR1、NR2、…、NRnは、定電流源CG1、CG2、…、CGnを介して夫々接地線と接続される構成であり、各定電流源は、夫々個別に導通状態(一定電流を流す状態)と非導通状態(開放された状態)との間で切換制御が可能に構成されており、本発明に係る電圧制御発振器1は、これらの各定電流源の導通制御を行うための制御手段7を備える構成である。

(もっと読む)

高周波装置の製造方法

【課題】基板に紙系の基材を用いても発振器の発振周波数の変動が少ない高周波装置を提供する。

【解決手段】紙基材の基板22上にはチップコンデンサ23と空芯コイル24とが搭載され、チップコンデンサ23は鉛フリー半田25で接続され、空芯コイル24は鉛フリー半田27で接続される。基板22上の空芯コイル24によって発信器7が形成され、この発信器7は空芯コイル24によって発振周波数が調整される。そして、鉛フリー半田25を溶かすための1回目のリフロー工程53における基板22のピーク温度と、鉛フリー半田27を溶かすための2回目のリフロー工程57における基板22のピーク温度との和の温度を475℃以下とする。これにより、チューナ1の吸湿による発信器7の周波数変動が小さくできる。

(もっと読む)

発振器

【課題】発振周波数変更機能を備えた発振器において、不揮発性メモリからデータを読み出す際に発振周波数が変更されることなく安定的に読み出すことができる。

【解決手段】LSIの外部に設けられた不揮発性メモリ15に、発振回路13から発振されるクロック信号の周波数を変更するための周波数設定値が記憶されており、その周波数設定値が、発振回路13から発振される初期設定された周波数のクロック信号によって読み出されると、ダミーレジスタ11に格納される。不揮発性メモリ15からデータが全て読み出されてロード動作完了信号が出力されると、ダミーレジスタ11から記憶レジスタ12へ周波数設定値が格納され、発振回路13の発振周波数が周波数設定値とされる。

(もっと読む)

電圧制御発振器

【課題】ICへの集積化も容易で、かつ、浮遊容量の発振周波数への影響も効果的に低減することが可能な電圧制御発振器を提供する。

【解決手段】バリキャップVC3,VC4のアノード共通接続点に設けられた第1のスイッチ回路P1と、第1の制御電圧Vtの供給配線上に設けられた第2のスイッチ回路P2と、バリキャップVC3,VC4の各アノードと第2の制御電圧VCONTの入力端子との間にそれぞれ接続された複数の抵抗R1,R2とを備え、バリキャップVC3,VC4を切り離すために第1のスイッチ回路P1をオフにしたときは、バリキャップVC3,VC4が抵抗R1,R2を介して第2の制御電圧VCONTの入力端子に接続されるようにし、バリキャップVC3,VC4を使用するときは第1および第2のスイッチ回路P1,P2をオンとし、同調電圧Vtによって発振周波数を制御できるようにする。

(もっと読む)

周波数逓倍回路

【課題】製造コストおよび消費電力を低下させることができる周波数逓倍回路を実現する。

【解決手段】本発明の周波数逓倍回路1は、電圧制御発振器を備え、上記電圧制御発振器のトランジスタ差動対Tr1・Tr2のエミッタから上記電圧制御発振器の発振周波数を逓倍した信号を取り出している。すなわち、電圧制御発振器と回路を共用している。

(もっと読む)

電圧制御発振器及び電圧制御発振器ユニット

【課題】デジタル放送を良好に受信することができる低コストな電圧制御発振器及び電圧制御発振器ユニットを提供する。

【解決手段】本発明の電圧制御発振器1aは、インダクタ3に対して互いに並列に設けた可変容量素子4・5を有し、インダクタ3のインダクタンスと可変容量素子4・5の容量値の合計とに基づく共振周波数で共振する共振回路2と、可変容量素子4・5のうちの少なくとも1つの容量値制御端子5の接続先を切り替える少なくとも1個のスイッチ6とを備える。

(もっと読む)

自動振幅制御機能を有する電圧制御発振機

【課題】電流源の代わりにアクティブ負荷を採用して利得の調整により電流源による位相雑音を除去し位相雑音特性を有する自動振幅制御機能を有する電圧制御発振機を提供する。

【解決手段】自動振幅制御機能を有する電圧制御発振機は共振信号を生成する共振回路と、共振信号をフィードバックして相互180°の位相差を有する2つの発振信号を生成する差動増幅回路と、差動増幅回路から生成される発振信号の利得を制御するアクティブ負荷を含む電圧制御発振部、及び2つの発振信号を変換して直流電圧を生成した後直流電圧と事前に設定された基準電圧を比較して上記アクティブ負荷の抵抗値を決定する制御電圧を出力する自動振幅制御部を含む。出力される発振信号の振幅を効果的に制御することが可能で、差動増幅回路のスイッチング時電流源により流入されるノイズ成分による位相雑音を減少させることが可能である。

(もっと読む)

周波数変換器

【課題】 発振周波数を下げたときに発振停止を起こしにくくし、さらに、温度が上昇したときにも発振停止を起こしにくくする。

【解決手段】 ミキサトランジスタ86〜89のコレクタバイアス電流と発振トランジスタ61、62のコレクタバイアス電流とを設定するためのバイアス電源74を設け、制御電圧Vtが第1の所定値以上のときよりも第1の所定値以下のときにバイアス電源74の出力電圧を高くしてミキサトランジスタ86〜89のコレクタバイアス電流又は発振トランジスタ61、62のコレクタバイアス電流の少なくとも一方を大きくした。

(もっと読む)

電圧制御発振器及びこれを備えた集積回路装置

【課題】本発明は、ある周波数を発振するに際して、いずれの電圧制御発振回路を選択すべきかを一意的に決定することが可能な電圧制御発振器を提供することを目的とする。

【解決手段】本発明に係る電圧制御発振器は、複数の電圧制御発振回路(図6ではVCO1〜VCO3)と、そのうちの1つを選択して動作させる選択回路と、を有して成り、隣接する電圧制御発振回路の発振周波数可変域がその端部で互いに重複されて成る電圧制御発振器において、最も低域側にばらついた状態(low状態)におけるn(≧1)番目の電圧制御発振回路の上端周波数が、最も高域側にばらついた状態(high状態)におけるm(=n+1)番目の電圧制御発振回路の下端周波数よりも高くなるように、各電圧制御発振回路の発振周波数可変域を調整して成る構成とされている。

(もっと読む)

インダクタ、共振回路、半導体集積回路、発振器、通信装置

【課題】 インダクタを大型化することなくそのQ値を高める。

【解決手段】 積層された複数の絶縁層における所定の層上にコイルパターンが形成されたインダクタであって、少なくとも2つの絶縁層上にコイルパターンが形成されるとともに各コイルパターン同士が電気的に接続されている。

(もっと読む)

CR発振回路および電子装置

【課題】 発振周波数の調整手段の選択余地を広げるのが望ましい。

【解決手段】 CR発振回路100において、第1発振用コンデンサC1および第2発振用コンデンサC2を並列に設け、CR発振回路100全体の容量値を選択可能に構成し、可変抵抗である、例えば第5トリミング抵抗116eを少なくとも一つ含む複数の抵抗を直列に設け、第5トリミング抵抗116eの抵抗値を調整することによってCR発振回路100全体の抵抗値を選択可能に構成し、CR発振回路100全体の容量値として選択可能な最小値CMINと最大値CMAX、およびCR発振回路100全体の抵抗値として選択可能な最小値RMINと最大値RMAXの間に、

CMIN・RMAX≧CMAX・RMIN

なる関係をもたせる。

(もっと読む)

周波数同調可能な装置

周波数同調可能な装置は、キャパシタンス範囲の全体にわたって同調可能な容量性部分(C1、C2、Cv1、Cv2)を有する共振回路(RS)を備える。発振ループを形成するために、共振回路には複数の増幅器(AB、AS1、AS2、AS3)が結合される。それらの増幅器の少なくとも1つが、活性状態とアイドル状態との間で切り替えが可能な切替可能増幅器(AS1)である。切替可能増幅器は、活性状態とアイドル状態との間で切り替えられたときに、共振回路の容量性部分と並列にキャパシタンス変化を引き起こす。切替可能増幅器は、このキャパシタンス変化が、容量性部分が同調可能なキャパシタンス範囲とほぼ一致するように構成される。  (もっと読む)

(もっと読む)

局部発振回路

【課題】 共通の発振トランジスタ及び共振回路によって、ハイバンド受信用の局部発振周波数帯域とローバンド受信用の局部発振周波数帯域とをカバーする。

【解決手段】 発振トランジスタ11、12を内部に構成すると共に、発振トランジスタ11、12のベースとコレクタとにそれぞれ結合された第1及び第2の端子10a、10bを有する集積回路10と、集積回路10の外部に設けられ、第1及び第2の端子10a、10b間に結合される共振回路30とを備え、集積回路10内には各端子10a、10bにカソードが接続され、アノードが接地された静電破壊防止用の保護ダイオード19、20を設け、保護ダイオード19、20のカソードには、VHFローバンド受信時に電圧を印加せず、ハイバンド受信時に逆バイアス用の電圧を印加した。

(もっと読む)

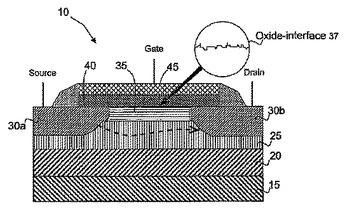

ストレインド・シリコン電圧制御発振器(VCO)

ストレインド・シリコン電圧制御発振器(VCO)は、ストレインド・シリコン層を有する第1Pチャネル金属酸化膜半導体(PMOS)装置を含み、ストレインド・シリコン層を有する第2PMOS装置に結合される。  (もっと読む)

(もっと読む)

発振回路

【課題】 VCO発振周波数の調整を容易にする。

【解決手段】 VCO用共振回路が接続されるボンディングパッド5下のエピタキシャル層2Aの電位を、従来のフローティング状態から抵抗6を介して所定(Vcc)電位に固定することで、エピタキシャル層2Aの電位変化を速くして、寄生容量値が速やかに安定することから、電源ON時のドリフトが改善する。

(もっと読む)

1 - 19 / 19

[ Back to top ]