Fターム[5J081BB09]の内容

LC分布定数、CR発振器 (9,854) | 用途 (545) | 変復調用 (42)

Fターム[5J081BB09]に分類される特許

1 - 20 / 42

電圧制御発振器およびそれを用いた情報機器

【課題】周波数変換利得の変動が少ない発振器のためのLC共振回路、それを用いた発振器及び情報機器を提供する。

【解決手段】発振器のLC共振回路が、インダクタL1、第1の微調容量と第1の容量バンクからなる並列回路と、第2の微調容量と第2の容量バンクの直列容量とを含む。発振器の周波数変換利得は、第1の容量バンクの容量値が大きくなるに従い低下する第1の微調容量による発振器の周波数変換利得と、第2の容量バンクの容量値が大きくなるに従い増大する第2の微調容量による周波数変換利得の和となる。

(もっと読む)

発振器、および発振を開始する方法

【課題】休止期間は消費電力を削減すると共に起動特性のよい発振器を提供する。

【解決手段】発振信号がコールドスタートからの規定の定常状態条件に達する時を早める回路を含んでいる発振信号を生成するための装置。装置は、発振信号を生成するための発振回路412と、前記発振回路に第1の電流を供給する第1の制御可能電流源404と、発振回路に第2の電流を供給する第2の制御可能電流源408と、を含み、第1および第2の電流は、発振信号が規定の定常状態条件に達するための時間分を縮小するのに適している。装置は、1以上の通信チャネルを確立するために低い負荷サイクルパルス変調を用いる通信システムに有益であるかもしれず、それによって装置はパルスのほぼ始めで発振信号を生成し始め、パルスのほぼ終わりに発振信号を終了する。

(もっと読む)

半導体装置

【課題】CMOSトランジスタによって構成されたVCOを備えた半導体装置において、発振信号の発振振幅のばらつきの抑制および低消費電力化を実現する。

【解決手段】VCO30は、CMOSトランジスタによって構成されたLCタンクVCOと、VCOの発振周波数帯域から一の発振周波数を選択するための周波数選択信号を生成する自動周波数選択回路42と、VCOの制御電圧を生成するPLL32と、周波数選択信号に基づいて差動型のMOSトランジスタのゲートに供給するバイアス電圧を調整するバイアス回路50とを備える。

(もっと読む)

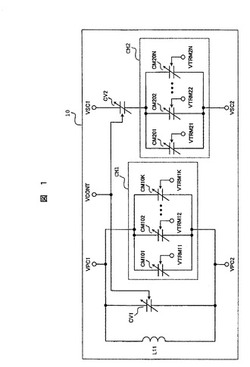

発振器複合回路と半導体装置並びに電流再利用方法

【課題】発振器の不安定動作を回避し低消費電力化を実現する発振器複合装置と方法の提供。

【解決手段】インダクタ(111)と容量(112)を含む共振回路(110)を備えた発振器(100)と、前記発振器の発振出力信号を入力し、且つ、電源側からの電流パスを構成し前記電流パスの前記第1の電源と反対側の一端が前記発振器の前記インダクタ(111)の中点に接続された差動対を含む分周器(200)とを、グランドと電源間に縦積みに配置し、分周器(200)の直流供給電流端子(230)からグランド側に流れる直流電源電流を、発振器(100)の電源電流として再利用する。

(もっと読む)

半導体チップ、筺体内信号伝送方法及び筺体内信号伝送システム

【課題】同一の筺体内に配置された半導体チップ間でミリ波の信号伝送媒体を介したミリ波帯域の信号を伝送できるようにすると共に、当該半導体チップ間でより簡易に高速伝送システムを実現できるようにする。

【解決手段】入力信号SINが基準搬送信号Sfに基づいてミリ波の送信信号Soutに変換され、変換後の送信信号Soutが、筺体1内に配置されたCMOSチップ101の送信部から当該筺体1内のミリ波の信号伝送媒体51へ伝送される場合であって、局部発振信号Sf’を発振する発振回路を有して筺体1内に配置され、信号伝送媒体51から受信したミリ波の受信信号Sinを発振回路に注入して当該局部発振信号Sf’を基準搬送信号Sfに同期させ、同期後の局部発振信号Sf’に基づいてミリ波の復調信号SOUTを復元するものである。

(もっと読む)

電圧制御発振器

【課題】電界効果トランジスタのドレイン−ソース間容量のばらつきによる位相誤差を低減しつつ、位相が互いに90°ずつ異なる発振信号を生成する。

【解決手段】電界効果トランジスタM1のドレインと電界効果トランジスタM2のドレインとの間にインダクタL1を接続し、電界効果トランジスタM3のドレインと電界効果トランジスタM4のドレインとの間にインダクタL2を接続し、インダクタL1にインダクタL3を磁気的に結合し、インダクタL2にインダクタL4を磁気的に結合し、インダクタL3の一端とインダクタL4の一端とをコンデンサC1を介して容量結合し、インダクタL3の他端とインダクタL4の他端とをコンデンサC2を介して容量結合する。

(もっと読む)

切り替え可能インダクタネットワーク

制御信号に応じて設定可能インダクタンスを有する切換可能インダクタネットワークを提供するための技術。前記切り替え可能インダクタネットワークは、差動モード動作の寄生素子の影響を低減するために完全に対称的なアーキテクチャを採用することができる。前記切り替え可能インダクタネットワークは、特に、マルチモード通信回路への用途、例えば、電圧制御発振器(VCO)またはそのような回路におけるアンプもしくはバッファに適している。 (もっと読む)

VCO周波数チューニングのための、オーバーラップする2セグメントキャパシタバンク

【解決手段】(例えばFM受信機中の)VCOは、LC共振タンクを含む。LC共振タンクは、粗同調キャパシタバンクおよび微同調キャパシタバンクを含む。粗同調キャパシタバンクは複数のデジタル制御粗同調キャパシタエレメントを含み、アクティブな際に各々は第1キャパシタンス値を供給する。微同調キャパシタバンクは複数のデジタル制御微同調キャパシタエレメントを含み、アクティブな際に各々は第2キャパシタンス値を供給する。キャパシタミスマッチの現実的な問題に対処するため、VCOチューニング範囲の全体にわたるキャパシタンスオーバーラップが、微キャパシタバンクのデジタル制御微同調キャパシタエレメントの全てがアクティブな場合に、微キャパシタバンクのキャパシタンス値が第1キャパシタンス値より大きくなるように第1及び第2キャパシタンス値を選択することによって生成される。 (もっと読む)

スプリット遅延ライン発振器における装置、システム及び方法

【課題】安全なデータ伝送を行うスプリット遅延ライン発振器における装置、システム及び方法を提供すること。

【解決手段】安全なデータ伝送を行うスプリット遅延ライン発振器における本装置は、第1装置における第1の変調/復調ブロックを有し、その第1の変調/復調ブロックは、第1の可変遅延を設定し、第1の変調/復調ブロックを通過する共有キャリア信号の周波数を変調し、第2装置における第2の変調/復調ブロックは、第2の可変遅延を設定し、第2の変調/復調ブロックを通過する共有キャリア信号の周波数を変調し、第1及び第2装置は、周波数変調された共有キャリア信号にデータを与えることで、共有する秘密情報を作成する。

(もっと読む)

電圧制御発振器、並びにそれを用いた無線通信システム及び位相同期回路。

【課題】 位相雑音特性の良好な電圧制御発振器、並びにそれを用いた無線通信システム及び位相同期回路を提供することを目的とする。

【解決手段】

電圧制御発振器10は、共振器Resと、共振器Resに入力側が接続された増幅器AMP1と、増幅器AMP1の出力側と共振器Resとの間に接続されたキャパシタC1aと、増幅器AMP1の入力側と出力側の間に、互いに直列になるように接続されたキャパシタC1bとインダクタL1を備える。さらに、共振器Resに入力側が接続された増幅器AMP2と、増幅器AMP2の出力側と共振器Resとの間に接続されたキャパシタC2aと、増幅器AMP2の入力側と出力側の間に、互いに直列になるように接続されたキャパシタC2bとインダクタL2とを備える。

(もっと読む)

PLL回路、及び無線機

【課題】 位相誤差の小さい、発振信号の精度が高いPLL回路及び無線機を提供する。

【解決手段】 第一差動信号を生成する第一発振部と、前記第一差動信号を90度の位相差をもつ第二差動信号を生成する第二発振部と、を有する電圧制御発振器と、前記第一及び第二差動信号に基づく第三差動信号の位相と、基準信号の位相とを比較する位相比較器と、前記位相比較器の比較結果に基づいて、前記電圧制御発振器を制御する制御電圧を生成するループフィルタと、を具備することを特徴とするPLL回路。

(もっと読む)

発振回路、及びこれを用いた無線受信回路、スイッチ装置

【課題】消費電力の増大と発振周波数調整に要する時間の増大とを低減しつつ、従来よりも発振周波数の調整精度を向上させることが容易な発振回路、及びこれを用いた無線受信回路、スイッチ装置を提供する。

【解決手段】パルス信号PWM1を出力すると共にパルス幅の設定を受け付けるパルス生成部PWMG1と、パルス信号PWM1を平滑して得られた直流電圧Vdc1を出力するローパスフィルタLPF1と、Vdc1を接続点P1に印加する配線25と、パルス信号PWM2を出力すると共にパルス幅の設定を受け付けるパルス生成部PWMG2と、PWM2を平滑して得られた電圧VLP2を出力するローパスフィルタLPF2と、VLP2を所定の比率に変換して直流電圧Vdc2として接続点P2に印加する電圧変換部CNV2と、接続点P1,P2間の電圧に応じた周波数の発振信号を生成する並列共振回路23を備えた。

(もっと読む)

電圧制御発振器、電圧並びにバイアス設定方法

【課題】位相雑音とDCバイアス電流特性上第1領域にて動作させることで安定した位相雑音特性を有する電圧制御発振器を得る。

【解決手段】インダクタL1、L2と可変容量素子M1、M2からなるLCタンク回路と負性抵抗を発生するバイポーラトランジスタQ1、Q2とを備える電圧制御発振器にあって、バイポーラトランジスタQ1、Q2のコレクターエミッタ間電圧VcEは、発振動作中バイポーラトランジスタのベースーエミッタ間電圧VBE以上であり、しかもバイポーラトランジスQ1、Q2タのトランジスタ耐圧BVCEO以下とするようにした。

(もっと読む)

FMチューナ

【課題】FMチューナのステレオ復調部における、パイロット信号をキャプチャするPLLを構成するVCOを、CR発振回路を用いて構成すると、温度に応じた発振周波数の変動に対応してキャプチャレンジが大きく設定される。そのため、パイロット信号の近傍周波数のノイズ等にPLLが誤って同期しやすくなる。

【解決手段】ステレオ復調部76を含むチューナ半導体チップ内に温度センサ回路94を設け、VCO部位の温度を検知する。温度センサ回路94の出力信号STPに基づいて、VCOの発振周波数fVCOを調整し、温度によるfVCOの変動を補償する。これによりキャプチャレンジの幅を、セラミックレゾネータ等を用いた場合のように狭く設定できる。

(もっと読む)

デジタル制御発振回路、周波数シンセサイザ、それを用いた無線通信機器及びその制御方法

【課題】周波数が直線的に変化する範囲が広く且つ占有面積が小さいデジタル発振回路を実現できるようにする。

【解決手段】デジタル制御発振回路10は、複数の第1の可変容量素子からなる第1の容量素子群14及び複数の第2の可変容量素子からなる第2の容量素子群14を含む可変容量部12を有し、可変容量部12の容量値に対応した発振周波数の信号を生成する発振部を備えている。第1の可変容量素子の第1の容量変化量は、第2の可変容量素子の第2の容量変化量に2以上の整数値を乗じた値であり、第2の可変容量素子の個数は、2以上の整数値から1を減じた値以上である

(もっと読む)

2位相出力電圧制御発振器

【課題】小型で低価格および高精度な位相差を持った2位相出力電圧制御発振器を提供すること。

【解決手段】1つの電圧制御発振器とハイブリッドカプラとを備え、電圧制御発振器の出力をハイブリッドカプラにより2つに分岐して互いに(π/4)異なる位相差の2信号を出力する2位相出力電圧制御発振器1であって、1つの上記電圧制御発振器回路4が多層プリント配線板上の最上層に形成され、上記ハイブリッドカプラ回路2が同じ多層プリント配線板の内層で構成されると共に、上記ハイブリッドカプラ回路2はトリプレートストリップライン導体構造を有しかつ上記多層プリント配線板内層の同一平面上に形成されていることを特徴とする。

(もっと読む)

4位相出力電圧制御発振器

【課題】小型で低価格および高精度な位相差を持った4位相出力電圧制御発振器を提供すること。

【解決手段】1つの電圧制御発振器、3つのハイブリッドカプラと1つの遅延線を備え、電圧制御発振器の出力を3つのハイブリッドカプラと1つの遅延線により4つに分岐して互いに(π/4)異なる位相差の4信号を出力する4位相出力電圧制御発振器であって、1つの電圧制御発振器回路4が多層プリント配線板上の最上層に形成され、3つのハイブリッドカプラ回路21、22、23と1つの遅延回路10が同じ多層プリント配線板の内層で構成されると共に、これ等ハイブリッドカプラ回路と遅延回路はそれぞれトリプレートストリップライン導体構造を有しかつ多層プリント配線板内層の同一平面上にそれぞれ形成されていることを特徴とする。

(もっと読む)

半導体集積回路装置

【課題】定常電流の変化に起因するVCOの位相雑音を低減し、VCO出力を安定させる。

【解決手段】半導体集積回路装置300は、バイアス電流又は発振周波数を制御して出力信号を出力する電圧制御発振器301と、前記電圧制御発振器301によって出力された出力信号に基づいて周波数制御信号を出力する位相同期回路302と、前記位相同期回路302から出力された周波数制御信号のピーク位置を検出するピーク位置検出回路303と、前記ピーク位置検出回路303によって検出されたピーク位置に基づいてバイアス電流を生成し、前記バイアス電流を出力するバイアス制御回路304と、を備え、前記電圧制御発振器301は、前記位相同期回路302によって出力された周波数制御信号に基づいて、前記バイアス制御回路304によって出力されたバイアス電流又は発振周波数を制御して出力信号を出力する。

(もっと読む)

電圧制御発振器

【課題】素子バラツキなどが生じた場合に、位相ノイズを効果的に低減することが困難であった。

【解決手段】電圧制御発振器は、電圧制御発振部へ動作電流を供給する可変電流生成回路と、インダクタと可変容量素子とで構成される共振回路を有し、可変電流生成回路の生成する電流に基づいた振幅の出力信号を出力する電圧制御発振部と、出力信号が入力され、可変電流生成回路の出力する電流の変化量に対する出力信号の振幅変化に基づいて電流設定信号を生成し、可変電流生成回路に供給する第1の最適化回路とを有する

(もっと読む)

発振回路

【課題】ノイズが少ない発振回路を提供する。

【解決手段】PNPトランジスタQ1と、PNPトランジスタQ1との間で抵抗R1,R2を介して互いのベースが接続されているNPNトランジスタQ2と、PNPトランジスタQ1のコレクタに一端L1aが接続され、NPNトランジスタQ2のコレクタに他端L1bが接続された一次巻線L1を有し、二次巻線L2が抵抗R1,R2に接続されたトランス32と、トランス32の二次巻線L2に接続された水晶振動子X1と、PNPトランジスタQ1のエミッタに正電極33が接続され、NPNトランジスタQ2のエミッタに負電極34が接続されている直流電源と、直流電源の正電極33と負電極34との間に直列接続された容量が等しい少なくとも2個のコンデンサC1〜C4とを具備し、トランス32の一次巻線L1の中点から取り出したタップと、コンデンサC1〜C4の間とから発振出力を取り出すように設けた。

(もっと読む)

1 - 20 / 42

[ Back to top ]