Fターム[5J098AC13]の内容

能動素子を用いた回路網 (5,588) | 回路特性を可変するための構成 (1,170) | 可変要素 (423) | 増幅器 (94) | 差動増幅器 (56)

Fターム[5J098AC13]に分類される特許

1 - 20 / 56

制御回路および位相変調器

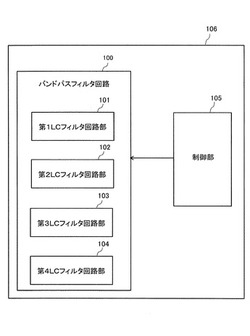

バンドパスフィルタ回路を備えた集積回路、バンドパスフィルタ回路の制御方法、その制御プログラム及びその制御方法を実行するロジック回路

【課題】センター周波数を実質的に変化させずに帯域幅を可変することが可能なバンドパスフィルタ回路を備えた集積回路、バンドパスフィルタ回路の制御方法、その制御プログラム及びその制御方法を実行するロジック回路を提供すること

【解決手段】本発明にかかる集積回路106は、楕円関数型のバンドパスフィルタ回路100及び制御部105を備える。バンドパスフィルタ回路100は、センター周波数f1を設定する第1LCフィルタ回路部101及び第4LCフィルタ回路部104、共振周波数f2、f3をそれぞれ設定する第2LCフィルタ回路部102、第3LCフィルタ回路部103を備える。前記制御部105は、第2LCフィルタ回路部102が設定するインダクタンス値L2、容量値C2及び第3LCフィルタ回路部103が設定するインダクタンス値L3、容量値C3を可変させて、共振周波数f2及びf3を、互いに増減が逆になるように変化させる。

(もっと読む)

トランスコンダクタンス調整回路、回路装置及び電子機器

【課題】トランスコンダクタンスを精度良く調整することができるトランスコンダクタンス調整回路、回路装置及び電子機器等を提供すること。

【解決手段】トランスコンダクタンス調整回路100は、第1の信号I及び第1の信号Iと位相が90度異なる第2の信号Qが入力され、第1、第2の抵抗素子RA1と、第1、第2のキャパシターCA1、CA2と、演算トランスコンダクタンス増幅器で構成される中心周波数シフト回路110と、トランスコンダクタンス調整信号AGMを出力する調整信号生成回路120とを含む。調整信号生成回路120は、第2の信号Qと第1の出力信号OIとに基づいて、又は第1の信号Iと第2の出力信号OQとに基づいて、又は第1の信号Iと第1の出力信号OIとに基づいて、又は第2の信号Qと第2の出力信号OQとに基づいて、トランスコンダクタンス調整信号AGMを生成する。

(もっと読む)

アクティブフィルタ

【課題】フィルタのQ値が変動することがないアクティブフィルタを提供する。

【解決手段】位相容量素子を含む演算増幅器、フィルタ用抵抗素子、フィルタ用容量素子、バイアス回路を含むアクティブフィルタにおいて、バイアス回路を、ゲート同士が接続されるMOSTr41、42、MOSTr41とドレイン同士が接続されるMOSTr43、MOSTr44とゲート同士が接続され、MOSTr42とドレイン同士が接続されるMOSTr44、MOSTr41またはMOSTr42のうちのいずれか1つのソースに接続される抵抗素子45、MOSTr41のドレインに接続される出力端子46またはMOSTr44のドレインに接続される出力端子47によって構成し、抵抗素子45を、フィルタ用抵抗素子と同じプロセス条件で製造し、位相補償容量素子をフィルタ用容量素子と同じプロセス条件で製造する。

(もっと読む)

位相調整回路、検出装置及び電子機器

【課題】信号の位相を高精度に調整可能な位相調整回路、検出装置及び電子機器等を提供すること。

【解決手段】位相調整回路は、位相主調整用のローパスフィルター210と、位相微調整用のハイパスフィルター230を含む。ローパスフィルター210は、周波数finの第1の信号が入力され、その周波数finにおける位相遅れ角度がX度(X≧0)となる周波数特性を有する。ハイパスフィルター230は、ローパスフィルター210からの出力信号LQに基づく第2の信号GQが入力され、周波数finにおける位相進み角度がY度(Y≧0)となる周波数特性を有する。Y度はX度よりも小さい値に設定される。

(もっと読む)

位相可変増幅器

【課題】回路規模が小型で低消費電流、出力信号の線形性に優れ、周波数特性が平坦であって、その上低ノイズの位相可変増幅器を提供する。

【解決手段】入力信号の位相を調整する移相部1、位相が調整された後の信号のゲインを増幅するゲイン可変増幅部2によって位相可変増幅器を構成する。そして、移相部1は、全域通過フィルタで構成される可変容量の容量素子103、容量素子103がエミッタとベースとの間に接続され、調整された入力信号の位相に対応する位相電流を生成するトランジスタ101を含み、可変ゲイン増幅部2は、移相電流がテール電流として供給されるトランジスタ108、トランジスタ109を含む差動対、トランジスタ109に流れる電流を電圧に変換する抵抗素子107、トランジスタ108、トランジスタ109に流れる電流を制御する制御信号を出力する制御回路106を含む。

(もっと読む)

ソースフォロワ回路、ソースフォロワ型フィルタ回路

【課題】入力MOSトランジスタのオーバードライブ電圧が低い場合でも、出力信号が歪まないソースフォロワ回路を提供することを目的とする。

【解決手段】ソースフォロワ回路を、MOSトランジスタ(Tr)1、Tr2でなるTr対、ドレインがTr1のソース及び出力端子17に接続するTr3、ドレインがTr2のソース及び出力端子18に接続するTr4でなるTr対、ゲートとドレインがTr3のゲートに接続してTr3と電流ミラーを構成するTr7、Tr7のドレインに接続してTr7に電流を供給する電流源9、ゲートとドレインがTr4のゲートに接続してTr4と電流ミラーを構成するTr8、Tr8のドレインに接続してTr8に電流を供給する電流源10、Tr7のゲートと出力端子18との間に接続される容量素子11、Tr8のゲートと出力端子17との間に接続される容量素子12によって構成する。

(もっと読む)

オペレイショナル・トランスコンダクタンス・アンプ、オペレイショナル・トランスコンダクタンス・アンプを用いたフィルタ回路

【課題】入力電圧範囲を広くしても線形性能の優れ、かつトランスコンダクタンス値精度の優れたOTA、OTAを用いたフィルタ回路を提供する。

【解決手段】I−V変換器と、内部抵抗素子の抵抗値に比例する増幅率でI−V変換器の出力電流を増幅する電流制御回路1、2とによってOTAを構成する。そして、電流制御回路1、2を、入力電流が入力されるドレイン、第1制御電圧が供給されるゲートを有するMOSトランジスタ10、出力電流が出力されるドレインを有するMOSトランジスタ13、第2制御電圧が供給されるゲートを有するMOSトランジスタ11、MOSトランジスタ10のドレインと接続される非反転入力端子、MOSトランジスタ13のゲートと接続される出力端子、MOSトランジスタ13のソース及びMOSトランジスタ11のドレインと接続される反転入力端子を有する差動増幅器12によって構成する。

(もっと読む)

半導体装置

【課題】半導体装置は、必要に応じてダイナミックレンジを確保し、且つ低消費電流化に資するフィルタ回路を備える。

【解決手段】半導体装置は、トランスコンダクタンス増幅器(103a〜103d、203a〜203d)とキャパシタ(104a、104b)から構成されるフィルタ回路(10、20)を有し、前記フィルタ回路は、妨害信号の電界強度を検出し、検出結果に基づいて、前記トランスコンダクタンス増幅器の差動入力段トランジスタのソース側のインピーダンスと前記トランスコンダクタンス増幅器のバイアス電流の双方を調整するための制御を行う。

(もっと読む)

可変利得増幅器及びそれを用いた移相器

【課題】 増幅素子の電流特性の非線形性を改善し、振幅設定精度を向上させた可変利得増幅器及びそれを用いた移相器を提供する。

【解決手段】 第2定電流源16からの電流を入力電流とし、この入力電流に比例した電流を第2カレントミラー回路17を介してエミッタ電流とする第7バイポーラトランジスタ18と、この第7バイポーラトランジスタ18の前記エミッタ電流に相応する第7バイポーラトランジスタ18のベース電流を入力電流とし、この入力電流に比例した電流を出力電流として第3バイポーラトランジスタ7及び第4バイポーラトランジスタ8のそれぞれのベースに入力する第3カレントミラー回路20とを備え、第3バイポーラトランジスタ7及び第4バイポーラトランジスタ8のそれぞれの入力電流に対する出力電流を線形とし、第2定電流源16からの電流に比例した利得を可変するようにした。

(もっと読む)

フィルタ回路

【課題】入力信号の大きさの広い範囲にあっても良好な線形性を有する高域通過フィルタ及びノッチフィルタを提供する。

【解決手段】 PMOSトランジスタ(Tr)1、Tr1とドレイン同士が接続されるTr2、ドレインがTr1のソースに接続されるTr3、Tr3がTr2のソースに接続されるTr4を有し、Tr3のゲートがTr4のドレインに接続し、Tr4のゲートがTr3のドレインに接続し、Tr3、Tr4のソースに接続される電流源5、6、Tr1、Tr2のソース間に接続されるコンデンサ8、Tr3、Tr4のソース間に接続されるコンデンサ7を含む回路29、Tr1、Tr2のゲートからTr3、Tr4のソースまでの経路において分岐された信号を出力信号に重畳し、回路29によって減衰される周波数帯域と異なる周波数帯域が減衰される信号を生成する回路100とによってフィルタ回路を構成する。

(もっと読む)

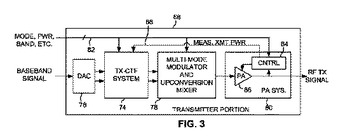

プログラム可能送信連続時間フィルタ

プログラム可能電流の送信連続時間フィルタ(TX−CTF)システムは無線周波数(RF)送信機に含まれ得る。TX−CTFの入力はベースバンド送信信号を受信することができ、TX−CTFの出力はアップコンバージョンミキサに供給されて、送信用のRFに変換され得る。TX−CTFは、フィルタパラメータをともに規定する増幅回路および受動回路を含む。TX−CTFはさらに、プログラム可能バイアス電流を増幅回路に供給するプログラム可能電流回路を含む。TX−CTFシステムはまた、1つ以上の送信機制御信号を受信し、これに応じて、TX−CTFに供給されるバイアス電流を制御する信号を生成する制御論理を含む。  (もっと読む)

(もっと読む)

フィルタ回路、連続時間フィルタ及び信号再生装置

【課題】周波数帯域を制限するフィルタ回路に関し、周波数とは、独立に利得を調整する。

【解決手段】第1の電圧/電流変換回路(12)に、係数設定回路(16)からの第1の制御信号と利得調整のための第2の制御信号とから作成した第3の信号を入力し、第2の電圧/電流変換回路(14)に、第1の制御信号を入力する。このため、周波数と、利得を独立に制御したフィルタを実現できる。

(もっと読む)

フィルタ回路及びフィルタ回路の補正方法

【課題】フィルタ回路で、製造ばらつきに対応して容易に特性周波数のずれを補正すること。

【解決手段】フィルタ回路10はgm値が制御可能なセルと、少なくとも2つのコンデンサを含むフィルタ部11を有し、2つのコンデンサの容量差を検出し、その容量差に応じて生成した制御電圧VCをフィルタ部11のgmセルに供給し、gmセルのコンダクタンス値とコンデンサの容量値との比をそれぞれ等しくする。

(もっと読む)

バランス回路

【課題】解決しようとする課題は、バランス入力増幅部の反転入力端子と、正転入力端子の入力インピーダンスの差異を無くして、同相分除去比(CMRR)の改善を図ったバランス回路を提供することである。

【解決手段】本発明では、バランス回路のバランス入力増幅部を2つ使用し、入力インピーダンスの差異があった反転入力端子と、正転入力端子に対して、バランス信号入力の各々を、一方のバランス入力増幅部の反転入力端子と他方のバランス入力増幅部の正転入力端子に交互に接続したものである。

(もっと読む)

Gm−Cフィルタをチューニングする装置および方法

チューナブルGm−Cフィルタを制御する装置であって、出力増幅器(304)の帰還符号を切り換えることによって自励発振器として再構成することのできるフィルタと、キャリブレーション構成においてフィルタの出力を検知するディジタルコントローラ(42)と、フィルタを含む相互コンダクタンス増幅器(310、320)のgm入力にアナログ制御信号(48)を提供するDAC(44)とを備える。 (もっと読む)

可変分周器

【課題】広い周波数帯域の発振信号を入力せずとも、所望の範囲の周波数帯域の発振信号を出力し、且つ高調波成分を抑えた発振信号を出力する可変分周器を提供する

【解決手段】可変分周器1aは、入力端子10及び11から入力された差動の発振信号が、ポリフェーズドフィルタ31及びポリフェーズドフィルタ32を経由する経路と、分周器21及びポリフェーズドフィルタ32を経由する経路と、分周器22、分周器21及びポリフェーズドフィルタ32を経由する経路とを有している。経路と分周器22の分周比を選択することで、入力発振信号に対して1倍、2分の1倍、4分の1倍及び6分の1倍の発振信号を生成することができ、更に、ポリフェーズドフィルタを最終段に備えることで、分周により発生する高調波等の不要な信号を除去した広い周波数帯域の4相の発振信号を出力端子12〜15から出力することが可能となる。

(もっと読む)

キャパシタンス乗算器回路

キャパシタンス乗算器回路が、追加の回路を追加することまたは追加の電力を必要とすることなしにキャパシタンス乗算器効果を達成するために、回路のRCフィルタ中のキャパシタを通る電流を検知し、その電流を乗算するように構成される。回路は、RCフィルタと、フィルタ出力に接続された第1の信号経路と、フィルタに入力に接続された第2の信号経路とを含む。フィルタを通る電流出力(iout)は、2つの経路に分割され、第1の経路において検知され、第2の経路において乗算される。乗算された電流は、キャパシタCの実効キャパシタンスを上げるために第2の経路からフィルタ入力にフィードバックされる。キャパシタンス乗算器回路は、フィルタ中のキャパシタの実効キャパシタンスを上げる際に、全体的な回路の周波数応答、直線性性能および/または安定性に影響を及ぼさない。  (もっと読む)

(もっと読む)

撮像装置及び当該装置におけるインピーダンス整合方法

【課題】 従来は、インピーダンスの整合を適切なタイミングで行うことにより、ノイズの影響を受けにくくする方法については考慮されていない。

【解決手段】 インピーダンス整合のための基準となる抵抗値を有する外部抵抗器260,261と、外部抵抗器が接続された端子の出力インピーダンスを、その外部抵抗器の抵抗値に対応して整合させるインピーダンス整合回路と、インピーダンス整合回路でインピーダンス整合を行わせるか否かを制御する制御信号280を生成する信号生成回路とを有する。

(もっと読む)

電気分散等化回路

【課題】各信号経路における遅延時間、帯域を所望の値に容易に調整可能なFFE型の電気分散等化回路を提供する。

【解決手段】縦列接続され、入力端子INからの入力信号を一定の遅延時間ずつ順次遅延させる第1〜第3の遅延回路11〜13と、入力端子IN、各遅延回路それぞれから入力される入力信号をあらかじめ指定したタップ係数a1〜a4それぞれと乗算する第1〜第4の乗算回路21〜24と、各乗算回路それぞれから入力される入力信号を順次加算した結果を出力する第1〜第3の加算回路31〜33と、を少なくとも備え、かつ、各乗算回路の出力信号線と接地部との間に電気容量C1〜C4を接続し、電気容量C1〜C4の容量値を所望の特性が得られるように調整する。なお、第1〜第3の遅延回路11〜13、第1〜第4の乗算回路21〜24の各回路のうち、少なくとも一部の回路の出力信号線にまたは回路内に電気容量を接続する構成であっても良い。

(もっと読む)

1 - 20 / 56

[ Back to top ]