Fターム[5J098AD28]の内容

能動素子を用いた回路網 (5,588) | 目的と効果 (843) | 生産性の向上、コストダウン、設計能率向上 (35)

Fターム[5J098AD28]の下位に属するFターム

バラツキの縮小、製造精度の向上、無調整化 (23)

検査や試験の能率向上 (3)

Fターム[5J098AD28]に分類される特許

1 - 9 / 9

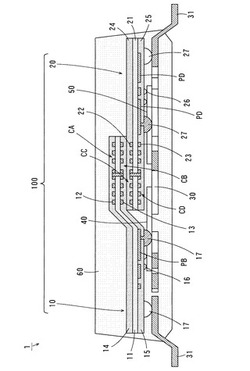

アイソレータ用回路基板、アイソレータおよびそれらの製造方法

【課題】コイルの設計の自由度の向上および小型化が可能でかつ容易に製造可能なアイソレータ用回路基板およびアイソレータならびにそれらの製造方法を提供することである。

【解決手段】回路基板10の上面にコイルCAが形成される。回路基板10の下面にコイルCBおよび配線パターンPBが形成される。回路基板20の上面にコイルCCが形成される。回路基板20の下面にコイルCDおよび配線パターンPDが形成される。複数のコイルCA,CB,CC、CDが互いに重なるように回路基板10,20が配置される。コイルCA,CB,CC,CDが送信チップ40および受信チップ50に重なるように回路基板10,20が送信チップ40上、受信チップ50上およびリードフレーム30上に配置される。

(もっと読む)

減衰器

【課題】減衰量の周波数依存性を改善することができる減衰器を提供すること。

【解決手段】減衰器10は、FET11〜13、インダクタ14及び15、抵抗16、入力端子17、出力端子18を備え、入力端子17には、FET11のドレイン電極と、FET12のドレイン電極と、インダクタ14の一方端とが接続され、出力端子18には、FET11のソース電極と、FET13のドレイン電極と、インダクタ15の一方端とが接続され、FET11のドレイン電極とソース電極との間にインダクタ14と、抵抗16と、インダクタ15とが直列に接続された構成を有する。

(もっと読む)

スイッチトキャパシター回路を用いたハイパスフィルター及び電子機器

【課題】設計の自由度を失うことなく、SC回路を構成するスイッチのクロック周波数を高く、且つカットオフ周波数を低くする場合において面積をより小さくできるSC回路を用いたHPF等を提供する。

【解決手段】スイッチトキャパシター回路を用いたM(Mは2以上の整数)次のハイパスフィルターは、第1の入力端、第2の入力端及び出力端を備える第1のオペアンプOP1と、第1の入力キャパシターC1と、出力端から帰還される帰還信号に対してハイパスフィルターのゲイン調整を行うゲイン調整回路GA1とを有する第1のスイッチトキャパシター積分器1001を含み、第1の入力端に、ハイパスフィルターの入力信号VINが供給され、第2の入力端に、帰還信号が第1の入力キャパシターC1を介して供給され、出力端からハイパスフィルターの出力信号VOUTが出力される。

(もっと読む)

スイッチトキャパシター回路を用いたハイパスフィルター及び電子機器

【課題】設計の自由度を失うことなく、SC回路を構成するスイッチのクロック周波数を高く、且つカットオフ周波数を低くする場合において面積をより小さくできるSC回路を用いたHPF等を提供する。

【解決手段】スイッチトキャパシター回路を用いたM(Mは2以上の整数)次のハイパスフィルター10は、第1の入力端、第2の入力端及び出力端を備える第1のオペアンプをOP1と、第1の入力キャパシターC1とを有する第1のスイッチトキャパシター積分器1001を含み、第1の入力端に、前記ハイパスフィルター10の入力信号VINが供給され、第2の入力端に、出力端から帰還された帰還信号が第1の入力キャパシターC1を介して供給され、出力端からハイパスフィルター10の出力信号VOUTが出力される。

(もっと読む)

フィルタ回路及びフィルタ回路の補正方法

【課題】フィルタ回路で、製造ばらつきに対応して容易に特性周波数のずれを補正すること。

【解決手段】フィルタ回路10はgm値が制御可能なセルと、少なくとも2つのコンデンサを含むフィルタ部11を有し、2つのコンデンサの容量差を検出し、その容量差に応じて生成した制御電圧VCをフィルタ部11のgmセルに供給し、gmセルのコンダクタンス値とコンデンサの容量値との比をそれぞれ等しくする。

(もっと読む)

アイソレータ用回路基板、アイソレータおよびアイソレータの製造方法

【課題】製造工程が簡略化されたアイソレータ用回路基板、アイソレータおよびアイソレータの製造方法を提供する。

【解決手段】ベース絶縁層1の上面および下面に金属層M1,M2がそれぞれ形成されている。金属層M1は、コイル2、複数の接続パッド3および複数の接続パッド4を含む。金属層M2は、コイル5および接続パッド6,7を含む。ベース絶縁層1には、貫通孔1a,1bが形成される。接続パッド3上に実装される受信チップ11の端子部11aがワイヤW1を介してベース絶縁層1の貫通孔1a内で露出する接続パッド6の部分にボンディングされ、端子部11bがワイヤW2を介してベース絶縁層1の貫通孔1b内で露出する接続パッド7の部分にボンディングされる。

(もっと読む)

無線受信機用半導体装置

【課題】マルチバンド無線受信機のバンドパスフィルタを集積回路で構成する場合に、回路規模が大きくなり、チップ面積が大きくなったり、製造コストが高くなる。

【解決手段】混合回路58は無線受信信号SRFをダウンコンバートして中間信号SIFを生成する。IFBPF60は、抵抗R及びキャパシタCを用いたRCアクティブフィルタで構成され、SIFから目的受信信号を抽出する。抵抗Rは、クロック信号SCLによって駆動されるスイッチトキャパシタからなる等価抵抗により構成される。SCLを生成するフィルタ制御クロック生成回路72は、SCLの周波数fCLを、目的受信信号が属するバンドに応じて切り換えることができる。IFBPF60の通過帯域は、クロック周波数fCLによる抵抗Rの等価抵抗値の切り換えにより、受信バンドに対応して変更できる。

(もっと読む)

改善されたガルバニックアイソレータ

【課題】ガルバニックアイソレータのコストを低減する。

【解決手段】分割回路要素、ポリマー基板、送信器、及び受信器を有するガルバニックアイソレータを開示した。前記分割回路要素は、第1及び第2の部分を有し、該第1の部分は、前記基板の第1の表面上に配置されており、該第2の部分は、前記基板の第2の表面上に配置されている。前記送信器は、入力信号を受信して、該入力信号から引き出した信号を前記第1の部分に結合する。前記受信器は、前記回路要素の前記第2の部分に接続されており、外部回路に結合される出力信号を生成する。ガルバニックアイソレータを、従来のプリント回路基板及びフレキシブル回路基板上において経済的に製造することができる。

(もっと読む)

動的カットオフ周波数可変フィルタ

方法および装置を開示する。本方法は、少なくとも1つの過去のセンサ測定値の記憶装置と、潜在的カットオフ周波数の記憶装置と、フィルタとを含む。各潜在的カットオフ周波数には、センサ測定値と記憶されている過去のセンサ測定値との間のそれぞれの潜在的な差が関連付けられている。フィルタは、記憶されている過去のセンサ測定値と現センサ測定値との間の差に基づいて、記憶されている潜在的カットオフ周波数から動的に選択されたカットオフ周波数を有する。本方法は、現センサ測定値と過去のセンサ測定値との間の差を判定するステップと、この差から現センサ測定値に対するフィルタのカットオフ周波数を選択するステップとを含む。  (もっと読む)

(もっと読む)

1 - 9 / 9

[ Back to top ]