Fターム[5J098AD29]の内容

能動素子を用いた回路網 (5,588) | 目的と効果 (843) | 生産性の向上、コストダウン、設計能率向上 (35) | バラツキの縮小、製造精度の向上、無調整化 (23)

Fターム[5J098AD29]に分類される特許

1 - 20 / 23

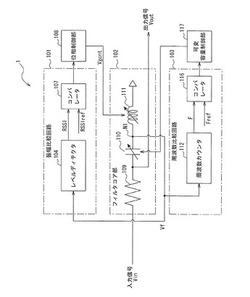

フィルタ装置およびその制御方法

【課題】フィルタのノッチ周波数を調整する機能を持ったフィルタ装置を提供する。

【解決手段】入力信号を抵抗109と可変容量110、アクティブインダクタ111を備えたフィルタコア部102にて分圧し、フィルタコア部102のフィルタ特性信号Vfの振幅と基準振幅とを比較する振幅比較回路101、振幅比較回路101での比較結果に基づいてアクティブインダクタ111の位相を制御する位相制御部108、フィルタコア部102のフィルタ特性信号Vfの周波数と基準周波数とを比較する周波数比較回路103、周波数比較回路103の比較結果に基づいて可変容量110の容量を制御する可変容量制御部117によってフィルタ装置を構成し、アクティブインダクタ111の位相、可変容量11の容量が制御される間、アクティブインダクタ111の位相制御部108が、フィルタコア部102を発振させる。

(もっと読む)

アクティブフィルタ

【課題】フィルタのQ値が変動することがないアクティブフィルタを提供する。

【解決手段】位相容量素子を含む演算増幅器、フィルタ用抵抗素子、フィルタ用容量素子、バイアス回路を含むアクティブフィルタにおいて、バイアス回路を、ゲート同士が接続されるMOSTr41、42、MOSTr41とドレイン同士が接続されるMOSTr43、MOSTr44とゲート同士が接続され、MOSTr42とドレイン同士が接続されるMOSTr44、MOSTr41またはMOSTr42のうちのいずれか1つのソースに接続される抵抗素子45、MOSTr41のドレインに接続される出力端子46またはMOSTr44のドレインに接続される出力端子47によって構成し、抵抗素子45を、フィルタ用抵抗素子と同じプロセス条件で製造し、位相補償容量素子をフィルタ用容量素子と同じプロセス条件で製造する。

(もっと読む)

フィルタ

【課題】従来に比して格段的に特性のばらつきを小さくすることができるフィルタを提供する。

【解決手段】入力信号Vinの周波数特性を補正して出力するフィルタ部22と、フィルタ部22の特性を制御する制御部23とを備えるようにする。フィルタ部22は、制御電流ICNTにより相互コンダクタンスを可変して入力電圧に応じた電流を出力するトランスコンダクタンス回路24を使用したジャイレータ方式のフィルタ回路であり、制御部23は、制御用のクロック信号CLKを周波数電流変換して制御電流ICNTを生成する。

(もっと読む)

イコライザ回路及び受信装置

【課題】回路を構成する素子の特性バラツキの影響を受けることなく、信号伝送で減衰した成分が補償された良好な信号が得られるイコライザ回路を提供する。

【解決手段】入力される電圧信号をトランスコンダクタンスにより電流に変換して、その出力に応じて各容量負荷の充放電を行い、容量負荷毎に期間を異ならせて、電圧信号に応じた電流による容量負荷からの電荷の引き抜きと電圧信号に応じた電流による容量負荷への電荷の注入とを行うようにして、デジタルフィルタにおけるハイパスフィルタの機能を実現し、素子の特性バラツキの影響を受けることなくイコライズ機能を実現できるようにする。

(もっと読む)

終端抵抗調整回路

【課題】入力差動信号のコモン電圧が変化しても、終端抵抗を一定に保持でき、かつ、簡易な回路構成の終端抵抗調整回路。

【解決手段】抵抗値を調整可能な第1の終端抵抗回路と、第1の終端抵抗回路と並列に接続され、抵抗値を調整可能な第2の終端抵抗回路と、第1及び第2の終端抵抗回路の抵抗値を調整するための調整用抵抗回路と、調整用抵抗回路により定まる第1の電圧と、外部に接続された基準抵抗により定まる第2の電圧とが入力され、両電圧が等しくなるように動作するとともに、第1及び第2の終端抵抗回路に対し抵抗調整信号を出力する第1の増幅回路と、第1の終端抵抗回路が接続された第1の端子と、第2の終端抵抗回路が接続された第2の端子と、第1及び第2の端子に与えられる差動信号のコモン電圧に基づく電圧と、第1又は第2の電圧とが入力され、両電圧が等しくなるように動作する第2の増幅回路と、を備える終端抵抗調整回路。

(もっと読む)

寄生容量により誘導される誤差が減少されたセンサデバイス

デバイス110は、駆動ノード34,36および感知ノード42,44を有する感知素子26を備えている。駆動ノード34および感知ノード42との間には寄生容量22が存在する。同様に、駆動ノード36と感知ノード44との間には寄生容量24が存在する。駆動信号56が駆動ノード34、36との間に印加されると、駆動ノード34と感知ノード42との間の寄生電流70および駆動ノード36と感知ノード44との間の寄生電流72が寄生容量22,24のおかげで生成される。容量性ネットワーク112を介して寄生電流70を打ち消す補正電流134を生成するために、駆動ノード36と感知ノード42との間に容量ネットワーク112が接続される。同様に、容量性ネットワーク112を介して寄生電流72を打ち消す補正電流138を生成するために、駆動ノード34と感知ノード44との間に容量性ネットワーク114が接続される。  (もっと読む)

(もっと読む)

抵抗値補正回路

【課題】外付けの基準抵抗と半導体集積回路に形成した抵抗の遅延量を比較して、半導体集積回路に形成した抵抗の抵抗値を補正する抵抗値補正回路を提供する。

【解決手段】半導体集積回路に形成した抵抗29と半導体集積回路の外部に設けられた基準抵抗33に予め設定された周期のクロック信号を入力し、抵抗29から出力された第1の信号A1と基準抵抗33から出力された第2の信号A2との遅延差を検出する遅延判定回路3と、直列接続される複数のフリップフロップにより構成されるフリップフロップ部に、遅延判定回路3で遅延差を計測開始と同時にクロック信号を入力し、フリップフロップごとに順次クロック信号を遅延させ、フリップフロップごとに遅延信号を出力し、遅延差が発生している期間に出力された遅延信号を選択して出力するばらつき検出回路と、を備える抵抗値補正回路1である。

(もっと読む)

低域ろ波回路

【課題】容量素子の小型化を図る低域ろ波回路(ループフィルタ)において、容量素子としてMOS容量を使用した場合の電圧依存によるPLL応答特性のばらつきと、MOS容量として薄膜ゲートトランジスタを使用した場合のゲートリーク電流によるジッタ特性の劣化を抑制する。

【解決手段】ループフィルタは、第1の容量素子31と、この容量素子31に直列に接続された抵抗素子32及び第2の容量素子33とを備える。前記第1の容量素子31の一端に接続された第1の入力端IN1に第1の電流(Ip/10)を与え、前記第1の容量素子31の他端に接続された第2の入力端IN2に第2の電流(Ip/10)を与えることにより、第1の容量素子31の小型化が図られる。前記抵抗素子32に直列に接続された可変電圧電源35は、電圧制御端子36から、第1の容量素子31の両端の印加電圧が一定になるように制御される。

(もっと読む)

ばらつき調整回路

【課題】回路構成が簡単で、かつ、小型化が可能なばらつき調整回路を提供することを目的とする。

【解決手段】複数の単位遅延回路27により構成されるばらつき調整用遅延回路3と、ばらつき調整用遅延回路3に信号Aが入力されると、クロック信号CLKのクロック毎に、信号C〜Iを順番に出力していくフリップフロップ10〜17と、ばらつき調整用遅延回路3から信号Bが出力された後に、対応するフリップフロップから出力される信号が入力されると、選択信号Q0〜Q7の何れかを出力するフリップフロップ18〜25と、フリップフロップ18〜25のうち連続して信号を出力する2つのフリップフロップからそれぞれ出力される各信号の排他的論理和を演算し、その演算結果に基づいて、遅延回路2の遅延時間を調整する制御回路26とを備えてばらつき調整回路1を構成する。

(もっと読む)

ノイズフィルタ回路、およびその方法、ならびに、サーマルヘッドドライバ、サーマルヘッド、電子機器、および印刷システム

【課題】 簡易な構造を有するノイズフィルタ回路等を提供する。

【解決手段】 ノイズフィルタ回路(10;60)は、入力信号(IN)を入力するラッチ回路(14;64)を備える。ラッチ回路(14;64)は、第1および第2の論理演算回路(たとえば、NAND回路)を含む。第1および第2のNAND回路のそれぞれにおいて、セット信号(S)またはリセット(R)信号を入力するP型トランジスタ(P1)の能力は、セット信号(S)またはリセット(R)信号を入力するN型トランジスタ(N1)の能力、および、このN型トランジスタ(N1)と直列に接続されるN型トランジスタ(N2)の能力(トータルな能力)より低い。ノイズフィルタ回路(10;60)は、ラッチ回路(14;64)からの出力信号(OUT(XQ;Q))を入力する波形整形回路(16)を、備えてもよい。

(もっと読む)

可変抵抗器及びこれを用いたフィルタ、可変利得増幅器及び集積回路

【課題】チューニング回路を必要とせずに位相遅れのばらつきを抑制可能な可変抵抗器を提供する。

【解決手段】シリコン基板上に形成され、入力端子と出力端子との間の抵抗値が変化する可変抵抗器において、前記入力端子にそれぞれの一端が共通に接続される複数の第1の抵抗Rと;前記第1の抵抗よりも小さな抵抗値を持ち、前記第1の抵抗の他端にそれぞれの一端が共通に接続される複数の第2の抵抗rと;前記入力端子と前記出力端子との間に挿入され、前記第1の抵抗から1つの抵抗を選択し、選択した第1の抵抗の他端に接続されている第2の抵抗から少なくとも1つの抵抗を選択するスイッチ部と;を具備する。

(もっと読む)

受信機

【課題】サンプリングフィルタを備えた受信機において、受信信号の同相成分と直交成分との振幅誤差や直交誤差による受信性能劣化を防ぐことのできる受信機を得る。

【解決手段】受信信号をフィルタリングするフィルタ部4と、復調部6を含む復調経路に設けられて受信信号の同相成分のI信号と直交成分のQ信号との振幅誤差および直交誤差を検出するIQ誤差検出部7と、IQ誤差検出部7により検出された誤差情報に基づいてフィルタ部4を制御する制御部8とを備えている。

(もっと読む)

MOS抵抗制御装置、MOS減衰器、無線送信機

【課題】MOS減衰器としての可変特性を所望に合わせ込んでそのばらつきを吸収することが可能なMOS抵抗制御装置、これを用いる無線送信機を提供すること。

【解決手段】ソースが第1の基準電位に接続されたMOSトランジスタと、該MOSトランジスタのドレインと第2の基準電位との間に挿入・接続された第1の制御電流源と、第1、第2の入力端、および出力端を有し、該第1の入力端がMOSトランジスタのドレインと第1の制御電流源との接続ノードに接続され、該出力端がMOSトランジスタのゲートに接続されたオペアンプと、該オペアンプの第2の入力端に一端が接続されたインピーダンス素子と、該インピーダンス素子に一端の側から電流を入力する基準電流源と、インピーダンス素子に一端の側からさらに電流を入力する第2の制御電流源と、MOSトランジスタのドレインに電流を入力する第3の制御電流源とを具備する。

(もっと読む)

利得制御フィルタ装置、利得制御複素フィルタ装置および受信装置

【課題】アクティブフィルタのSNを確保するために、フィルタ回路への入力信号レベルを一定にする利得制御機能を有する利得制御フィルタ装置を提供する。

【解決手段】反転入力端、非反転入力端、反転出力端および非反転出力端を有するアクティブフィルタ回路241と、アクティブフィルタ回路241の非反転入力端、反転入力端に至る第1および第2の入力路に挿入され第1の制御電圧によって抵抗値が制御される可変抵抗回路221とを備え、第1の制御電圧を変化させることによって利得を制御する。

(もっと読む)

フィルタ回路及び半導体集積回路装置

【課題】Gmセルが有するコンダクタンスのばらつきの影響を受けず、フィルタの電圧利得のばらつきが抑制されるGm−Cフィルタを提供する。

【解決手段】フィルタ回路は、第1回路と、第2回路と、第3回路とを具備する。第1回路は、差動入力信号の一方の信号である第1入力信号と、差動出力信号の一方の信号である第1出力信号とを入力し、第1入力信号と第1出力信号との電圧差を所定のコンダクタンスに応じて電流に変換し、電流に変換された差動信号を出力する。第2回路は、差動入力信号の他方の信号である第2入力信号と、差動出力信号の他方の信号である第2出力信号とを入力し、第2出力信号と第2入力信号との電圧差を所定のコンダクタンスに応じて電流に変換し、電流に変換された差動信号を出力する。第3回路は、第1回路から出力される差動信号と第2回路から出力される差動信号とを合成した合成差動信号を入力し、差動出力信号を出力する。

(もっと読む)

フィルタ装置およびこれを用いた半導体装置

【課題】CR積のバラツキを検出してフィルタ装置の周波数特性のバラツキを補正し、周波数特性を一定とする。

【解決手段】基準フィルタ12のスイッチ28は抵抗21,22、スイッチ29は抵抗23,24のどちらかを選択、この抵抗は基準信号周波数選択回路7の周波数選択信号gにて決定される。周波数選択信号gは基準信号aの周波数を識別する信号で、周波数識別信号iが基準信号周波数選択回路7に入力され、出力される周波数選択信号gを用いて基準フィルタ12の群遅延量が入力される基準信号aの周波数に反比例するように制御する。このため基準信号aの周波数が違ってもカウンター出力信号eは変わらず、主フィルタ6では同じスイッチがオンする。基準信号aに対して主フィルタ6のCR積のバラツキに応じた最適な設定したとき、基準信号aの周波数を変えても主フィルタ6の最適な設定が選択され、主フィルタ6の周波数特性は補正され一定となる。

(もっと読む)

遅延回路及びリングオッシレータ型電圧制御発振回路

【課題】遅延回路1を構成するトランジスタ素子のばらつきの影響を低減し、少ない余裕で発振周波数可変範囲を確保する。

【解決手段】第2のトランジスタQ2に対してソース同士、ドレイン同士が接続された第3のトランジスタ素子Q3と、前記第3のトランジスタ素子Q3のゲートに接続され、当該ゲートにトランジスタ素子の特性のバラツキを補正するためのバイアス電圧を印加するためのバイアス生成回路10とを備える。前記バイアス生成回路10は、遅延回路1と同一の基板から形成された少なくとも1つのトランジスタ素子Q6を備え、このトランジスタ素子Q6を用いて前記バイアス電圧を生成する。

(もっと読む)

フィルタ自動調整回路およびフィルタ調整方法ならびに携帯電話システム

【課題】特性周波数の調整機能を有するフィルタに対して、高い調整精度を持ちかつ容易に低消費電流化を実現したバラツキ補正を可能にし、フィルタ調整誤差を確実に抑えることができるフィルタ自動調整回路およびフィルタ調整方法ならびに携帯電話システムを提供する。

【解決手段】基準フィルタ103のバラツキを検出するために、位相差検出器104により、基準フィルタ103における前後の位相差をカウンタ106にてカウントする際に、一種類の基準信号でなく、位相器110で作成した複数個の基準信号を用いてカウントし、このカウント結果から得られる信号を、主フィルタ109の制御信号116(1)〜116(n)としてレジスタ108に保持することにより、主フィルタ103のバラツキ調整後は、フィルタ調整に関する部材のすべての動作を停止させる。

(もっと読む)

電圧電流変換回路及びアナログフィルタ回路

【課題】寄生容量を変化させずに出力電流を停止する。

【解決手段】所定の定電流を供給する第1(12,14)及び第2電流源(11,13)と、前記第1電流源と直列に接続され、制御電極に第1入力電圧(Vin−)が印加される第1トランジスタ(18)と、前記第2電流源と直列に接続され、制御電極に第2入力電圧(Vin+)が印加される第2トランジスタ(17)とを有し、前記第1入力電圧及び前記第2入力電圧に応じて動作する差動回路と、を備え、前記第1電流源と前記第1トランジスタとの間から、前記第1電流源から供給される前記定電流と、前記第1トランジスタを流れる電流とに応じた第1出力電流(Iout+)を出力する電圧電流変換回路であって、前記第1トランジスタの入力電極と、前記第2トランジスタの入力電極とを電気的に接続することにより前記第1出力電流を停止するスイッチ回路を、更に備える。

(もっと読む)

低電圧差動信号受信器及びそれの終端抵抗値の設定方法

【課題】低電圧差動信号受信器及びそれの終端抵抗値の設定方法を提供する。

【解決手段】低電圧差動信号受信器は、外部から提供される基準電圧を感知して第1信号を出力する第1受信部、抵抗制御コードに基づいて可変される可変終端抵抗部の両端に外部から提供される基準電流によって形成される電圧を感知して第2信号を出力する第2受信部を含む。低電圧差動信号受信器は、第1信号と第2信号とを比較してカウンタ制御信号を出力する比較部及びカウンタ制御信号に応答して可変終端抵抗部の抵抗値を変動させるための抵抗制御コードを可変終端抵抗に出力するアップ/ダウンカウンタ部を更に含む。アップ/ダウンカウンタ部は、可変終端抵抗部に抵抗制御コードを提供する。

(もっと読む)

1 - 20 / 23

[ Back to top ]