Fターム[5J104AA43]の内容

暗号化、復号化装置及び秘密通信 (108,990) | 目的、効果 (22,786) | 暗号破りへの対策 (431) | 暗号鍵の性質を利用した暗号破りを対象 (99)

Fターム[5J104AA43]に分類される特許

1 - 20 / 99

半導体装置及びICカード

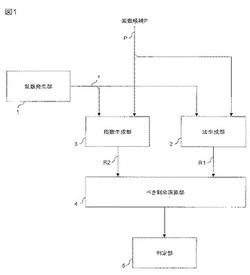

【課題】暗号に対するサイドチャネル攻撃から防御するために、素数性判定を行う半導体装置において、素数の漏えいを防止する。

【解決手段】素数性判定におけるべき剰余演算において、従来の指数のランダム化に加え、法をもランダム化する。乱数発生部により発生した乱数をランダム化数として、法生成部と指数生成部に入力する。法生成部と指数生成部は、ランダム化数を用いて素数候補Pをランダム化し、ランダム化された法R1と指数R2を生成する。ランダム化された法R1と指数R2を用いて素数性判定のためのべき剰余演算を実行し、その結果に基づいて、素数性候補Pの素数性を判定する。半導体装置の素数性判定中の消費電力が、判定対象の素数候補の値と無相関となり、サイドチャネル攻撃による素数の漏えいを防止することができる。

(もっと読む)

暗号処理装置

【課題】回路規模や消費電力の増大を抑えながら、サイドチャネル攻撃を無効化できる暗号処理装置を提供する。

【解決手段】第1線形変換部、第2線形変換部は、マスクデータを線形変換する。第1算出部は、処理対象データと第1線形変換部により線形変換された第1マスクデータとに基づいて第1データを算出する。選択部は、第1データと第2線形変換部により線形変換された第2マスクデータのいずれかを選択する。非線形変換部は、選択された第1データまたは第2マスクデータを非線形変換する。第2算出部は、非線形変換された第1データとマスクデータとに基づいて第2データを算出する。第3線形変換部は、第2データを線形変換する。そして、第3線形変換部により線形変換された第2データが新たな処理対象データとして保持され、非線形変換された第2マスクデータが新たなマスクデータとして保持される。

(もっと読む)

サイドチャネル攻撃に対抗する方法

【課題】

本発明は、サイドチャネル攻撃に対抗する方法に関する。当該方法は、中間変数をマスクするためのブロック暗号アルゴリズムを実行することから成り、このブロック暗号アルゴリズムは、1つ以上の非線形関数を有する。

【解決手段】

この課題は、前記1つ以上の非線形関数のうちの少なくとも1つの非線形関数が、マッチ・イン・プレース関数を使用して実行されることによって解決される。

(もっと読む)

暗号処理装置

【課題】1Round演算を1クロックサイクルで実行し、なおかつ、回路規模の増大を抑え、DPA耐性の向上を図ることが可能な暗号処理装置を提供する。

【解決手段】第1レジスタ105と、第2レジスタ106と、非線形変換部としてSboxを有し、第2レジスタの格納値に対してラウンド演算を行うラウンド演算部109と、初期置換された第1データと所定の攪乱値とのEXORを行う第1演算部102と、初期置換された第2データと所定の攪乱値とのEXORを行う第2演算部103と、第1レジスタの格納値に対して逆置換を行う逆置換部107と、逆置換した値と所定の攪乱値とのEXORを行い、演算結果をラウンド演算部に供給する第3演算部109と、を有し、ラウンド演算部109は、Sboxにて、第2レジスタに格納された格納値の攪乱状態を解除した値を入力として、非線形変換処理を行い、Sboxの処理結果と第3演算部の演算結果とのEXORした結果を第2レジスタに出力する。

(もっと読む)

暗号処理装置及び暗号処理回路の制御方法

【課題】サイドチャネル情報を用いた電力差分解析又は電磁波等の解析による攻撃への対策を施し、かつ、回路規模増加を抑えること

【解決手段】本発明にかかる暗号処理装置は、平文又はラウンド処理結果である入力データを複数の部分データに分割する分割部と、複数の部分データのそれぞれを保持するための複数のデータ保持部と、複数のデータ保持部に保持された複数の部分データからラウンド処理の対象となる一つのラウンド処理対象データに結合する結合部と、を備え、分割部は、複数の部分データのそれぞれの格納先を複数のデータ保持部の中から選択し、複数の部分データのそれぞれについて、当該選択した格納先へ格納し、結合部は、分割部により選択された各部分データの格納先に応じて、入力データを復元するように複数の部分データからラウンド処理対象データに結合する。

(もっと読む)

暗号装置及び暗号プログラム

【課題】キャッシュ攻撃などに対してデータ処理装置などを保護する。

【解決手段】入力データ列の暗号化処理又は復号処理を行う際にサイドチャネル攻撃の対象となる可能性のある処理ブロックを有するデータ処理装置に対し、正規の暗号化処理又は復号処理の際に前記処理ブロックに入力される正規データ列と異なる擬似データ列を所定のルールに基づいて生成し、生成した擬似データ列を正規データ列に代えて処理ブロックへ入力し、処理ブロックと等価の擬似処理ブロックと擬似データ列を生成する際に用いた基礎データを擬似処理ブロックに入力して補正データを生成し、擬似データ列の入力により前記処理ブロックで実行される擬似的な暗号化処理又は復号処理による擬似結果データを補正データで補正することで、当該擬似結果データを正規の暗号化処理又は復号処理により得られる結果データと同じ内容に補正する。

(もっと読む)

ガロア体の逆元演算回路

【課題】ダイナミックハザードに起因する消費電力の増加を一様に抑えて、DPA攻撃を困難にする。

【解決手段】8ビットの入力データは4つのデコーダ111乃至114によって2ビットずつデコードされ、それぞれ4ビットずつ計16ビットのデコードデータとなる。演算部120はデコードデータに対してGF(((22)2)2)逆元演算を行う。演算結果は4つのエンコーダ131乃至124によって4ビットずつエンコードされ、それぞれ2ビットずつ計8ビットの出力データとなる。デコーダ111乃至114は共通の制御信号PCdlyに同期して演算開始前に固定値「0000」を一旦出力した後に、入力データに応じて何れか1ビットのみを「1」に変化させる。演算部120は固定値が入力されると固定値を出力し、固定値以外が入力されると演算結果を出力する。これにより、中間値への遷移を抑止する。

(もっと読む)

暗号鍵解析方法、暗号鍵解析装置および暗号鍵解析プログラム

【課題】記憶容量が圧迫されずに、暗号鍵を解くこと。

【解決手段】所定の点に対して自己同型写像を適用して算出した第1の点の集合の中から代表点を選択して記憶部に記憶させる。この集合に関する代表点に対して擬似乱数を用いて算出した点に対して自己同型写像を適用することで、第1の点の集合に関する新たな代表点を記憶部に追加して記憶させる。また、所定の暗号鍵から定まる点に対して自己同型写像を適用して算出した第2の点の集合の中から代表点を記憶部に記憶させる。この集合の点に関する代表点に対して擬似乱数を用いて点を算出し、点に対して自己同型写像を適用することで、第2の点の集合の新たな代表点を記憶部に追加して記憶させる。そして、第1および第2の点の集合に関する各代表点のうち、一致した代表点に基づいて暗号鍵を算出する。

(もっと読む)

暗号化装置および復号装置

【課題】回路規模を増加させずにサイドチャネル攻撃に対して安全な暗号化装置を提供する。

【解決手段】AES暗号方式の暗号化装置100であって、鍵情報を用いてデータを演算するラウンドのうち、最初のラウンドで、AddRoundKeyと、SubBytesと、MixColumnsとをこの順序で含む演算を行い、最後の1つ前のラウンドで、MixColumnsと、AddRoundKeyと、SubBytesとをこの順序で含む演算、または、AddRoundKeyと、MixColumnsと、SubBytesとをこの順序で含む演算を行い、最後のラウンドで、AddRoundKeyを含む演算を行う演算部を備える。

(もっと読む)

暗号処理装置

【課題】DPA攻撃に対する耐性を高めることのできる、暗号処理装置および暗号処理方法を提供する。

【解決手段】処理対象データを取得し、前記処理対象データにラウンド処理を施して中間データを生成する、ラウンド処理部と、乱数データを生成する乱数データ生成部と、前記中間データまたは前記乱数データを格納する記憶回路と、前記記憶回路に前記中間データと前記乱数データとのうちのどちらを格納するかを選択する選択制御部とを具備する。前記選択制御部は、前記中間データが格納された後に前記乱数データが格納されるように、前記記憶回路に格納するデータを選択する。

(もっと読む)

複数のナップザックを用いる公開鍵暗号方式による暗号システム、鍵生成装置、暗号化装置、復号装置、データ交換方法およびプログラム

【課題】 高い安全性および処理の高速性を実現するナップザック暗号方式を提供すること。

【解決手段】 本発明の暗号システムは、個々は超増加性を示さない複数の秘密鍵数列を、数列それぞれの要素を変数として非線形関数により組み合わせると超増加性を満たすという条件のもと、生成する秘密鍵生成手段と、法と、法と互いに素な複数の乗数とをさらに秘密鍵として定めて、複数の秘密鍵数列それぞれの要素をモジュラ変換し、複数の公開鍵数列を生成する公開鍵生成手段とを含む鍵生成装置と、複数の公開鍵数列それぞれと平文との内積を求めて複数のナップザックを計算し、計算した複数のナップザックを非線形関数に対応して演算し、暗号文を生成する暗号化手段を含む暗号化装置と、法による乗数の乗法逆元と、法とを用いて、受信した暗号文を逆モジュラ変換し、複数の秘密鍵数列を用いて暗号文から平文を一意に復号する復号手段を含む復号装置を含む。

(もっと読む)

暗号化されたアクセスを使う電子的エンティティのセキュリティ化方法

【課題】DFAタイプの3つの攻撃に対して、単純で、効果的な撃退法を提供することである。

【解決手段】本発明のセキュリティ方法は、暗号化アルゴリズムの一部をなす巡回プロセスの選択されたステップの計算結果(リザルト)を記憶し、少なくとも前記巡回プロセスの少なくとも1部を再実施し、前記記憶したものに対応する新リザルトを再計算し、前記2つのリザルトを比較し、両者が異なる場合は、暗号文(MC)の送出を禁止することを特徴とする。

(もっと読む)

秘密鍵を伴う電子暗号アセンブリを安全に守る方法

【課題】秘密鍵または個人鍵をもつ暗号電子アセンブリまたはシステムの、すべてのnの値についての「n次のDPA」攻撃のリスクをなくす。

【解決手段】秘密鍵を使用してメモリ中に記憶される暗号計算プロシージャを実装する、プロセッサおよびメモリを含む電子システムのためのセキュリティ保護を行う方法であって、前記プロシージャについての少なくとも1つのクリティカル関数の入力または出力中の中間結果をマスキングすることから成る。

(もっと読む)

カスタマイズされたマスキングによって保護される低複雑度の電子回路

本発明の主題はマスキングにより保護された暗号化回路であり、前記回路は少なくとも1つの鍵krcを用いた2進ワードを暗号化する手段、前記ワードに線形処理(216)および非線形処理(226)を適用する手段、および前記ワードをマスキングする手段を含む。2進ワードは、マスクkriを用いることによって非線形処理の上流で脱マスキング(214)され、そしてマスクkr+1iを用いることによって前記処理の下流でマスキング(215)され、マスクkriおよびkr+1iは回路の各実例に固有の、一組のマスクから選択される。 (もっと読む)

暗号鍵取り出しを制限する通信システム、方法、及びデバイス

【課題】優れた、エンティティ間の暗号化通信方法を提供する。

【解決手段】外部エンティティとの暗号化通信のための方法、システム、及びデバイスであって、デバイスは暗号鍵を特定しようと試みるサイドチャネル攻撃を妨げるように構成される。デバイスは、第1のメモリ、第1のメモリに格納された暗号鍵、及び暗号鍵に適用するための片方向関数を有する。使用中、暗号鍵は、片方向関数への適用に先立ち第1のメモリから取り出され、デバイスは、暗号鍵が不揮発性メモリから取り出されることを許可される回数を予め定められたしきい値まで制限するように構成される。

(もっと読む)

暗号処理装置

【課題】HD2リークをなくし、DPA対策および検証をレジスタ並びにその出力信号に対してのみ行うことができ、電力解析に対する耐性を向上させることが可能な暗号処理装置を提供する。

【解決手段】演算用データを格納する第1レジスタ103と、演算用データを格納する第2レジスタ104と、非線形変換部としてSbox1073を有し、第2レジスタ104の格納値に対してラウンド演算を行うラウンド演算部107と、第1レジスタ103の格納値に対して逆置換を行い、逆置換した値をSbox1073に出力する逆置換部108と、を有し、Sbox1073は、Sboxテーブル値と逆置換された第1レジスタ103の値との排他的論理和演算した値を入力として非線形変換処理を行い、ラウンド演算部107は、ラウンド演算結果を第2レジスタ104に出力する。

(もっと読む)

暗号処理装置

【課題】電力解析攻撃に対する耐性を確保しつつ、処理時間を短くできる暗号処理装置を提供する。

【解決手段】暗号処理装置1は、それぞれが暗号処理を実行する第1及び第2のラウンド関数演算回路27a、27bと、第1のラウンド関数演算回路27aと前記第2のラウンド関数演算回路27bを並列に動作させる並列動作モード(PM)と、第1のラウンド関数演算回路27aと第2のラウンド関数演算回路27bを直列に動作させる直列動作モード(SM)とをランダムに切り替えて、第1のラウンド関数演算回路27aと第2のラウンド関数演算回路27bを動作させる制御回路30とを有する。

(もっと読む)

結託戦略の選択を含む確率論的結託防止符号のための復号方法

【課題】デジタル・コンテンツの不正コピーの作成および頒布に対する保護で、不正コピーのソースの特定を可能とする符号化方法を提供する。

【解決手段】確率論的結託防止符号の復号方法であって、マルチメディア・コンテンツの不正コピーの作成に使われた前記マルチメディア・コンテンツ中に存在する前記符号の少なくとも一つのシーケンスを識別することをねらいとし、結託戦略モデルの集合のうちから前記不正コピーを構築するために使われた結託戦略を選択するステップを含む。

(もっと読む)

表示情報変換装置

【課題】 画像表示装置を用いて情報を伝達する際の漏洩電磁波等を通じた情報の傍受を防止することを課題とする。

【解決手段】 画像変換装置が入力画像と数値列から複数の変換画像を生成し,生成された変換画像を画像記憶装置に格納し,画像出力装置により,画像記憶装置から変換画像を読出し,表示制御装置に順次送信する。表示制御装置は画像表示装置に受信画像を表示する。画像出力装置が高速に前記の変換画像群を出力することで,画像表示装置上で切替表示をおこない,視覚上で入力画像と同等の画像を表示する。

(もっと読む)

暗号処理装置

【課題】暗号化演算回路の消費電流を低く抑えることができ、電力解析に対する耐性を向上させることが可能な暗号処理装置を提供する。

【解決手段】所定ビットずつのフラグ演算を行う第1フラグ演算部102と、第1および第2データにフラグ演算によるフラグとのEXORによるフラグ制御を行う第1演算部103と、第2データレジスタのデータと第2フラグレジスタのフラグとのEXORを行う第2演算部109と、その出力データに対してラウンド演算を行うラウンド演算部110と、その出力と第1データレジスタの格納値および第1フラグレジスタのフラグとのEXORを行う第3および第4演算部111,112と、その出力データで所定ビットずつの新たなフラグ演算を行う第2フラグ演算部114と、その出力データに第2フラグ演算部によるフラグとのEXORによりフラグ制御を行う第5演算部115とを有する。

(もっと読む)

1 - 20 / 99

[ Back to top ]