Fターム[5J104NA22]の内容

暗号化、復号化装置及び秘密通信 (108,990) | 構成要素 (27,346) | 物理的構成要素 (16,068) | レジスタ (113)

Fターム[5J104NA22]の下位に属するFターム

シフトレジスタ (40)

Fターム[5J104NA22]に分類される特許

21 - 40 / 73

暗号処理装置

【課題】セキュリティ耐性を低下させること無く、暗号化演算回路の回路規模の増大および動作時の消費電流の増大を抑えることが可能な暗号処理装置を提供する。

【解決手段】複数の演算ブロックを含み、暗号演算を電源電圧レベルと基準電位レベル間でデータを遷移させ、演算によるデータの遷移を休止相と稼動相の2相で行う演算回路100と、電源電圧と基準電圧の中間の電圧を生成する電圧生成部200と、休止相では演算ブロック間の信号バスを上記電圧生成部に接続し、稼動相では信号バスを演算ブロックの出力に接続する出力制御部105,106,109,111,114とを有する。

(もっと読む)

情報処理装置

【課題】鍵実装システムについて、セキュリティレベルの高い開発環境を提供する。

【解決手段】セキュアメモリを備えたLSIを有するシステムについて、構成が共通のLSIを、<商品動作モード>とは異なる<開発モード>に設定して、プログラムの開発を行う。また、<アドミニストレータモード>に設定して鍵生成プログラムの開発および暗号化を行い、<鍵生成モード>に設定して、暗号化された鍵生成プログラムを実行させて各種の鍵を生成する。

(もっと読む)

プログラム可能なプロセッサにおける随意選択的なガロア域計算の実行

ガロア域乗算のための方法は第1及び第2の指令の実行を含んでいる。第1の指令は、第1の変数のような第1の入力を受信し、第2の変数のような第2の入力を受信し、第1及び第2の入力を使用してGF(2m)により多項式乗算を行い、積を生成することを含んでいる。第2の指令は、第1の指令からの積である第3の入力を受信し、積において演算するための予め定められた生成多項式である第4の入力を受信し、積における予め定められた生成多項式の演算を限定するため予め定められた生成多項式の長さである第5の入力を受信し、長さにより限定された予め定められた生成多項式を介して除数に関して積の係数を計算することを含んでいる。ハードワイヤブロックも説明されている。 (もっと読む)

拡張精度アキュムレータ

【課題】公開鍵暗号システムの使用が増加するにつれて、拡張精度モジュールの算術計算の性能を増大させる拡張精度アキュムレータを提供する。

【解決手段】乗算ユニットが拡張精度アキュムレータを含む。拡張アキュムレータの1つのポーションの内容を汎用レジスタに移動するためのインストラクション(「MFLHXU」)、及び汎用レジスタの内容を拡張アキュムレータの1つの部分に移動するためのインストラクション(「MTLHX」)を含む、マイクロプロセッサのインストラクションが、拡張精度アキュムレータの部分を操作するために提供される。

(もっと読む)

処理回路

【課題】 処理能力を維持したまま回路面積の削減化が図られた処理回路を提供する。

【解決手段】 128ビット幅のパラレル信号(平文)を入力し、分周器10からの低速のクロックCLK_Gに同期して128ビット幅全幅についてパラレルに処理を実行するレジスタ11,シフトロウズ演算器13,ミックスコラムズ演算器14,アドラウンドキー演算器15,レジスタ16と、128ビット幅をNに分割したときの128/Nビット幅単位で、クロックCLK_Gよりも高速のクロックCLK_Lに同期して処理を実行する共有型S―Boxを具備し、128ビット幅のパラレル信号を128/Nビット幅ずつに分けて上記共有型S―Boxに処理を複数回繰り返させるサブバイト演算器12とを備えた。

(もっと読む)

モントゴメリー乗算に基づくモジュラ乗算及び累乗の改善された装置と方法

【課題】モントゴメリー・モジュラ乗算を実行する、改良された小型電子論理演算装置を提供する。

【解決手段】ρ(A・B)Nのモントゴメリー・モジュラ乗算を実行するものであって、ここでρ(A・B)Nは A・B・I mod N にモジュラ演算上の合同であり、I・2n≡1 mod N であり、A、B及びNはnビット長オペランドであり、Nは奇数であり、該装置は、第一及び第二の主メモリ・レジスタであって、各レジスタはnビット長オペランドを保持し、それぞれ、乗数B、法Nを格納するように適合せしめられたものと、第一の値を第二の値によって、及び第三の値を第四の値によって、同時に乗算し、両方の結果を合計するデバイスであって、該デバイスへの入来ビットとしての予想Y0ビットを出力するための一つの桁上げ保存加算器を有するものと、該桁上げ保存加算器から出力される最下位kビットがゼロとなるようにY0を決定するY0センスユニットと、を具備する。

(もっと読む)

Pi++ストリーム暗号の暗号方法および復号方法、並びにパイ・データに基づく暗号算法及び復号化算法

【課題】「高速性」「安全性」「汎用性」の共存を実現させる効率に優れたストリーム暗号方法を提供する。

【解決手段】Pi++暗号シリーズの中心概念である動態S−box・動態フリップ・動態シフト・動態更新・動態循環シフトなど全て動態的な概念を一貫的に利用して、キーに基づいたキーストリームを生成し、該キーストリームと平文との排他的論理和演算により該平文を暗号化した暗号文を生成する。初期化プロセス、要素交換プロセス、インデックスポインターy生成プロセス、更新変数Mi×32生成プロセス、キーストリーム実行プロセス、インデックスポインターx選択プロセス、インデックスポインターy更新プロセス、インデックスポインターxの動態フリッププロセス、インデックスポインターyの動態フリッププロセス、MIX32更新プロセス、MIX32動態更新プロセス、臨時変数生成プロセスを有する。

(もっと読む)

情報処理装置

【課題】回路規模を増大させることなく暗号化及び認証値作成を実行できる情報処理装置を提供する。

【解決手段】入力パケットデータに対する暗号化処理及び認証値作成処理を行なうに際し、入力レジスタ部20に入力パケットデータを8byteずつ記憶する3個のレジスタ22,24,26を設け、レジスタ22,24に記憶されたデータについて第1のEXOR回路12及びAES回路14を用いた認証値作成処理を行った後に、レジスタ24,26に記憶されたデータについて第1のEXOR回路12及びAES回路14を用いた入力パケットデータの暗号化処理を行い、当該暗号化処理により暗号化された暗号化データをレジスタ24,26に記憶し、その後に入力レジスタ部20のデータを16byteシフトし、入力パケットデータの続きの16byteのデータをレジスタ24,26に記憶することを繰り返し実行するように制御する。

(もっと読む)

データ処理装置

【課題】本発明は、データを暗号化してハードディスク等に格納するプリンタ装置、複合装置等のデータ処理装置に関する。

【解決手段】複合装置1は、暗号化対象の画像データをハードディスク10のアクセス単位であるセクタをデータブロックとして該データブロック毎にレジスタ部9から初期ベクトルまたは前の該データブロックの暗号化された暗号データを利用してAES制御部8で暗号化してハードディスク10に保管する際に、画像データのフォーマット情報に基づいて、画像データのデータブロックのうちどのデータブロックを初期ベクトルを用いてAES制御部8に暗号化させるかの初期ベクトル利用タイミングを制御する。したがって、画像データがJPEG等で符号化されているか否かのフォーマット情報に基づいて初期ベクトル利用タイミングを制御することができ、データの機密を保持しつつ、処理効率を向上させることができる。

(もっと読む)

楕円曲線演算装置および楕円曲線演算方法

【課題】楕円曲線暗号における演算の高速化が可能な楕円曲線演算装置および楕円曲線演算方法を得ること。

【解決手段】楕円曲線上の点加算および点2倍算において、剰余算の演算結果を直後の乗算に使用しないように、点加算手順および点2倍算手順を構成する。例えば、ステップ2では、乗算手段による乗算(M ← T2×T3)と、剰余算手段による剰余算(T4 ← M mod p)とを、同時に実行している。そのため、点加算を高速に行うことができる。

(もっと読む)

暗号処理装置、および暗号処理方法、並びにコンピュータ・プログラム

【課題】ラウンド関数を繰り返し実行する暗号処理回路を簡略化して装置の小型化およびコストダウンを実現する。

【解決手段】秘密鍵Kに基づいて生成する複数の異なるデータ構成を有する第1中間鍵KAと第2中間鍵KBを適用して、複数のラウンド関数を繰り返し実行して入力データのデータ変換処理を行なう共通鍵ブロック暗号処理構成において、ラウンド関数実行部に第1中間鍵KAに基づいて生成するラウンド鍵KAiのみを入力してラウンド関数を実行し、第2中間鍵KBに基づいて生成される鍵KBiは、ラウンド関数部におけるF関数に入力することなく、暗号処理対象となる入力データ、またはラウンド関数からの出力データとの排他的論理和演算を実行させる構成とした。本構成により暗号処理回路を簡略化し装置の小型化およびコストダウンを実現した。

(もっと読む)

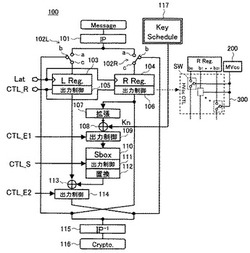

暗号/復号装置

【課題】回路規模を縮小できる暗号/復号装置を提供する。

【解決手段】暗号/復号演算回路100は、所定のデータを所定のビット長からなる暗号鍵を用いてAES方式に基づき暗号化演算する暗号演算回路、および前記暗号演算回路で暗号化演算された前記所定のデータを暗号鍵と同一のビット長からなる復号鍵を用いてAES方式に基づき復号化演算する復号演算回路の両方の回路機能を有している。鍵スケジュール演算回路200は、暗号鍵および復号鍵のいずれか一方から他方を生成する処理すなわち鍵スケジュール演算処理を行うためのものである。暗号/復号鍵用レジスタ300は、暗号鍵および復号鍵を交互に記憶する動作を行う。

(もっと読む)

半導体装置

【課題】第三者による不正な攻撃によって故障動作を引き起こされた場合でも、故障動作を検出し、回路動作を停止することが可能となるような半導体装置を提供する。

【解決手段】複数のフリップフロップを含む信号処理回路を有する半導体装置において、前記信号処理回路は、フリップフロップの入力信号を入力としパリティデータを生成する第1のパリティ生成回路と、前記第1のパリティ生成回路の出力をラッチするための、パリティ格納回路と、フリップフロップの出力信号を入力としパリティデータを生成する第2のパリティ生成回路と、前記パリティ格納回路の出力と第2のパリティ生成回路の出力とを比較し、不一致の場合に異常検出信号を出力するパリティ比較回路を備える。

(もっと読む)

疑似乱数生成装置及びそれを用いた暗号化処理装置

【課題】

従来は、高い安全性を実現するために大きな内部状態を持ち、ハードウェア実装では回路規模が、ソフトウェア実装ではメモリ容量が、大きくなった。

【解決手段】

本発明は、2ブロック(1ブロックはnビット)の容量のステート記憶部と複数ブロックの容量のバッファとを有し、これらの内容を攪拌し、乱数列を得る疑似乱数生成装置である。バッファの記憶内容を入力し、この入力データと同サイズのデータを出力する非線形変換部と、ステート記憶部の内容と非線形変換部の出力とを入力し、出力をステート記憶部に格納する第1の線形変換部、バッファの記憶内容とステート記憶部の記憶内容とを入力し、出力をバッファに格納する第2の線形変換部とにより攪拌する。攪拌したステート記憶部の内容を乱数列として出力する。

(もっと読む)

マイクロコントローラ

【課題】暗号化プログラムの秘匿性を十分確保できるようにしたマイクロコントローラを提供する。

【解決手段】暗号化したプログラムを格納するメモリ12と、第1の経路を通じて前記メモリから読み出した前記プログラムを実行するCPU11とを備える。暗号化プログラムを復号するために利用する復号情報を、前記第1の信号経路とは異なる第2の経路を通じて読み込み、且つ前記CPU11から物理的に読み出し不可能に保持するレジスタを有する復号ブロック13を備える。該復号ブロック13は、前記第1の経路を通じて前記メモリから読み出した前記暗号化プログラムを、前記レジスタに保持した前記復号情報を利用して復号する。

(もっと読む)

情報送信装置、情報送信方法、情報送信プログラムおよび該プログラムを記録した記録媒体

【課題】メモリの利用の効率化を図ること。

【解決手段】情報送信装置100は、送信先へ送信する送信データについて、パディングデータサイズ算出部201によって、暗号化アルゴリズムと、認証コードおよびコンテンツのデータサイズとに基づいて、パディングデータサイズを算出し、送信データサイズ算出部202によって、パディングデータサイズと、認証コードおよびコンテンツのデータサイズとから、送信データサイズを算出する。つぎに、生成部203によって、送信データの種別と送信データサイズとを含むヘッダを生成し、暗号化部204によって送信データを暗号化する。そして、送信部205によって、ヘッダと、送信データとを送信先へ送信する。

(もっと読む)

乱数発生器及び乱数発生器の作成方法

【課題】リングオシレータに配線資源による遅延回路を導入し、配線資源のジッターも利用して、真の乱数を発生する乱数発生器及び乱数発生器の作成方法を提供する。

【解決手段】複数の論理素子23で構成されるリングオシレータの当該論理素子23間のいずれか又は全てに少なくとも一個以上の配線資源(インターコネクト)22からなる遅延回路が設けられている複数のリングオシレータと、複数のリングオシレータの出力に接続され,複数のリングオシレータの排他的論理和出力を発生する排他的論理和回路18と、排他的論理和回路18の出力に接続され,所定のサンプリング周波数fSでジッター出力をサンプリング抽出するサンプリング回路12とを備える。

(もっと読む)

暗号処理方法及び暗号処理装置

【課題】暗号強度を損ねることなく暗号化/復号化の処理時間を短縮することのできる暗号処理方法および暗号処理装置を提供する。

【解決手段】暗号化処理が半分終了した時点で第1AES暗号演算部11から出力された暗号ベクタとKEYレジスタ31に保持された暗号鍵とIVレジスタ32に保持されたイニシャルベクタIVとを保持レジスタ33に保存しておき、次回以降の暗号化処理でKEYレジスタ31に保存された暗号鍵とIVレジスタ32に保存されたイニシャルベクタIVとが保持レジスタ33に保存されたものと一致する場合は、前半部を第1AES暗号演算部11側で暗号化し、これと並列に後半部を、保持レジスタ33に保持されている暗号ベクタを利用して第2AES暗号演算部21で暗号化する。

(もっと読む)

暗号演算装置

【課題】AES暗号回路を小型化する。

【解決手段】MixColumn変換回路において、4つの乗算器とXOR回路から構成される演算回路を2個並列に設けて、32ビットデータを2サイクルで処理するか、あるいは、単一の演算回路で32ビットデータを4サイクルで処理することで、MixColumn変換またはInvMixColumn変換の変換結果を得る。

(もっと読む)

プログラマブル論理回路

【課題】任意の機能セルを機密状態に保持しつつ、機密とされていない機能セルについて、部分的な再構成を可能とする。

【解決手段】一つ以上の構成レジスタに対応して一つ配置される機密保護レジスタと、機密保護レジスタの値が機密の状態であるならば構成レジスタの更新を禁止し、構成レジスタへの入力を出力し、機密保護レジスタの値が非機密の状態であるならば構成レジスタを更新し構成レジスタの値を出力するように動作する構成レジスタ制御回路をそなえることで、任意の機能セルを機密に保持しつつ、非機密部の部分的再構成を可能とする。

(もっと読む)

21 - 40 / 73

[ Back to top ]