Fターム[5J104NA39]の内容

暗号化、復号化装置及び秘密通信 (108,990) | 構成要素 (27,346) | 物理的構成要素 (16,068) | 計算モジュール (731)

Fターム[5J104NA39]の下位に属するFターム

計算能力を持つICカード (179)

Fターム[5J104NA39]に分類される特許

1 - 20 / 552

チェックデジット計算装置、チェックデジット計算方法、承認情報生成装置、承認情報生成方法、取引支援システム、取引支援方法、およびプログラム

半導体装置及びICカード

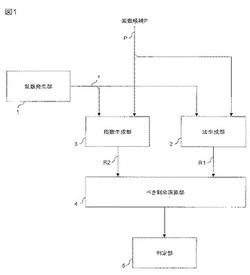

【課題】暗号に対するサイドチャネル攻撃から防御するために、素数性判定を行う半導体装置において、素数の漏えいを防止する。

【解決手段】素数性判定におけるべき剰余演算において、従来の指数のランダム化に加え、法をもランダム化する。乱数発生部により発生した乱数をランダム化数として、法生成部と指数生成部に入力する。法生成部と指数生成部は、ランダム化数を用いて素数候補Pをランダム化し、ランダム化された法R1と指数R2を生成する。ランダム化された法R1と指数R2を用いて素数性判定のためのべき剰余演算を実行し、その結果に基づいて、素数性候補Pの素数性を判定する。半導体装置の素数性判定中の消費電力が、判定対象の素数候補の値と無相関となり、サイドチャネル攻撃による素数の漏えいを防止することができる。

(もっと読む)

データ変換装置

【課題】データ変換装置において、マスク値の更新回数を減らしつつセキュリティ性を確保することにある。

【解決手段】S層変換(SubBytes)に係るマスク値M1,M2と、P層変換(ShiftRows及びMixColumns)に係るマスク値M3とを独立して更新することができる。例えば、マスク値M3は、マスク値M2とXORされたマスク値M4として使用される。このマスク値M3は、マスク値M1,M2より高い頻度で更新される。P層変換においては、S層変換に比して、同一のデータ(サブバイトS0〜S15)がより多く読み出されるものの、高頻度でマスク値M3が更新されることで、通信のセキュリティ性が確保される。また、マスク値M3のみを更新可能とすることで、マスク値M1,M2の更新回数を減らすことができ、その更新に要する消費電力を低減することができる。

(もっと読む)

ストレージメディア、ホスト装置、メモリ装置、及びシステム

【課題】秘密情報の不正利用の防止に有利な認証装置、被認証装置、およびその認証方法を提供する。

【解決手段】実施形態によれば、被認証装置を認証装置が認証する認証方法であって、前記被認証装置は、秘匿される固有の秘密識別情報(SecretID)、固有の暗号化秘密識別情報(E-SecretID)、および共通に付される鍵管理情報(FKB)を保持し、前記認証装置は、秘匿される識別鍵情報(IDKey)を保持し、前記認証装置が、前記被認証装置から、前記暗号化秘密識別情報(E-SecretID)および前記鍵管理情報(FKB)を読み出すステップと、前記認証装置が、読み出した前記鍵管理情報(FKB)を用いて、前記識別鍵情報(IDKey)から復号可能な識別鍵情報(FKey)を取得するステップと、前記認証装置が、得られた識別鍵情報(FKey)を用いて、読み出した前記暗号化秘密識別情報(E-SecretID)を復号し、秘密識別情報(SecretID)を取得するステップとを具備する。

(もっと読む)

ストリーム暗号の暗号化装置、ストリーム暗号の復号装置、ストリーム暗号の暗号化方法、ストリーム暗号の復号方法、およびプログラム

【課題】早送り、巻き戻し、途中再生が必要なコンテンツに、ストリーム暗号を利用すること。

【解決手段】ストリーム暗号の暗号化装置100であって、初期鍵および初期ベクトルを格納する内部メモリ110と、平文を所定のサイズのブロックに分割する分割部120と、分割部120で分割された各ブロックを識別する数値と、内部メモリ110に格納された初期ベクトルとに基づいて、各ブロック用の初期ベクトルを生成する生成部130と、各ブロック用に生成部130で生成された初期ベクトルと、内部メモリ110に格納された初期鍵とに基づいて、分割部120で分割された各ブロックを暗号化する暗号化部140と、暗号化部140で暗号化された各ブロックを連結して、暗号文を生成する連結部150と、を備える。

(もっと読む)

情報処理装置、サーバ、情報処理システム、および情報処理方法

【課題】ユーザの意思がより反映されたレコメンドを実現することが可能な、情報処理装置、サーバ、情報処理システム、および情報処理方法を提供する。

【解決手段】レコメンド情報を生成するサーバと通信を行う通信部と、レコメンド情報をサーバに生成させるための、複数のログデータと、サービスに対応付けてユーザを管理するための匿名情報と、サーバが使用可能なログデータの組合せを示す組合せ情報とを含む送信データを生成するデータ生成部と、生成された送信データを、サーバに送信する送信処理部とを備える、情報処理装置が提供される。

(もっと読む)

ハッシュ値生成装置、ハッシュ値生成プログラム及びハッシュ値生成方法

【課題】差分攻撃耐性を有し、メモリ容量に制限のある装置に実装可能なハッシュ生成方法を提供する。

【解決手段】メッセージをメッセージブロックに分割し、各メッセージブロックに対してブロック暗号の処理を実行してハッシュ値を算出するハッシュ値生成装置であって、初期値を格納する記憶部と、鍵定数Kを算出する関数fk、及び、出力データを算出する関数fRを実行し、出力データを記憶部に格納し、出力データを連結してハッシュ値を算出する演算部と、を備え、関数fRは、mビット幅のビット列の巡回シフトと、二つのビット列を加算する算術加算とを含み、4mビットの入力データに対して4mビットの出力データを算出する非線形関数γと、2mビット幅のビット列の巡回シフトと、二つのビット列の排他的論理和とを含み、4mビットの入力データに対して4mビットの出力データを算出する線形関数θと、の合成関数である関数FRを含む。

(もっと読む)

暗号処理装置

【課題】回路規模や消費電力の増大を抑えながら、サイドチャネル攻撃を無効化できる暗号処理装置を提供する。

【解決手段】第1線形変換部、第2線形変換部は、マスクデータを線形変換する。第1算出部は、処理対象データと第1線形変換部により線形変換された第1マスクデータとに基づいて第1データを算出する。選択部は、第1データと第2線形変換部により線形変換された第2マスクデータのいずれかを選択する。非線形変換部は、選択された第1データまたは第2マスクデータを非線形変換する。第2算出部は、非線形変換された第1データとマスクデータとに基づいて第2データを算出する。第3線形変換部は、第2データを線形変換する。そして、第3線形変換部により線形変換された第2データが新たな処理対象データとして保持され、非線形変換された第2マスクデータが新たなマスクデータとして保持される。

(もっと読む)

情報処理装置及び情報処理プログラム

【課題】処理対象データと処理プログラムを取得し、処理対象データに対して処理プログラムを実行する場合において、仮想計算機を利用し、当該処理の実行単位で処理対象データの暗号化処理と復号処理を制御できる情報処理装置を提供する。

【解決手段】情報処理装置の仮想計算機の鍵対生成手段は、秘密鍵Aと公開鍵Aを生成し、公開鍵出力手段は、公開鍵Aを出力し、処理対象データ取得手段は、公開鍵Aで暗号化された処理対象データを外部から取得し、復号手段は、処理対象データを秘密鍵Aで復号し、処理プログラム取得手段は、処理プログラムを外部から取得し、実行手段は、復号された処理対象データを対象に処理プログラムを実行し、公開鍵取得手段は、公開鍵Bを外部から取得し、暗号化手段は、処理プログラムの処理結果として生成された処理結果データを、公開鍵Bで暗号化し、出力手段は、暗号化された処理結果データを外部へ出力する。

(もっと読む)

情報処理装置およびその方法

【課題】 NAF Sウィンドウ法に必要な倍算テーブルの総数よりも少ない倍算テーブル数でスカラ倍演算を行う。

【解決手段】 変換部11は、スカラを入力し、スカラを符号付き二進法の、負数を含む数値に変換する。初期分割部12は、数値を1ビットから最大分割ビット長wの範囲の複数の数値に分割する。選択部13は、複数の数値から特定の数値を選択する。数列算出部14は、選択された数値の絶対値を含み、項の総数が前記最大分割ビット長wの関数である閾値よりも少ない数列を取得する。再分割部15は、複数の数値の絶対値のうち数列に含まれない数値を1ビットから前記最大分割ビット長wの範囲の複数の数値に再分割する。倍算テーブル算出部16は、数列に含まれる2以上の各項をスカラに含む倍算テーブルを算出する。スカラ倍演算部17は、分割された複数の数値、再分割された複数の数値、および、倍算テーブルを用いてスカラ倍演算を行う。

(もっと読む)

新暗号規格(AES)向けの柔軟なアーキテクチャおよび命令

【課題】汎用プロセッサ用の柔軟なAES命令セットを提供する。

【解決手段】AES命令セットは、AES暗号化または復号化用に「1ラウンド」パスを行う命令を含み、さらに、鍵生成を行う命令を含む。128/192/256ビット鍵用の鍵生成の鍵サイズおよびラウンド数を示すのに直近を利用してよい。柔軟なAES命令セットは、暗黙のレジスタをトラッキングする必要がないので、パイプライン能力の最大限の発揮が可能である。

(もっと読む)

演算装置

【課題】演算装置を小型化する。

【解決手段】演算措置は、データの種類ごとにN個の前記データを連続するアドレスに記憶する記憶装置と接続され、予め定められた暗号方式の演算を実行する。演算装置は、演算部と、アドレス生成部と、制御部とを備える。演算部は、暗号方式で用いられる複数の演算処理を実行する。アドレス生成部は、演算処理で用いられる種類のN個のデータのうち先頭のデータのアドレスの上位ビットと、指定に応じて更新されるカウンタ値に応じた値であって先頭のデータのアドレスを基準とするオフセットと、に基づいて、演算処理で用いられるデータを記憶する記憶装置のアドレスを生成する。制御部は、暗号方式で定められる順序で演算処理を実行するように演算部を制御するとともに、演算処理で用いられるデータの種類を変更するタイミング、および、演算処理で用いられるデータを変更するタイミングでカウンタ値の更新を指定する。

(もっと読む)

送信装置、受信装置および送受信システム

【課題】符号化処理と復号化処理との間の同期をより確実なものとして受信エラーを抑制することができる送受信システムを提供する。

【解決手段】送受信システム1Aは送信装置10Aおよび受信装置20Aを備える。送信装置10Aは、符号化部11、シリアライザ12および送信部13を備える。受信装置20Aは、復号化部21、デシリアライザ22、受信部23、エラー検出部24及びリセット指示部25を備える。符号化部11は、符号化部11の符号化処理と復号化部21の復号化処理との間の同期を確立するための同期信号(符号復号同期信号)を符号化データとして定期的に送信部13から受信装置20Aへ送信させる。符号化部11は、リセット指示信号を受信装置20Aのリセット指示部25から受け取ったときにも、符号復号同期信号を符号化データとして送信部13から受信装置20Aへ送信させる。

(もっと読む)

白色雑音生成装置

【課題】デジタル信号による白色雑音をより確実に連続的に生成できる白色雑音生成装置を提供する。

【解決手段】デジタル信号により白色雑音を生成する白色雑音生成装置において、正規乱数を生成するための所定の条件を満たす一様乱数を出力する乱数出力部1A/1Bが、複数系統設けられて成る乱数群出力部1と、乱数群出力部1によって逐次出力される複数系統の一様乱数に基づいて、Box-Muller変換により正規乱数を生成し、当該正規乱数に基づいて白色雑音を生成する白色雑音生成部3とを備えたものである。

(もっと読む)

情報処理装置,情報処理方法及びそのプログラム

【課題】暗号処理回路の耐タンパ性の評価をより効率的に行う。

【解決手段】暗号処理回路である評価用回路における入力ビットAの状態を表す状態変数と評価用回路における消費電力Wとが対応付けられた消費電力データを複数取得する。そして、取得された複数の消費電力データに基づいて、消費電力Wを目的変数とし消費電力Wに対応づけられた状態変数を説明変数として重回帰分析を行い、分析により決定係数R2及び偏回帰係数a1〜a8を分析値として導出する(ステップS240)。そして、導出された分析値に基づいて、評価用回路の耐タンパ性を評価する(ステップS251〜S256)。これにより、電力差分解析攻撃を複数回行い攻撃が成功するか否かによって耐タンパ性を評価する場合と比べて、暗号処理回路の耐タンパ性を効率的に評価することができる。

(もっと読む)

データ処理装置

【課題】外乱が発生しても正常な演算結果を出力する構成を実現する。

【解決手段】切替部10は、出力タイミングの度にデータKeyとデータDataとを並行して出力する。演算部20は、データKeyとデータDataとを用いた演算を行って、バスデータBus1とBus2とを並行して出力する。比較部30は、同タイミングで入力したバスデータBus1とBus2のデータ値を比較し、データ値が一致する場合は値が“H”の、一致しない場合は値が“L”の信号S1を出力する。切替部10は、出力されたバスデータBus1を入力し、出力タイミングの度に、入力した信号S1の値が“H”であれば、新たに入力したデータKIを新たなデータKeyとして演算部20に出力し、入力したバスデータBus1を新たなデータDataとして出力し、“L”であれば、演算部20に出力済のデータKeyとデータDataとを、再度、演算部20に出力する。

(もっと読む)

サイドチャネル攻撃に対抗する方法

【課題】

本発明は、サイドチャネル攻撃に対抗する方法に関する。当該方法は、中間変数をマスクするためのブロック暗号アルゴリズムを実行することから成り、このブロック暗号アルゴリズムは、1つ以上の非線形関数を有する。

【解決手段】

この課題は、前記1つ以上の非線形関数のうちの少なくとも1つの非線形関数が、マッチ・イン・プレース関数を使用して実行されることによって解決される。

(もっと読む)

半導体装置、および半導体装置の開発システム

【課題】本発明は、安価な製造コストで、複数の会社が開発した複数のプログラムを記憶素子に書込んだ状態であても、プログラムの内容が他社(許可されない者)に分からない半導体装置、および半導体装置の開発システムを提供する。

【解決手段】本発明に係る半導体装置10は、プログラムを記憶する記憶部(記憶素子2)と、記憶部に記憶したプログラムを実行することで特定の処理を行なう処理部(IP回路3)と、記憶したプログラムを記憶部から読出し、処理部で実行することが可能な命令を生成する演算部(CPU1)と、プログラムおよび命令を伝送するデータバス4とを備える。処理部は、データバス4を介して処理部に入力する命令に基づいて算術論理演算を行なう制御レジスタC_REGと、処理部に入力する命令を、制御レジスタで処理することが可能な命令に変換する変換回路(A回路32)とを有する。

(もっと読む)

情報処理装置、情報処理方法、及びプログラム

【課題】複数の演算ユニットを用いた並列処理において、より高速に素数を求める。

【解決手段】複数の演算ユニットのうち何れか1つを選択し、選択した演算ユニットに対してメモリに格納されているシードを用いた乱数発生処理の実行を指示する。複数の演算ユニットのそれぞれは、乱数発生処理の実行が指示されると、メモリに格納されているシードを用いて乱数を生成し、メモリに格納されているシードを生成した乱数で更新し、生成した乱数が素数であれば、該生成した乱数を出力する。乱数発生処理の実行を指示した演算ユニットによる更新処理が完了したことを検知すると、演算ユニットとは別の演算ユニット群のうち何れか1つを選択し、選択した演算ユニットに対してメモリに格納されているシードを用いた乱数発生処理の実行を指示する。

(もっと読む)

外部メディアインタフェース装置、テスト方法

【課題】正当性確認テストを行う際の時間を短縮する外部メディアインタフェース装置を提供すること。

【解決手段】記憶手段アクセス制御手段45と、外部メディアアクセス手段41、52と、暗号器43と、を有する外部メディアインタフェース装置100であって、前記暗号器のテストモードである場合、前記記憶手段アクセス制御手段と前記外部メディアアクセス手段との間にテスト用のパスを構築するパス構築手段53と、前記記憶手段アクセス制御手段が読み出したテストデータを取得してテストデータの送信先を振り分けるデータ振り分け手段44、60と、前記データ振り分け手段が振り分けた第一のデータを保持すると共に、前記データ振り分け手段が前記暗号器に振り分け、前記暗号器が暗号化した第二のデータを取得し、比較するデータ比較手段51と、を有する。

(もっと読む)

1 - 20 / 552

[ Back to top ]