Fターム[5J106CC42]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | フィルタ回路 (1,598) | ループフィルタ (906) | 複数のループフィルタ (25)

Fターム[5J106CC42]に分類される特許

1 - 20 / 25

PLLシンセサイザ

【課題】温度補償ループフィルタのキャパシタの容量値を小さくする。

【解決手段】PLLシンセサイザは,位相比較器PDと,ループフィルタLFと,電圧制御発振器VCOとを有する。さらに,温度補償ループとして,周波数制御電圧が制御電圧範囲から外れたときに比較信号30を出力する比較器CMPと,比較信号30を積分してMビットの第1のデジタル信号32を生成するデジタルフィルタDFと,第1のデジタル信号32を入力し,前記Mビットより少ないNビットで、前記第1のデジタル信号32に対応する第2のデジタル信号34を生成するΣΔ変調器12、10と,第2のデジタル信号34を電流信号36に変換する温度補償チャージポンプCPtと,前記電流信号36を温度補償制御電圧に変換する温度補償ループフィルタTFとを有し,電圧制御発振器VCOは温度補償制御電圧ftに基づいて出力クロックCKoutの周波数を制御する。

(もっと読む)

半導体集積回路

【課題】チップ面積の更なる縮小化を図ることができる半導体集積回路を提供する。

【解決手段】ディジタル制御発振器50−1〜50−nと、位相データ出力部100−1〜100−nと、積分処理部150と、フィルタ部151と、フィルタ部151からの時分割された出力信号に所定の係数を乗算した値を発振器制御値OTWとして出力する乗算器(第1の乗算器)40と、リファレンス周波数Frefに同期して、発振器制御値OTWを各ディジタル制御発振器50−1〜50−nに振り分ける出力セレクタ(制御値分離部)42と、を備える。

(もっと読む)

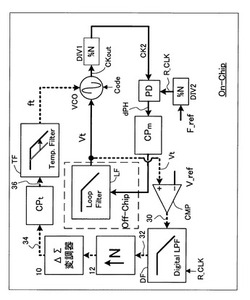

ループフィルタ部品を低減するために二重経路およびデュアルバラクタを用いるタイプII位相ロックループ

【課題】フィルタ内のオンチップ部品サイズを低減するデュアルチャージポンプおよび対応する二重信号経路を有し、低減されたループフィルタ部品を備えた位相ロックループ(PLL)の提供。

【解決手段】二重経路は、電圧制御発振器内のデュアルバラクタを介して有利に結合され、ループフィルタ部品をさらに低減する。PLLは、二重経路構成を加算するために通常用いられる回路によってもたらされるノイズの欠点をなくす。

(もっと読む)

PLL回路

【課題】高速かつ確実に低雑音特性を得ることができるPLL回路を得ることを目的とする。

【解決手段】相互に異なる移相量PS14,PS24,PS34がそれぞれ設定されており、N分周された発振信号の位相を設定されている移相量だけ変える移相器4−1〜4−3と、移相量の差分の関係が移相器4−1〜4−3のそれぞれに設定されている移相量の差分の関係と一致する条件の下で、相互に異なる移相量PS15,PS25,PS35がそれぞれ設定されており、R分周された基準信号Refの位相を設定されている移相量だけ変える移相器5−1〜5−3とを設ける。

(もっと読む)

PLL回路

【課題】ループフィルタの回路面積を削減すると共に、電圧制御発振器の動作の安定化やノイズ感度の低減が可能なPLL回路を提供することである。

【解決手段】本発明のPLL回路は、位相比較器3の出力信号に応じて出力電圧を制御する第1及び第2のチャージポンプ回路4、5と、第1のチャージポンプ回路4の出力に基づく信号から所定の周波数成分が除去された第1の電圧信号を出力する第1のフィルタ6と、第2のチャージポンプ回路5からの電流を入力し、所定の一定電圧を第2の電圧信号として出力する第2のフィルタ7と、第1のフィルタ6からの第1の電圧信号と基準電圧との比較結果に基づき第3の電圧信号を出力する電圧制御部30と、第1及び第2の電圧信号を低ゲイン入力、第3の電圧信号を高ゲイン入力とし、当該第1乃至第3の電圧信号に基づき発振周波数を生成する電圧制御発振器10を備える。

(もっと読む)

PLL回路

【課題】 PLL回路の出力周波数毎の閉ループ伝達特性を一定に保ち、所望の周波数を出力するのに必要な電圧制御発振器の制御電圧要求が大きい場合でも、電圧制御発振器を制御できるPLL回路を得る。

【解決手段】 PLL回路内にループフィルタ切替器6aを設け、ループフィルタ切替器6aは、その入力部に接続されたスイッチ8aと出力部に接続されたスイッチ8bとで、ループフィルタを選択的に切替え、各ループフィルタがオペアンプを用いた能動回路から構成される。

(もっと読む)

アナログ位相拘束ループ装置

【課題】単一で安定し信頼性のあるアナログのタイプIII位相拘束ループ装置を提供する。

【解決手段】位相検出器2は入力基準信号4及び出力信号6の位相差を表すエラー信号12を発生する。選択器14は第1帯域幅パラメータ値の選択時にエラー信号を第1信号経路8に供給し、第2帯域幅パラメータ値の選択時にエラー信号を第2信号経路10に供給する。第1信号経路はエラー信号を積分する第1積分器16と、その積分信号を積分してエラー電圧信号を発生する第2積分器18と、このエラー電圧信号に応答して第1信号経路出力信号を発生する電圧制御発振器20とを具えている。第2信号経路も同様な積分器22,24及び電圧制御発振器26を具えている。選択器28は第1帯域幅パラメータ値の選択時にVCO20の出力を選択し、第2帯域幅パラメータ値の選択時にVCO26の出力を選択する。選択器28の出力信号が位相検出器2に帰還する。

(もっと読む)

クロックデータリカバリー回路

【課題】周波数オフセットによるジッタ耐性の低下を防止するクロックデータリカバリー回路を提供する。

【解決手段】ディジタル制御発振器107における発振周波数の変化が矩形パルス状になるようにし、その周波数変化パルスの高さと幅を制御パラメータとしてディジタル制御回路104、105、106に与える。

(もっと読む)

CDR回路

【課題】異なる複数のビットレートの入力データを再生できるようにしたCDR回路を提供する。

【解決手段】参照クロックCKの周波数に対応した制御信号Vrにより第2の電圧制御発振器3の発振周波数が決定されるPLL回路と、制御信号Vrにより第2の電圧制御発振器3の発振周波数と同じ周波数で再生クロックCLK1を発振し且つ入力データのタイミングに合わせて該再生クロックCLK1の発振位相が調整される第1の電圧制御発振器1と、入力データを再生クロックCLK1によりリタイミングするフリップフロップ回路2とを備えるCDR回路において、PLL回路に、分周比の異なる2個の分周器7A,7Bと、該分周器7A,7Bの内の1つを選択するセレクタ8とを備えさせる。

(もっと読む)

信号発生装置

【課題】IC化が可能なように、VCOの出力の位相雑音のうち、中心周波数から所望の離調周波数における位相雑音を軽減化した信号発生装置を提供することである。

【解決手段】基準信号を出力する基準信号源1と、発振周波数を電圧制御可能な可変信号源3aを有し、可変信号源の出力信号を基準信号に位相同期させる複数のPLL手段31、32、・・3)と、各PLL手段の該各可変信号源の出力信号を合成する合成手段2と、各可変信号源の出力信号の位相が前記合成手段により合成後に同一となるように各可変信号源の出力信号の位相を調整する移相手段41、42、・・4Mとを備えた。

(もっと読む)

位相同期発振器及びその制御方法

【課題】VCO回路の特性バラツキや温度変動によらず、簡単な構成及び制御で常に高安定なVCO出力が得られることを課題とする。

【解決手段】位相比較器と、ローパスフィルタと、主制御を行う制御部と、該制御部出力の制御電圧で駆動されるVCO回路と、その出力を分周する可変分周器とからなるPLLループを備える位相同期発振器であって、制御部は、PLLループを複数周波数でロックさせて各ロック時の制御電圧を測定し、該測定した各制御電圧に基づき、VCO回路のリニアリティー校正された変調感度を求めると共に、該PLLループを所定周波数でロックさせた後、該PLLループを開放した状態で、前記求めた変調感度に基づきVCO回路に所定周波数を中心とするリニアリティー補正された周波数変化を発生させるための制御電圧信号を生成する。

(もっと読む)

PLL回路

【課題】 引込み時間の短縮化が図られたPLL回路を提供する。

【解決手段】 第1のクロックCLK1のN・Y倍の周波数の第2のクロックCLK2が入力されるリセット付分周器18が、断検出回路17で検出された入力クロックCLKINの停止を受けて分周をリセットし、再び入力クロックCLKINが入力されたことが断検出器17で検出されたことを受けて分周を開始して第3のクロックCLK3を生成して位相比較器12に入力する。

(もっと読む)

スイッチ可能なフェーズロックループ及びスイッチ可能なフェーズロックループの動作方法

【課題】PLL及びPLLの動作方法に関し、制御可能なオシレータが出力信号を発生し且つPLLの入力クロック信号として使用するために第一クロック信号及び第二クロック信号の間でスイッチオーバーさせる。

【解決手段】現在使用されているクロック信号(CKin1又はCKin2)が出力信号を発生するために、このクロック信号と出力信号との間の位相差が決定され且つオシレータの制御のために使用され、一方現在使用されていないクロック信号(CKin2又はCKin1)が出力信号を発生するために、出力信号に関してのその周波数差が決定され且つ格納され且つ継続的にアップデートされ且つ、前に使用されていないこのクロック信号へのスイッチオーバーの後にオシレータの制御のために提供される。PLL出力信号はどのようなスイッチオーバーに関連する周波数変化よりも迅速に追従することが可能である。

(もっと読む)

VCO駆動回路及び周波数シンセサイザ

【課題】 VCOの制御端子からみたインピーダンスを低くして、VCOの位相雑音特性の劣化を防ぐことができるVCO駆動回路及び周波数シンセサイザを提供する。

【解決手段】 粗調用周波数のデジタルデータを入力し、アナログ信号を出力する粗調用DAC4と、微調用周波数のデジタルデータを入力し、アナログ信号を出力する微調用DAC6と、粗調用DAC4からの出力のノイズを除去してVCOの制御端子への入力とする応答速度の遅いLPF5と、微調用DAC6からの出力を電圧に変換し、信号の平滑化を行う応答速度の速いLPF7と、LPF5の入力段とLPF7の入力段とを接続する抵抗R6 と、LPF5の出力にLPF7の出力が加算されるよう容量結合するコンデンサC8 とを有するVCO駆動回路及びそれを備えた周波数シンセサイザである。

(もっと読む)

VCO駆動回路及び周波数シンセサイザ

【課題】 VCOの制御端子側のインピーダンスを低くし、VCOの位相雑音特性の劣化を防ぎ、VCOの固体バラツキや温度変化に対して固有周波数を一定値に保つVCO駆動回路及び周波数シンセサイザを提供する。

【解決手段】 粗調用周波数のデジタルデータをアナログ出力する粗調用DAC4と、微調用周波数のデジタルデータをアナログ出力する微調用DAC6と、粗調用DAC4からの出力のノイズを除去してVCOの制御端子への入力とする応答速度の遅いLPF5と、微調用DAC6からの出力を電圧に変換し、信号の平滑化を行う応答速度の速いLPF7と、LPF5の入力段とLPF7の入力段とを抵抗R6 で接続し、LPF5の出力とLPF7の出力とをコンデンサC8 で容量結合し、LPF7に電圧制御手段としての可変抵抗R4 を設けたVCO駆動回路及びそれを備えた周波数シンセサイザである。

(もっと読む)

情報記録再生装置、およびその記録クロック生成方法

【課題】ウォブル信号に同期して生成される記録クロックの周波数安定化を簡素な構成で実現することができる情報記録再生装置を提供する。

【解決手段】本発明に係る情報記録再生装置は、光ディスクに記録クロックを用いてデータを記録する情報記録再生装置において、光ディスクの再生信号から抽出されるウォブル信号によるフェーズロック制御に基づいて周波数制御され、記録クロックの発振源となるVCOと、VCOの周波数変動量を検出する周波数変動検出部と、を備え、VCOは、フェーズロック制御に基づく周波数制御に加えて、周波数変動検出部にて検出される周波数変動量に基づいて周波数制御される、ことを特徴とする。

(もっと読む)

耐放射線型位相ロック・ループ

【課題】耐放射線型位相ロック・ループ(PLL)を実現するための方法および装置を提供する。

【解決手段】耐放射線型PLLは、調節可能な帯域幅のループ・フィルタを含む。調節可能なフィルタは、未濾波の電圧制御信号を変更し、検出された放射線誘導型の過渡イベント中に、安定した電圧制御信号を電圧制御発振器(VCO)へ送る。調節可能なフィルタは、放射イベントが検出されたときに、その帯域幅を減少することによって、放射の作用を除去する。

(もっと読む)

マルチループ電圧制御発振器を創出するための方法及び装置

【課題】 高いデータレートで周波数変調を行い、位相ノイズを低く抑えたVCOを提供すること。

【解決手段】 本発明は、実質的に広帯域の電圧制御発振器(VCO)から発生すると予想される位相ノイズ(ジッタ)を引き起こさずに、非常に高い変調レートを提供可能とした理想的なVCOを創出するための方法および装置に関する。一般的な高性能なVCOは変調帯域が狭くなる代償として純度の高い信号を提供するが、本発明の方法により、高性能(低ジッタ)且つ高い変調帯域を有する理想的なVCOを創出することが可能となる。高周波数位相変調器及び制御電圧プロセッシングは、制御電圧の周波数コンポーネントを分割する段階と、位相調整器へ向かう高周波数制御電圧コンポーネントを電気的に積分する段階とを備える。これにより理想的なVCOのための全体的な電圧‐周波数間の伝達関数を創出する。

(もっと読む)

2重系クロック位相同期装置および通信装置

【課題】 歪みのないクロックを出力できる2重化クロック位相同期装置、およびこれを用いた通信装置を提供することである。

【解決手段】 無線基地局10は、外部から受信した信号から抽出されたクロックに位相同期した基準クロックを生成するクロック位相同期部12a,12bを備えた通信装置である。クロック位相同期部12a,12bは、位相ロックループ回路を2重化したものであり、待機系は運用系よりも速い応答速度で動作する。こうした構成によって、運用系と待機系との間の位相差が少なくなり、系の切替が起こったとしても、出力クロックに歪みが生じることがなくなる。

(もっと読む)

改良VCO事前チューニングを有するPLL合成装置

本発明は、位相ロックループ(PLL)合成装置(1)に関する。PLL合成装置(1)は、位相検出器(2)、少なくとも1つのスイッチ可能なフィルター(3)、制御電圧(uPLL)で制御可能な発振器(4)及びプログラム可能な分周器(5)を有する。VCO(4)は2個の入力を有し、制御電圧(uPLL)及び選択電圧(uSET)は、第1及び第2の入力へ、それぞれ周波数粗調整のために印加され、そしてVCO(4)周波数を決定する。

(もっと読む)

(もっと読む)

1 - 20 / 25

[ Back to top ]