Fターム[5J106DD09]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | スイッチ (729) | セレクタ (399)

Fターム[5J106DD09]の下位に属するFターム

マルチプレクサ (64)

Fターム[5J106DD09]に分類される特許

321 - 335 / 335

遅延ロックループ回路

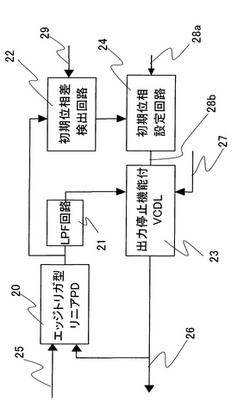

【課題】基準クロック信号/クロック信号間の位相を合致させるように位相制御の遅延ロックループ(DLL)回路で、回路規模縮小化、低消費電力化を図かった、電圧制御可変遅延線(VCDL)を使用するアナログDLL回路を提供

【解決手段】イニシャル信号入力により第1のクロック信号の初期位相設定を行う遅延ロックループ回路で、基準クロック信号位相と第1のクロック信号位相の比較結果に応じた信号を出力の位相比較器と、イニシャル信号入力時に位相比較器出力信号に応じた選択信号を発生の初期位相差検出器と、イニシャル信号入力時に初期位相差検出器からの選択信号で位相が異なる第2のクロック信号中の基準クロック信号に最近接位相の第2のクロックを選択し、第3のクロック信号として出力の初期位相差設定回路と、第3のクロック信号に位相比較器からの信号に応じた位相遅延を付加の第1のクロック信号を出力の電圧制御可変遅延線とを備える遅延ロックループ回路を提供。

(もっと読む)

位相同期ループ回路

【課題】 ディジタル信号伝送においてキャリア引き込み特性の改善を図り、それを実現する位相同期ループ回路の構成を提供すること。

【解決手段】 位相同期ループ回路が複素乗算器71、位相比較器73、ループフィルタ74、数値制御発振器75等を備え、位相比較器73において、複素数信号の実数部及び虚数部から逆タンジェント特性を得て位相を算出する検出位相算出部76と、位相が異なる2つの直交ディジタル位相変調の信号点配置パターンにおける近傍引き込み点の位相と、上記で算出した受信信号の検出位相とのそれぞれの位相誤差を求める位相誤差計算部77とを備え、各ブロックにおけるパターン毎の位相誤差の2乗から尤度を求めて尤度の高い位相誤差の積分値を位相誤差として出力する。

(もっと読む)

PLL回路

【課題】 複数の発振帯域を有するVCO、又は異なる発信帯域を有する複数のVCOを備えたPLL回路において、設定した発振周波数に最適なVCOを選択完了するまでに要する時間を短縮すること。

【解決手段】 PLL回路の各出力周波数に対応する最適なVCOを予め記憶回路11に記憶しておき、このデータを利用してPLL回路の出力周波数が変化した時に最初に選択するVCOを決定する。また、各出力周波数に対応する最適なVCOは、当該出力周波数の選択完了後に書き換えることができるようにする。また、当該出力周波数に対応するVCOデータの代替として、前後の出力周波数のデータを利用する。また、コンパレータの出力を利用してVCOの制御電圧の動きを観測することにより、選択しているVCOの可否を判断するまでの時間を短縮する。

(もっと読む)

PLLシンセサイザ

【課題】 信号純度を低下させることなく、誤差信号の極性を反転させる際のロック外れを起こさないようにする。

【解決手段】 VCO11の自走発振周波数をローカル信号Bの周波数より高い第1の周波数領域内にするために必要な第1のオフセット電圧V1と、ローカル信号Bの周波数より低い第2の周波数領域内にするために必要な第2のオフセット電圧V2のうち、周波数領域を切り替える際に、その切り替える方の周波数領域に対応したオフセット電圧を選択してVCO11に一時的に印加する。

(もっと読む)

PLL回路およびDLL回路

【課題】 ロックするまでの時間を短縮することができ、初期制御電圧を、回路の用途に応じて変更することができ、製造条件等により、ロックするまでの時間が変動することを防ぐことのできるPLL回路およびDLL回路を提供する。また、ジッタを迅速に低減することのできるDLL回路を提供する。

【解決手段】 PLL回路は、位相比較器3と、チャージポンプ4と、ループフィルタ5と、電圧制御発振器6と、選択信号に応じて制御電圧のレベルを選択する電圧設定回路10と、複数個の選択信号のうち少なくとも1つを出力し、電圧制御発振器6において周波数の増減された出力クロックの、入力クロックに対する逓倍数を検出し、複数個の選択信号の中から最適な選択信号を特定し、電圧設定回路10に出力する設定値判定回路9とを含み、各回路は、待機信号に応じて処理の開始および停止を行なう。

(もっと読む)

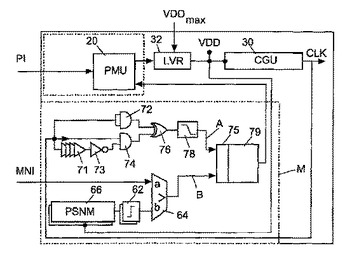

性能調整のための閉ループ制御

本発明は、監視される性能指標に応答して集積回路の性能を制御するための、方法および回路構成に関し、集積回路の電力供給は、前記性能指標に基づいて制御される。制御された電力供給の雑音レベルと前記集積回路内で発生されたクロック周波数の少なくとも一方が監視され、チェック結果が所定の範囲内にない場合、それぞれの制御信号が制御機能にフィードバックされる。それによって、プロセス変動への簡単で容易に拡張可能な自動適応が達成されることができる。  (もっと読む)

(もっと読む)

クロック同期回路におけるクロック捕捉

クロック捕捉同期回路は、まず基準クロック信号から同期クロック信号を生成し、そして同期クロック信号を捕捉し、基準クロック信号が除かれた後も同期クロック信号を出力し続ける。クロック捕捉同期回路はまた、同期クロック信号の入力依存ジッタを低減する。本発明により、基準クロック信号が除かれた後、同期クロック信号を出力し続けるクロック同期回路が提供される。また、本発明により、同期クロック出力信号の入力依存ジッタをもし除去しないとしても低減はするクロック同期回路が提供される。  (もっと読む)

(もっと読む)

電圧制御発振器およびPLL回路

【課題】 電圧制御発振器の発振周波数範囲を広くし、かつ制御電圧のみにより発振周波数を調整する。

【解決手段】 電圧比較回路は、制御電圧が第1参照電圧より低いときに第1電圧比較信号を活性化させ、制御電圧が第2参照電圧より高いときに第2電圧比較信号を活性化させる。カウンタは、カウントクロックに同期して、第1比較結果信号の活性化中にカウンタ値を減少させ、第2比較結果信号の活性化中にカウンタ値を増加させる。発振回路は、複数の発振周波数帯域のいずれかをカウンタ値に応じて選択するとともに、選択した発振周波数帯域において制御電圧に応じて発振周波数を調整して出力クロックを出力する。これにより、動作条件の変動あるいは制御電圧の設定範囲の縮小に対して広い発振周波数範囲を確保でき、かつ電圧制御発振器の発振周波数を制御電圧のみにより調整できる。

(もっと読む)

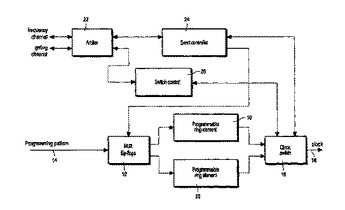

プログラマブルで一時停止可能なクロック発生ユニット

互いに排他的に動作するように配置構成された2つのプログラマブル・リング発振器(10、20)と、プログラマブル可変遅延要素(図示せず)とを含むクロック発生回路。入力プログラミング・パターン(14)が発振回路に入力として供給され、プログラミング・パターン(14)は、クロック信号を発生させる必要のある周波数のシーケンスを表すデータを提供する。2つの発振器(10、20)の出力端がクロック・スイッチ(16)に接続され、発生されたクロック信号(18)がこのスイッチから出力される。周波数変更を求める要求が受け取られたときは、まず現在アイドル状態の発振器(20)が必要とされる次の周波数で活性化され、次いで現在動作中の発振器(10)の出力が、そのクロック信号がローのときに、ゲート制御されるようになる。次に、前にゲート制御されていた発振器(20)の出力が、その出力がローのときに、ゲート制御されないようにされ、次いで発振器(10)が非活性化される。  (もっと読む)

(もっと読む)

クロックリカバリ回路及び通信デバイス

本発明に係るクロックリカバリ回路は、第1遅延量でデータ信号を順次遅延させる複数段の第1可変遅延素子と、第1遅延量より大きい第2遅延量で、クロック信号を順次遅延させる複数段の第2可変遅延素子と、複数段の第1可変遅延素子によって遅延された複数のデータ信号を、同一段の第2可変遅延素子によって遅延されたクロック信号によりサンプリングする複数のタイミングコンパレータと、連続する2つのタイミングコンパレータの2つのサンプリング結果を排他的論理和演算する複数のEOR回路と、複数のEOR回路の演算結果に基づいて、クロック信号を遅延させるリカバリ可変遅延回路とを有する。 (もっと読む)

半導体装置

本発明の半導体装置は、瞬時にクロックを切り替えるのではなく、前基準信号の位相状態と現基準信号の位相状態が一致するようにディレイセルを1段ずつ移動させて、最大N+1/Nクロック(Nは2以上の整数)かけて切り替えて、正確に基準信号にクロックを同期させ、出力されるクロックのDUTYを一定に保つようにした。 このような本発明の半導体装置によれば、基準信号がクロックに同期していない様な信号が入

力され、この基準信号の立ち上がりに対してリセットをかけた場合に、クロックのDUTYが不連続になるのを防ぐことができる。

(もっと読む)

半導体装置及び電圧制御発振回路

電圧制御発振回路(15)内に互いに異なる段数の独立した複数のリング発振回路を設け、セレクタ(22)により何れか1つのリング発振回路の出力を帰還クロック信号(FB)として選択的に出力することで、独立しているリング発振回路の出力が常に帰還クロック信号として出力されるようにして、動作速度が高速であってもデューティ比が崩れていない帰還クロック信号を出力でき、入力信号(DLLI)が出力されるまでの遅延時間を任意に調整できるようにする。  (もっと読む)

(もっと読む)

位相スイッチングデュアルモジュラスプリスケーラ

デュアルモジュラス分周器を有する位相スイッチングデュアルモジュラスプリスケーラがもたらされる。前記分周器は第一及び第二の2分周回路(A;B)を有しており、前記第二の2分周回路(B)は、前記第一の2分周回路(A)の出力部に結合され、少なくとも前記第二の2分周回路(B)は各々90度で分離される四つの位相出力を有している。位相選択ユニット (PSU)が、第二の2分周回路(B)の四つの位相出力(Ip, In, Qp, Qn; INi, INni, INq, INnq)の一つを選択するためにもたらされる。更に、位相制御ユニットが、制御信号(C0, NC0; C1, NC1; C2, NC2)を位相選択ユニットに供給するためにもたらされ、位相選択ユニットPSUは、制御信号(C0, NC0; C1, NC1; C2, NC2)による四つの位相出力(Ip, In, Qp, Qn; INi, INni, INq, INnq)の選択を実行する。直接論理に基づく位相制御ユニット(PSU)の実現により、より高い速度が可能になり、チップ上の面積が節減される。  (もっと読む)

(もっと読む)

PLL回路

【課題】 出力信号のS/Nが高く、最大ロックアップ時間が短くかつ低廉なPLL回路を提供する。

【解決手段】 出力信号のS/Nが高くするために水晶電圧制御発振器1を用いる。また、M相位相シフト回路4が基準信号SREFを略同一周波数のM相の信号を生成し、セレクタ5が該M相の信号の中から基準信号SREFとの位相差が最小になる信号を選択して比較信号SCOMとして出力する。これにより、比較信号SCOMと基準信号SREFとの位相差が小さくなるので、最大ロックアップ時間を短縮できる。また、水晶電圧制御発振器を一つしか用いないので、コストを抑えることができる。

(もっと読む)

位相周波数検出器およびそれが組み込まれた位相ロックループ回路

【課題】 位相誤差信号に周波数差を加味した変形を加えることにより、周波数が離れているときでも短時間で位相同期を達成する。

【解決手段】 周波数が離れているときに生じる位相誤差信号の不連続なジャンプをジャンプ検出部30において検出し、検出信号により状態記憶部32の状態を遷移させる。保持部34において、状態記憶部32の状態に応じて位相誤差信号を修正して周波数位相誤差信号とする。

(もっと読む)

321 - 335 / 335

[ Back to top ]