Fターム[5J106DD09]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | スイッチ (729) | セレクタ (399)

Fターム[5J106DD09]の下位に属するFターム

マルチプレクサ (64)

Fターム[5J106DD09]に分類される特許

121 - 140 / 335

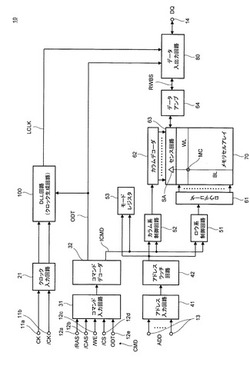

半導体装置

【課題】リード動作時における位相調整精度を低下させることなく、DLL回路の消費電力を低減する。

【解決手段】ODT機能を有するデータ入出力回路80と、データ入出力回路80の動作タイミングを規定する内部クロックLCLKを生成するDLL回路100とを備える。DLL回路100は、内部クロックLCLKを高精度に位相制御する第1のモードと、低消費電力で動作する第2のモードとを有し、データ入出力回路80がODT動作を行っていない場合には第1のモードで動作し、データ入出力回路80がODT動作を行っている場合には第2のモードで動作する。このように、ODT動作の有無によってDLL回路100の動作モードを切り替えていることから、厳密な位相制御が不要なODT動作時における消費電力を低減することが可能となる。

(もっと読む)

デジタルPLL回路

【課題】

映像信号をサンプリングするためのサンプリングクロック信号として用いても、映像に乱れを生じさせないクロック信号を生成することのできるデジタルPLL回路を提供することを課題とする。

【解決手段】

映像信号のサンプリングに用いるサンプリングクロック信号として、入力電圧に応じた発振周波数のクロック信号を出力する電圧制御発振回路と、映像信号の制御に用いられる複合同期信号と、前記電圧制御発振回路の出力に基づく帰還信号との位相差を検出する位相差検出部と、前記位相差検出部で検出される位相差が所定の範囲内にある場合は当該位相差を選択して出力し、前記位相差検出部で検出される位相差が前記所定の範囲内にない場合は前記位相差検出部で検出される位相差の目標値を出力する出力部とを含み、前記出力部の出力に基づいて、前記電圧制御発振回路の入力電圧を制御する。

(もっと読む)

PLL装置及びその制御方法

【課題】 基準入力期間に対して基準信号断期間が長期間継続しても、基準信号に同期して安定した信号を出力することが可能な、制御が容易で安価なPLL技術を提供する。

【解決手段】 基準発信源から入力される基準信号に対して所定の位相差を有する出力信号を生成するPLL装置は、前記基準信号と前記出力信号との位相を比較して、当該位相の位相差に対応する位相差信号を出力する比較手段と、基準となる位相差に対応する基準位相差信号を保持する保持手段と、前記位相差信号、又は、前記基準位相差信号を制御信号として選択する選択手段と、前記選択手段が選択した制御信号に応じた周波数の前記出力信号を発振して出力する発振手段と、を備え、前記選択手段は、前記基準発信源から前記基準信号が入力されている期間は前記位相差信号を選択し、前記基準発信源から前記基準信号が入力されていない期間は前記基準位相差信号を選択する。

(もっと読む)

クロック位相調整回路

【課題】実装面積や消費電力を低減させることができるクロック位相調整回路を提供すること。

【解決手段】n個の第1の遅延素子15を多段に接続し、入力クロック信号INCLKをその周期の1/nずつ遅延させたクロック信号をそれぞれ出力するDLL回路2と、n個の第1の遅延素子15から出力されるクロック信号のうち1つのクロック信号を選択して出力する第1のセレクタ回路3と、この第1のセレクタ回路3から出力されるクロック信号CLK1を遅延させる遅延部4を備えている。遅延部4は、1又は複数の直列に接続された遅延回路20を有しており、この遅延回路20は、前段の遅延回路10に設けられた第1の遅延素子15の遅延量に対して1/2の遅延量を有する第2の遅延素子21と、入力されたクロック信号CLK1と第2の遅延素子21により遅延されたクロック信号のいずれかを選択して出力する第2のセレクタ回路22とを備える。

(もっと読む)

基準周波数発生装置及び基準周波数発生システム

【課題】冗長化された基準周波数発生システムにおいて、現用側と予備側での出力切替時に出力信号のタイミングが急激に変動するのを防止する。

【解決手段】現用側の基準周波数発生装置51においては、自機のGPS受信機21aが生成する1PPS信号がPLL回路22aに供給される。予備側の基準周波数発生装置52においては、現用側の基準周波数発生装置51のPLL回路22aから出力された1Hzの信号が、第1伝送経路を経由してPLL回路22bに供給される。予備側に入力された1Hzの信号は、前記第1伝送経路と遅延量が等しい第2伝送経路を経由して現用側に戻される。現用側の基準周波数発生装置51は、自機のPLL回路22aからの1Hzの信号と、予備側に出力して戻された1Hzの信号と、の時間差に基づき補正用信号を出力する。予備側の基準周波数発生装置52は、補正用信号に基づいて、PLL回路22bの出力信号の位相を調整する。

(もっと読む)

基準周波数発生器

【課題】リファレンス信号を取得できている状態において動作環境が通常のものから一時的に外れた場合でも、自走用制御信号を精度良く得ることができる基準周波数発生器を提供する。

【解決手段】基準周波数発生器は、電圧制御発振器と、位相比較器と、温度センサと、制御部と、を備える。制御部は、GPS受信機からの1PPS信号が供給されなくなると、ループフィルタから出力される制御電圧信号に代えて、自走用制御電圧信号を生成して電圧制御発振器を制御する。制御部は、電圧制御発振器が動作している経過時間に応じて、前記自走用制御電圧信号を決定する。また、この制御部は、1PPS信号を取得できているときに時系列で記憶された制御電圧信号から、温度センサの検出値が設定温度範囲から外れたときの制御電圧信号を除外した上で、残りの制御電圧信号の変化に基づいて前記自走用制御電圧信号を決定することができる。

(もっと読む)

PLL回路及び発振装置

【課題】クロック信号を安定的に生成するPLL回路及び発振装置を提供すること。

【解決手段】水晶発振回路1は、同水晶発振回路1に設けた駆動可変部の駆動能力をPLL回路50aのループフィルタ59から出力される制御信号Slfの電圧値に応じて制御する。

(もっと読む)

基準信号発生装置

【課題】演算処理能力の低い安価なCPUを用いても、ホールドオーバー時における位相差を抑制して、保守作業の時間的制限等の自走発振に係わる課題を解決することができる基準信号発生装置を実現する。

【解決手段】制御部10は、1PPSが入力されている間に同期型制御電圧信号のレベルを経時的に観測し、記憶する。制御部10は、リファレンス信号の入力断を検出すると、自走用第1制御電圧信号を生成し、電圧制御発振器14へ与える。また該自走用第1制御電圧信号を用いて前記電圧制御発振器を制御している期間において、自走用第2制御電圧信号の算出を開始する。そして前自走用第2制御電圧信号の記算出が完了し次第、自走用制御電圧補正値を算出し、位相差を相殺しながら制御を続ける。以後、H.O.が終了するまで、自走用第N制御電圧信号の算出を繰り返し、高精度な基準周波数信号を発生させる。

(もっと読む)

リングオシレータ及びそれを用いたPLL回路

【課題】 リングオシレータで発生した高調波ノイズによる干渉を抑制できるリングオシレータ及びそのリングオシレータを備えたPLL回路を提供する。

【解決手段】 リングオシレータは、無線装置に内蔵され、複数段のインバータゲートからなる発振回路と、発振回路に接続された切り替えスイッチとを備える。発振回路が発生する高調波ノイズと無線装置の受信周波数とが干渉し、通信感度が低下する場合には、切り替えスイッチによりインバータゲートのリング状に接続される段数を切り替える。リングオシレータが発生する高調波ノイズの周波数を変えることで、無線装置の受信周波数との干渉を抑制する。

(もっと読む)

ルビジウム原子発振器

【課題】スイープ時間を短時間にする。

【解決手段】マイクロ波MWに基づき共鳴信号RSを発生する原子共鳴器1と、原子共鳴器1が発生する共鳴信号RSを増幅する増幅器2と、位相変調信号LWを出力する低周波発振器10と、共鳴信号RSと位相変調信号LWとに基づき制御電圧VCを出力する周波数制御部4と、制御電圧VCによって発振信号OUTの周波数が制御される電圧制御発振器8と、発振信号OUTを位相変調信号LWに基づき逓倍及び位相変調してマイクロ波MWを出力する逓倍位相変調部9と、記憶部27と、共鳴信号RSの周波数がロックされたロック状態の時に制御電圧VCを所定の時間間隔TSで記憶部27に同期電圧SVとして記憶させ、共鳴信号RSの周波数がロックされていない非ロック状態の時に制御電圧VCと同期電圧SVとに基づき周波数制御部4に制御信号S2を出力する制御部26と、を含むルビジウム原子発振器100。

(もっと読む)

位相同期回路及びこれを用いた受信機

【課題】フラクショナルスプリアスの発生しない位相同期回路を提供する。

【解決手段】第1の分数及び第2の分数の和で表される比率を基準信号の周波数に乗じて得られる対象信号に周波数及び位相が一致した出力信号を得る位相同期回路において、第1の分数の分母と第2の分数の分母と2との最小公倍数を更に2で除した数と同じ段数の増幅器を環状接続して構成され、最小公倍数と同じ信号数の多相信号が取り出し可能であって多相信号の周波数がデジタル制御信号及びアナログ制御信号によって制御され、多相信号の1つが出力信号として出力される制御発振器120と、出力信号と基準信号との間の周波数差及び位相差をデジタル信号に変換する変換部116と、デジタル信号に基づいて、基準信号の周期毎に、次の周期において基準信号と位相が一致する信号を多相信号から順次選択する信号選択部140とを具備する。

(もっと読む)

発振システム(oscillatorysystem)の周期タイミング・ジッタ(periodictimingjitter)の減少

【解決手段】PLL及びVCOを含む発振システムのようなノイズに敏感なアナログ回路について適応切替周波数回路を含む電圧調整器を含む装置が開示される。例において、装置は参照クロック発振器30、低ジッタ発振器170a、低ジッタ発振器について電源電圧WD_REGを調整するためにクロック信号入力を含む電源120、低ジッタ発振器出力周波数が安定している場合クロック検出器制御信号BOOST_CLK_SELを生成するクロック検出器、クロック検出器制御信号がアサートされた場合、低ジッタ発振器出力信号の周期ジッタの影響を抑制するために、電源へのクロック信号CLK入力として、参照クロック発振器出力信号REF_CLK、及び低ジッタ発振器出力信号VCO_CLKのうち一つを選択するマルチプレクサ110を含む。他の例において、クロック検出器制御信号は低ジッタ発振器出力周波数が安定している場合、電源のクロック信号入力として低ジッタ発振器出力信号を選択するために、マルチプレクサを制御する。 (もっと読む)

半導体装置

【課題】クロックの周波数が低くても、多大な時間を要することなく所望の位相遅延を可能にする半導体装置を提供する。

【解決手段】リファレンスクロックと第1のディレイラインで遅延させたリファレンスクロックとの位相比較結果に応じて第1のディレイラインでの遅延量を制御し、制御結果に基づいて第1のクロックを第2のディレイラインで遅延させ所定の位相差を有する制御クロックを生成する半導体装置にて、第1のディレイラインでの遅延量が設定可能な最大遅延量に応じた遅延量以上かつ最大遅延量未満の所定の閾値遅延量を超える場合には、セレクタによりリファレンスクロックとして出力するクロックを第1のクロックから定数倍の周波数を有する第2のクロックに切り替えるようにして、第1のクロックの周波数が低くても、多大な時間を要することなく所定の位相差を有する制御クロックを生成できるようにする。

(もっと読む)

位相誤差検出装置、位相誤差検出方法、集積回路及び光ディスク装置

【課題】周波数誤差が生じているときでも±180度を越える位相誤差の検出を可能とし、PLLの安定性を向上させることができる位相誤差検出装置を提供する。

【解決手段】アナログ入力信号をサンプリングクロックに基づいてAD変換してデジタル再生信号を生成するAD変換部1の出力より位相誤差を検出する位相誤差検出装置は、AD変換部1の出力より前記位相誤差を生成する位相誤差生成部2と、位相誤差を補正する位相誤差補正部3とを含み、位相誤差補正部3は、過去の位相誤差により位相誤差検出範囲を決定し、位相誤差生成部2が生成した位相誤差が位相誤差検出範囲外であった場合に当該位相誤差を補正する。

(もっと読む)

信号生成回路

【課題】 プロセス要因で生じるクロック信号の位相バラツキを抑える。

【解決手段】 信号生成回路100は、クロック信号PLLCKが通るクロック信号線30に1以上のクロックバッファ31が配置され、1以上のクロックバッファ31によりクロック信号PLLCKを遅延させ、遅延したクロック信号に基づき所定の信号を生成する。この信号生成回路100は、前記クロックバッファ31と同一チップ上に形成された複数のクロックバッファ41を有して構成される参照用クロックバッファ40と、参照用クロックバッファ40の遅延量を検知し、この遅延量と予め定められた遅延量との差に基づく位相調整信号PHADJを出力する遅延検知回路50と、位相調整信号PHADJに応じて、クロック信号PLLCKの位相を変える位相調整回路20と、を備える。

(もっと読む)

デジタル位相ロック・ループ(DPLL)、デジタル位相ロック・ループ(DPLL)内のジッタを制御するための方法、デジタル制御発振器(DCO)内のディザを最適化するための方法、および自己ディザリング・デジタル制御発振器(DCO)回路

【課題】 デジタル位相ロック・ループ(DPLL)および方法を提供する。

【解決手段】 デジタル位相ロック・ループ(DPLL)および方法は、入力として基準クロックを受け取り、ディザリングした基準クロック信号を出力するように構成された調整可能遅延線を含む。位相周波数検出器(PFD)は、ディザリングした基準クロック信号をフィードバック・クロック信号と比較して、ディザリングした基準クロック信号とフィードバック・クロック信号との位相および周波数の差を決定するように構成される。デジタル制御発振器(DCO)は、PFDから早遅判断を受け取り、それに応じて出力を調整するように構成され、ディザリングした基準クロック信号はDPLLの全体的な動作を強化するためにジッタ応答を分散する。

(もっと読む)

位相混合回路及びそれを備える遅延固定ループ回路

【課題】PVTが変動してもジッタの増加を防止する位相混合回路及びそれを備えた遅延固定ループ回路を提供する。

【解決手段】位相制御信号に応答して第1入力信号及び第2入力信号の位相を混合し、単位位相値の自然数倍分だけの位相が可変される位相混合信号を出力する位相混合部と、PVT変動情報を含むPVTコード信号に応答して前記単位位相値を調整する位相値調整部とを備える。

(もっと読む)

クロックデータリカバリ回路

【課題】簡単な回路で高データレートおよび低データレートに対応させる。

【解決手段】クロック信号CLK0、CLK1のエッジに係るタイミングt1、t2、t3(ただし、t2<t1<t3)でサンプリングした入力データ信号DATAINの論理値をそれぞれD1、D2、D3とする時、D1≠D2であるか、D1≠D3であるかを検出する検出回路11と、検出回路11の検出結果に基づいて、入力データ信号DATAINの論理値の遷移タイミングがタイミングt2、t3に一致するようにクロック信号CLK0、CLK1の位相を変化させるクロック発生回路14と、を備える。

(もっと読む)

クロック生成回路、及び集積回路

【課題】電源電圧、温度変動、製造プロセスによる素子特性の変動があっても、外部クロックの周期に応じて位相関係が一定になる複数のクロックを出力する。

【解決手段】クロック生成回路は、外部クロックに対して、第1の遅延素子101により遅延させた第1のクロックを出力する第1の生成部130及び第2の遅延素子102により遅延させた第2のクロックを出力する第2の生成部140と、第1の遅延素子及び第2の遅延素子の遅延量に対して、それぞれ相関がある遅延量を有する複数の第3の遅延素子127を用いて、複数の第3の遅延素子127の遅延量の合計が外部クロックの周期に依存した目標値になるように、第3の遅延素子を制御し、制御用の信号を用いて、第1の遅延素子101の遅延量、第2の遅延素子102の遅延量、及び第3の遅延素子127の遅延量を制御する制御部120とを備える。

(もっと読む)

基準信号発生装置

【課題】常に高精度な制御電圧信号のレベル(DAC値)の推定を行うことができる基準信号発生装置を実現する。

【解決手段】制御部10は、起動とともに計時を開始し(S102)、計時を行いながら(S103)、自走DAC値の算出タイミングを検出して自走DAC値の算出タイミングになると(S104:Yes)、予め設定したタイミング(起動からの経過時間)と重み付け係数との関連テーブルから、重み付け係数Wを設定する(S105)。この際、重み付け係数は、起動からの経過時間が長いほど大きな値に設定される。これにより、DAC値の変動が激しい起動からの経過時間が短い期間では、過去のDAC値が今回の推定値に与える影響が少なくなる重み付けがなされる。一方、経過時間が十分に長いDAC値が安定する期間では、過去のDAC値が今回の推定値に与える影響が大きくなる重み付けがなされる。

(もっと読む)

121 - 140 / 335

[ Back to top ]