Fターム[5J106DD09]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | スイッチ (729) | セレクタ (399)

Fターム[5J106DD09]の下位に属するFターム

マルチプレクサ (64)

Fターム[5J106DD09]に分類される特許

81 - 100 / 335

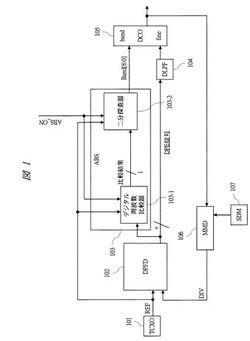

ADPLL回路、半導体装置及び携帯情報機器

【課題】ADPLL環境下またはADPLL環境に近い環境下において、ABSの精度向上手段を提供し、ABSの処理時間短縮を実現する。

【解決手段】ABS103中のデジタル周波数比較器103−1に、DPFD102の出力するDPE信号の初期位相差を格納するDFFを用意する。ABS動作開始直後に、DPFD102が出力するDPE信号はDPFD102の内部回路の初期位相差を表すものであるとしてDFFに記録する。以後デジタル周波数比較器103−1は入力されるDPE信号からDFFに記録された初期位相誤差を引いたものでABSを行い、高速かつ安定したABS動作の実現を図る。

(もっと読む)

同期装置および同期方法

【課題】同期源からの信号を捕捉できない状態になっても、可能な限り同期を維持することができる同期装置および同期方法を提供する。

【解決手段】選択部20は、内蔵GPSユニット2からの第1の基準信号およびGPSユニット3からの第2の基準信号のいずれかを選択する。PLL回路6は、選択部20で選択された基準信号に同期した同期信号を生成して内部の回路へ供給する。、内蔵GPSユニット2のホールドオーバー時間は、GPSユニット3のホールドオーバー時間よりも短い。選択部20は、GPSユニット3がホールドオーバー可能な状態となった後は、GPSユニット3を選択する。

(もっと読む)

クロックデータリカバリ回路

【課題】ジッタに高速に追従可能なCDR回路を提供する。

【解決手段】フリップフロップFF1〜FF4はそれぞれ、入力データDINを対応するクロック信号CKのタイミングでラッチする。i(iは自然数)番目の第1論理ゲートG1iは、(2×i−1)番目のフリップフロップFFの出力と(2×i)番目のフリップフロップFFの出力とが不一致のときアサートされる内部アップ信号UPを生成する。j(jは自然数)番目の第2論理ゲートG2jは、(2×j)番目のフリップフロップFFの出力と(2×j+1)番目のフリップフロップFFの出力とが不一致のときアサートされる内部ダウン信号dnを生成する。第3論理ゲートG3は、複数の内部アップ信号up1〜up2にもとづきアップ信号UP_Aを生成する。第4論理ゲートG4は、複数の内部ダウン信号dn1、dn2にもとづきダウン信号DN_Aを生成する。

(もっと読む)

信号多重化回路

【課題】データ信号とクロック信号との位相関係を適応的に制御できる信号多重化回路を提供する。

【解決手段】信号多重化回路は、第1のクロック信号の第1の位相位置に同期したデータ遷移をする第1のデータ信号と第1のクロック信号の第1の位相位置から180度位相がずれた第2の位相位置に同期したデータ遷移をする第2のデータ信号とを受け取り、第2のクロック信号に応じて第1及び第2のデータ信号を順次選択して出力するセレクタ回路と、第1及び第2のデータ信号と第1及び第2のクロック信号とに基づいて、第2のクロック信号とデータ遷移との位相関係を示す位相制御信号を出力する位相検出器と、位相制御信号に応じて位相関係を制御する位相制御器とを含む

(もっと読む)

半導体集積回路装置

【課題】ノーマルなクロックとSSCとを生成するクロック発生回路における回路面積を低減しながら、高精度のSSCを生成する。

【解決手段】電圧制御発振器から出力されたクロック信号vco1は、分周器13によって分周され、分周クロックph0としてセレクタ15に出力される。分周器13は、制御回路12の制御信号Pconに基づいて、周期の1/mずつ位相のシフトした分周クロックph1〜phmを出力する。セレクタ15は、分周クロックph0〜phmのうち、最も近い位相シフトをもつ2つの分周クロックphj,phj+1を選択する。位相補間回路16は、制御回路12から出力される重み付けデータ信号Aに基づいて、分周クロックphj,phj+1間の位相差の間を更に細分化した位相シフト量で位相シフトさせ、出力クロックfout1として出力する。

(もっと読む)

周波数シンセサイザ

【課題】設計が容易で、かつノイズ特性を良好にする。

【解決手段】周波数foutの出力信号Soutを生成するVCO5、周波数f1の低周波信号S1を生成する低周波信号生成部3、周波数f2の高周波信号S2を生成する高周波信号生成部4、ミキサ部6、ミキシング信号Smix中の差周波数信号Sdiを通過させる低域フィルタ部7、比較用信号S4を出力する信号処理部10、位相比較部8およびループフィルタ9を備え、信号処理部10は、周波数f2が新たに設定された際に、fout<f2のときには比較用信号S4の出力を停止し、fout≧f2で、かつ差周波数信号Sdiの絶対周波数fdiが低域フィルタ部7のカットオフ周波数fco以上のときには周波数f3(>f1)の基準信号S3を比較用信号S4として出力し、fout≧f2で、かつfdi<fcoのときには差周波数信号Sdiを比較用信号S4として出力する。

(もっと読む)

バーストデータ再生装置

【課題】バーストデータからクロックを抽出してデータの再生を行うバーストデータ再生装置を得ること。

【解決手段】入力バーストデータ、ICLK、θCLKを入力し、入力バーストデータとICLKとの間の比較結果を出力する周波数位相比較部1と、入力バーストデータとICLKとの比較結果に基づいて準同期状態または非準同期状態を示す検出信号を出力する準同期状態検出部2と、比較結果を平滑化するループフィルタ部3と、準同期状態の場合は非準同期状態の場合よりも小さな利得でループフィルタ部3の出力信号を増幅する線形利得可変増幅部4と、線形利得可変増幅部4の出力信号に基づいてICLKおよびθCLKを生成する多位相型電圧制御発振部5と、入力バーストデータを遅延させる遅延調整部6と、遅延調整後の入力バーストデータとICLKに基づいてデータを再生する識別部7と、を備える。

(もっと読む)

チャージポンプ回路、PLL回路及び電子回路装置

【課題】寄生容量(浮遊容量)の影響を抑制し、制御信号の電圧変動を抑えることで、リファレンスリークや妨害スプリアスを少なくすることが可能なチャージポンプ回路を提供する。

【解決手段】本実施形態のチャージポンプ回路は、セレクタ手段SEL1は、主定電流源I1_mainと主定電流源I2_mainまたは副電流源I2_subとを接続させ、かつ、主定電流源I2_mainと主定電流源I1_mainまたは副電流源I1_subとを接続させるよう接続状態を選択し、主定電流源I1_main及びI2_mainを常時他の電流源と接続させる。

(もっと読む)

位相同期ループ回路および位相同期ループ回路の制御方法

【課題】チップサイズの増大を抑え、広帯域の発振周波数帯域を有することが可能なPLL回路等を提供すること。

【解決手段】VCO34は、制御電圧VTに応じた発振周波数fVCOを有する出力クロック信号CLKOを生成する。PLLブロック2は、制御電圧VTを生成する。ロック検出器24は、発振周波数fVCOが設定周波数fSにロックされているか否かを検出する。VT電圧検出部31は、バラクタVA1ないしVA3のうちの何れを選択するかを決定する。セレクタ部32は、出力クロック信号CLKOの粗調整段階においてはバラクタVA0を選択する。また、粗調整段階においてロック検出された旨をロック検出器24から受信することに応じて、微調整段階へ移行する。微調整段階においては、移行時点におけるVT電圧検出部31によって選択されていたバラクタの選択を維持する。

(もっと読む)

半導体集積回路

【課題】広い周波数範囲で高調波電流成分を削減して高周波ノイズを低減することのできる半導体集積回路の提供を図る。

【解決手段】クロック信号CKに同期して動作する複数のデジタル回路11,12を含む半導体集積回路であって、前記各デジタル回路は、周波数が同じで位相が異なる第1および第2クロック信号CKa,CKbの一方を受け取り、前記第1および第2クロック信号の位相差は、m,nを自然数として、ほぼ[2m−1]/2nであるように構成する。

(もっと読む)

デジタル位相同期回路

【課題】ホールドオーバ期間中の温度特性と経年変化に対する影響を抑え、周波数の高安定性を維持するホールドオーバ機能を有するデジタル位相同期回路を得る。

【解決手段】電圧制御型クロック発振手段の周辺の温度を測定する温度測定手段と、同期対象と同期している間、デジタルフィルタ手段からの出力で電圧制御型クロック発振手段を制御するとともにデジタルフィルタ手段からの出力と電圧制御型クロック発振手段の周辺の温度、経過時問の履歴から経過時間と電圧制御型クロック発振手段の周辺の温度と項に持つ2元多項式を求め、同期対象と同期していない間、同期対象に同期しなくなってからの経過時間および電圧制御型クロック発振手段の周辺の温度から2元多項式で電圧制御型クロック発振手段を制御する制御信号を推定するとともに推定した制御信号で電圧制御型クロック発振手段を制御するホールドオーバ手段と、を有する。

(もっと読む)

クロックリカバリ回路およびデータ再生回路

【課題】クロックジッタを低減可能なクロックリカバリ回路およびデータ再生回路を提供する。

【解決手段】シリアル入力信号を第1のクロック信号に同期させてサンプリングしたサンプリングデータを出力するサンプラ13、サンプリングデータに基づき、第1のクロック信号とシリアル入力信号のクロックとの位相関係を表すシリアル位相情報信号を出力する位相比較回路14、シリルア位相情報信号を第2のクロック信号に同期させてシリアルパラレル変換したパラレル位相情報信号を出力するシリアルパラレル変換回路17、パラレル位相情報信号に基づき、位相偏差信号と位相遅進信号を演算するデジタルフィルタ回路16、位相偏差信号と位相遅進信号とに基づいて生成した位相制御信号を第2のクロック信号より高速の第3のクロック信号に同期して出力する位相制御量処理回路20および、位相制御信号に基づき、外部から入力する基準クロック信号の位相を調整した第1のクロック信号を出力する位相補間回路12を備える。

(もっと読む)

半導体集積回路およびその動作方法

【課題】比較的小さな電源電圧による速度変動を高精度で抑制して比較的大きな電源電圧による速度変動を高速で抑制する。

【解決手段】半導体集積回路は、第1と第2の機能ブロックMOD00、01、クロック生成回路PLL、クロック供給回路CS0を具備する。第1と第2の機能ブロックMOD00、01には、電圧値の相違する第1と第2の電源電圧VDD00、1が供給される。MOD00は一方の電源電圧VDD01が供給可能な第1の内部回路BUF00と第1の論理回路MFF00を含み、MOD01は他方の電源電圧VDD00が供給可能な第2の内部回路BUF01と第2の論理回路MFF01を含む。クロック供給回路CS0は微調遅延段回路FC0と粗調遅延段回路CC0と位相差計測回路RSM0を含み、RSM0は第1と第2の動作クロック信号COUT00、01の位相差に応答してFC0の遅延時間TF0とCC0の遅延時間TC0を制御する。

(もっと読む)

クロック信号制御回路及びクロック信号制御方法

【課題】クロック信号の周波数制御をより好適に行うこと。

【解決手段】モニタ回路12のリングオシレータ16によるモニタ結果であるモニタ信号MSの周波数に応じて設定値記憶回路13からテーブル値TVALを出力させる。そして、そのテーブル値TVALに応じてクロック信号生成回路14のPLL回路15a,15bにより生成した発振信号と等しい周波数のクロック信号CLKを対象回路11に供給する。

(もっと読む)

遅延ロックループ回路、半導体集積回路装置

【課題】低い周波数から高い周波数までの幅広い周波数帯域に対応して、回路面積の小さい遅延ロックループ回路、その遅延ロックループ回路を搭載する半導体集積回路装置を提供する。

【解決手段】遅延ロックループ回路は、位相変更回路と、遅延線回路と、遅延制御回路とを具備する。位相変更回路は、入力される基準クロックに対して第1の位相差を有する第1の信号と、第2の位相差を有する第2の信号とを出力する。第1の位相差と第2の位相差との差分は所定の位相遅延量を示す。遅延線回路は、変更可能な単位遅延量を備える遅延回路を複数含む。遅延制御回路は、単位遅延量の合計が基準位相遅延量になるように単位遅延量を制御する。

(もっと読む)

遅延ロックループ回路、信号遅延方法

【課題】回路面積を大きくすることなく、遅延ロックループ回路を提供すること

【解決手段】逓倍PLL107は、基準クロックを逓倍して出力する。DLL211は、逓倍PLL107から出力されたクロックと、逓倍PLL107から出力されたクロックを遅延させたクロックと、を比較し、比較結果に基づいて所定の遅延量を持つ遅延信号を生成する。遅延制御信号演算回路108は、DLL211が生成した遅延信号に基づき、所望の遅延制御信号を生成する。第1の遅延回路102は、遅延制御信号演算回路108が生成した遅延制御信号に基づいて、入力信号を遅延させる。

(もっと読む)

受信部及び局側装置並びにクロック・データ再生回路における周波数校正方法

【課題】電圧制御型発振器を用いた受信部等において、温度補償用に容量素子を増やすことなく、温度変化による電圧制御型発振器の周波数特性を補償する。

【解決手段】本発明の受信部/局側装置は、受信信号からクロック信号及びデータ信号を再生するクロック・データ再生回路11を含むものであって、クロック・データ再生回路11に含まれる電圧制御型発振器17の発振周波数を校正する校正器16と、信号受信のスケジュールを管理する機能を有し、クロック信号及びデータ信号を再生すべき受信信号(上り信号)が無い状態の持続時間が校正器16による校正の所要時間を満たす時を選んで校正器16に対してリセット信号(校正指令信号)を出力する管理部104とを備えたものである。

(もっと読む)

スペクトラム拡散クロックジェネレータ、回路装置、画像読取装置、画像形成装置、及びスペクトラム拡散クロック生成方法

【課題】周波数変調幅を高精度に合わせることができるようにする。

【解決手段】入力クロックとフィードバッククロックとの位相差を検出する位相比較器2と、位相比較器2からの位相差信号に応じて電流を供給するチャージポンプ3と、チャージポンプ3の出力を電圧に変換し、平滑化するループフィルタ4と、入力電圧に応じた周波数のクロックを発生させる電圧制御発振器6と、変調幅設定値に応じた振幅を持つ変調信号を生成する変調生成部8とを有し、ループフィルタ4の出力と変調生成部8から出力される変調信号とを加算した信号を電圧制御発振器6に印加し、スペクトラム拡散クロックを生成する際、電圧制御発振器6で生成されたスペクトル拡散クロックの変調幅を検出し、検出した変調幅と変調幅目標値を比較し、その差分を小さくするように新たに算出した変調幅設定値を変調生成部8にフィードバックする変調幅検出部10を備えた。

(もっと読む)

発振周波数制御回路

【課題】 自己の周波数を補正し、自走した時にも発振周波数を安定に保ち、更に外部からの固定電圧を可変にした制御電圧で発振できる発振周波数制御回路を提供する。

【解決手段】 電圧制御発振器15と、分周器16と、位相比較器12と、ループフィルタ14と、検波回路17と、PWM回路22と、メモリ21と、制御電圧可変回路26と、位相比較器12とループフィルタ14との接続をオン/オフすると共に制御電圧可変回路26からの制御電圧を選択出力する選択スイッチ13と、当該制御電圧選択の指示で当該制御電圧を優先的に選択出力し、当該指示がない場合に検波回路17で検出された外部基準信号のレベルが適正範囲内であれば選択スイッチ13をオンとし、レベルが適正範囲外であれば選択スイッチ13をオフとしてメモリ21に記憶されたパルス生成の情報をPWM回路22に出力するCPU20とを有する。

(もっと読む)

タイミング・モジュールのホールドオーバのための内蔵自己検査のシステム及び方法

【課題】本発明の実施例は、局所発振器を有する装置において使用される方法を含む。

【解決手段】方法は、外部レファレンス信号によって統制される局所発振器について外部レファレンス信号にロックされている間に、外部レファレンス信号の関数であり、発振器におけるドリフトを統制するために使用される関数である補正信号に少なくとも部分的に基づいて数学的モデル毎の予測補正信号を求めるよう発振器の少なくとも2つの数学的モデルを訓練する工程を含む。方法は更に、外部レファレンス信号が利用可能でなく、発振器におけるドリフトを統制するために別の補正信号を使用する場合に最小の時間誤差を少なくとも2つの数学的モデルのうちの数学的モデルも含む。方法は、訓練に使用される期間に加えた検査持続時間の必要なしに、選択された数学的モデルを使用することが可能であるように、補正信号のサンプリングされたバージョンを使用して、選択された数学的モデルを検査する工程を更に含む。

(もっと読む)

81 - 100 / 335

[ Back to top ]