Fターム[5J106DD09]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | スイッチ (729) | セレクタ (399)

Fターム[5J106DD09]の下位に属するFターム

マルチプレクサ (64)

Fターム[5J106DD09]に分類される特許

21 - 40 / 335

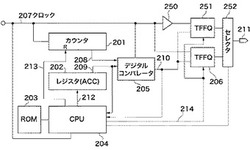

PWM信号生成装置

【課題】PWM信号生成装置において、回路規模を小さくして効果的に放射雑音等のノイズを低減する。

【解決手段】CPU204、カウンタ201、レジスタ202、及びコンパレータ205は基準クロックの周波数をその一周期未満の時間で変動させた変動クロックを生成する。TFF206は基準クロックに応じて変動クロックを第1のPWM信号として出力する。TFF251は基準クロックを所定の時間遅延させた遅延クロックに応じて変動クロックを第2のPWM信号として出力する。セレクタ252は第1及び第2のPWM信号を選択的にPWM信号として出力する。

(もっと読む)

発振器

【課題】PLL回路を有する発振器であって、小型化を図ることができる発振器を提供する。

【解決手段】発振器100は、基板110の上方に配置された第1MEMS振動子12を含み第1発振信号を出力する基準発振回路と、基板110の上方に配置された第2MEMS振動子52を含み制御信号で発振周波数が制御され第2発振信号を出力する電圧制御発振回路と、前記第2発振信号を分周して分周信号を出力する分周回路と、前記分周信号と前記第1発振信号との位相差に基づいた前記制御信号を出力する位相比較回路と、を含み、第1MEMS振動子12および第2MEMS振動子52の各々は、第1電極と、第2電極と、を有し、第2電極は、第1電極と対向配置された可動部を有し、基板の平面視において第1MEMS振動子12の可動部の面積は、第2MEMS振動子52の可動部の面積よりも大きい。

(もっと読む)

可変分周装置

【課題】クロック信号が高速化した場合でも対応することのできる可変分周装置を得る。

【解決手段】可変分周回路101は、クロック信号Clk_aを入力し、クロック信号Clk_aに対するP(Pは2以上の整数)またはP+1の分周した信号Do1を出力する。可変分周回路102は、クロック信号Clk_aと逆相になるクロック信号Clk_bを入力し、クロック信号Clk_bに対するPまたはP+1の分周した信号Do2を出力する。経路切り替え回路103は、信号Do1,Do2を入力し、経路選択信号MuxContにより信号Do1,Do2のうちいずれか一方を選択し出力する。

(もっと読む)

PLL回路

【課題】サイクルスリップが発生することでPLL回路の引き込み時間が遅れるという問題がある。そのため、サイクルスリップを低減し、高速にロックを行なうPLL回路の提供が望まれる。

【解決手段】図1に示すPLL回路は、位相比較器と、位相比較器と接続されるチャージポンプと、を備えている。さらに、位相比較器は、基準クロックを遅延させたクロック及びフィードバッククロックを遅延させたクロックに基づき、チャージポンプの出力電圧を上昇させる第1のUP信号及びチャージポンプの出力電圧を下降させる第1のDW信号を生成する制御信号生成回路と、基準クロックに同期させ、第1のUP信号に基づきチャージポンプの出力電圧を上昇させる第2のUP信号を出力する第1の保持回路と、フィードバッククロックに同期させ、第1のDW信号に基づきチャージポンプの出力電圧を下降させる第2のDW信号を出力する第2の保持回路と、を含んでいる。

(もっと読む)

信号生成装置及び周波数シンセサイザ

【課題】PLLを用いた周波数シンセサイザにおいて、簡素な構成でありかつスプリアス特性が良好であること。

【解決手段】位相比較部に入力する参照周波数信号を、ディジタル信号からなる鋸波のゼロクロスポイントを検出したときのクロックに基づいて生成する。しかしこの場合ディジタル値が飛び飛びの値であることから正負の符号が逆転するときにディジタル値がゼロとなるとは限らない。そこで前記ディジタル値が徐々に変化する領域において正、負の符号が逆転するゼロクロス時の直前のディジタル値及び直後のディジタル値を読み出したクロック信号を夫々P1及びP2とし、クロック信号P2の次のタイミングのクロック信号をP3とすると、P1とP2で読み出されるディジタル値の比率に対応する比率でP1、P3を使用する。

(もっと読む)

位相同期装置および位相同期回路の周波数キャリブレーション方法、並びにプログラム

【課題】アナログ特性を容易な設計で高速なデジタルアシストが可能な位相同期装置および位相同期回路の周波数キャリブレーション方法、並びにプログラムを提供する。

【解決手段】デジタルアシストキャリブレーション回路は、探索範囲を所定の値から順番に検索値を変更して、検索値と目的値との大小関係を確認する順次探索と、探索範囲の検索値の中央値と上記目的値との大小関係を確認し、目的値が含まれる側の半分の検索範囲に対してのみその半分の検索範囲の検索値の中央値と目的値との大小関係を確認して、目的値を検索していく二分探索と、を選択的に処理可能で、検索過程における最初の過程と最後の過程のうち、少なくとも最初の過程と最後の過程のいずれかにおいて二分探索を行い、残りの過程では順次探索処理を行う。

(もっと読む)

アキュムレータ型フラクショナルN−PLLシンセサイザおよびその制御方法

【課題】フラクショナル分周器の分周数を周期的に切り替えることに起因するフラクショナルスプリアスを抑制したアキュムレータ型フラクショナルN−PLLおよびその制御方法を実現する。

【解決手段】アキュムレータ型フラクショナルN−PLLシンセサイザ100を、その参照信号入力側の位相検出器の前段にアキュムレータ120からの誤差信号によって上記参照信号に対し位相調整を行う位相調整回路130を介挿して構成し、出力段のVCO114の出力を前段側にフィードバックするフラクショナル分周器115の出力である帰還信号と、上記位相調整された参照信号との両信号の位相差が生じないようにして、該両信号の位相差に応じた出力を得る位相検出器111の出力によってチャージポンプ112が駆動されないようにすることによって、フラクショナル分周器115の分周数を周期的に切り替えることに起因するフラクショナルスプリアスを抑制するように構成する。

(もっと読む)

クロック生成装置及びクロック同期方法

【課題】冗長構成を有するとともにクロックの同期が確実に行えるクロック生成装置、及び、クロック同期方法を提供する。

【解決手段】クロック生成装置は、クロックC1、クロックC2をそれぞれ出力するVCXO14、24と、クロックC1又はクロックC2が供給されるとともに主たる機能に使用される主機能部31に設けられ、クロックC1及びクロックC2の位相を比較し、クロックC1及びクロックC2の位相ずれの情報を含む位相差情報を生成する位相比較器33と、この位相差情報に基づいてVCXO24に出力する制御電圧を調整し、クロックC1の位相にクロックC2の位相を同期させる第2制御部22と、を有する。

(もっと読む)

位相同期回路およびその制御方法

【課題】ばらつき条件(温度、電源電圧、経年変化等)下の安定動作を補償しかつ低ゲインの電圧−周波数特性を実現できる位相同期回路を提供する。

【解決手段】バラクタアレイを有するVCO101と、VCO101の特性をモニターするモニター回路102と、モニター結果に応じてバラクタアレイに供給するオフセット量を切り替えるオフセット発生回路103とを備える。ばらつき条件下のVCOの特性をモニターした結果からバラクタアレイのオフセット量を調整することで、位相同期回路の動作不良を防ぐ。

(もっと読む)

フラクショナルPLL回路

【課題】分周器の分周比を変化させることを動作原理としない新規なフラクショナルPLL回路を提供する。

【解決手段】フラクショナルPLL回路は、位相周波数比較器1、チャージポンプ2、ループフィルタ、電圧制御発振器4、位相コントローラ5、及び位相選択回路6を備える。位相選択回路6は、電圧制御発振器4からの出力クロック信号vco_ckのクロックの1周期を等分した位相のうちのいずれかを選択し、選択された位相に立ち上がりエッジを有する移相クロック信号pi_outを生成し、これを帰還信号として位相周波数比較器1に送る。位相コントローラ5は、移相クロック信号pi_outの周期を出力クロック信号vco_ckの周期から予め決められた移相量で変化させるように、位相選択回路6によって選択される移相クロック信号pi_outの立ち上がりエッジの位相を決定し、決定された位相を選択するように位相選択回路6を制御する。

(もっと読む)

クロック生成装置及びDLL(DigitalLockedLoop)回路及びクロック生成方法

【課題】回路規模が小さく、また設計が容易な構成にて、高精度なクロックを生成するDLL回路を実現する。

【解決手段】DLL回路は、外部から入力される動作クロックclksと前記動作クロックと周波数が異なるもしくは等しい入力クロックと所望の周波数を表す設定値kから前記動作クロック周波数の前記設定値k分の一の周波数を有する生成クロックclkcを生成するクロック生成部100と、前記生成クロックclkcと外部から入力される参照クロックclkrの位相差を比較し、その位相差を出力する位相比較部200と、前記位相比較部200の出力である位相差から、前記位相差を“0”とするように前記設定値kへ補正をする補正値を生成し、前記設定値kへ補正値を加算する補正部300とを備える。

(もっと読む)

PLL回路

【課題】PLL回路の引き込時間を短縮する。

【解決手段】位相比較器10は、PLL回路100への入力クロックの位相と、PLL回路100の出力から分周器40を介して帰還される帰還クロックの位相とを比較し、その位相差に応じた信号を生成する。LPF20は、位相比較器10の出力信号に応じた直流電圧を生成する。電圧制御発振器30は、LPF20により生成された電圧に応じた周波数のクロックを出力する。サイクルスリップ予測回路50は、位相比較器10により生成される信号を監視し、サイクルスリップの発生を予測する。サイクルスリップ予測回路50によりサイクルスリップの発生が予測されたとき、入力クロックの位相、帰還クロックの位相および電圧制御発振器に入力される電圧のいずれかが調整される。

(もっと読む)

スペクトラム拡散クロックジェネレータ

【課題】 残ピークノイズを低減させることができるとともに、ジッターの増大を防止することのできるスペクトラム拡散クロックジェネレータを提供する。

【解決手段】 実施形態のスペクトラム拡散クロックジェネレータは、チャージポンプ回路1が、出力電流量が設定に応じて変化する可変電流源を有し、位相比較器14により検出された位相差に応じた期間、VCO11へ印加する電圧を制御するためのチャージ電流を出力する。

(もっと読む)

PLL回路および半導体装置

【課題】 PLL回路の発振精度の低下を抑制しつつ、ロックアップタイムを短縮する。

【解決手段】 PLL回路は、制御電圧に応じた周波数の出力信号を生成する電圧制御発振器と、出力信号を分周する分周器と、基準信号と分周された出力信号との位相差を検出し、位相差に応じて第1検出信号および第2検出信号を生成する位相比較器と、第1検出信号に基づいてオン/オフが制御される第1スイッチおよび第2検出信号に基づいてオン/オフが制御される第2スイッチを含み、制御電圧を調整するチャージポンプ回路と、チャージポンプ回路により充放電される容量素子を含み、チャージポンプ回路の出力を平滑化して制御電圧を生成するローパスフィルタと、電圧制御発振器に初期電圧を与える初期設定期間に、第1スイッチおよび第2スイッチの少なくとも一方をオンし、容量素子の充放電を制御することにより、制御電圧を初期電圧に設定する電圧供給部とを有している。

(もっと読む)

デルタシグマ変調型分数分周PLL周波数シンセサイザおよびそれを備えた無線通信装置

【課題】デルタシグマ変調型分数分周PLL周波数シンセサイザにおいて、スプリアスを抑制し、さらに、位相雑音特性を良好に保つ。

【解決手段】分周器(25)を変調することで分数分周を行うデルタシグマ変調型分数分周PLL周波数シンセサイザは、分数部データKに加算すべきシフト量Sを求め、シフト量Sと、シフト後分数部データK2とをそれぞれ出力する演算処理手段(27)と、シフト後分数部データK2を積分して量子化する第1のデルタシグマ変調器(28)と、シフト量Sを積分して量子化する第2のデルタシグマ変調器(29)と、第1のデルタシグマ変調器(28)の出力系列と第2のデルタシグマ変調器(29)の符号反転出力とを加算する第1の加算器(30)と、整数部データMと第1の加算器(30)の出力とを加算する第2の加算器(31)とを備え、第2の加算器(31)の出力により分周器(25)を変調させる。

(もっと読む)

PLL回路

【課題】 基準周波数断時におけるフリーランの出力周波数の精度を向上させるPLL回路を提供する。

【解決手段】 比例積分方式のPLL回路を用いて、積分器14の後にA/D変換部15とパタン生成部16を付加した構成とし、A/D変換部15が、ロック時の積分器14の出力電圧をデジタル信号として得て、ロック外れ時はロック時のデジタル信号を保持する機能を備え、ロック外れ時で基準周波数断時には、保持したデジタル信号に応じてパタン生成部16がパタン生成し、セレクタ13によって積分器14に出力するものであり、基準周波数断時には、パタン生成の波形を積分器14に代替入力するPLL回路である。

(もっと読む)

シリアルデータの受信回路、受信方法およびそれらを用いたシリアルデータの伝送システム、伝送方法

【課題】単一の伝送路で、高速なシリアルデータを伝送可能な伝送技術を提供する。

【解決手段】受信回路100は、pビットに2×q回(p、qは実数)の割合で第1レベルから第2レベルへの遷移が生ずるように生成されたシリアルデータDSOUTを受ける。VCO60は、入力された制御電圧Vcnt2に応じた周波数を有するサンプリングクロック信号CLK4を発生する。第1分周器22は、サンプリングクロック信号CLK4を分周比Mで分周する。第2分周器24は、受信したシリアルデータに応じたクロック信号CLKINを分周比Nで分周する。周波数比較器20は、第1分周器22の出力信号と第2分周器24の出力信号の位相差に応じた位相周波数差信号PFDを発生する。制御電圧生成回路42は、位相周波数差信号PFDに応じて、チャージポンプ回路40の周波数を調節するための制御電圧Vcnt2を生成する。

(もっと読む)

無線通信装置

【課題】無線通信装置の変調精度の低下を抑制しつつ、スプリアスによる受信特性の低下を抑制する。

【解決手段】デジタル部2は、アナログ部1にて周波数変換された受信信号の復調処理を行う。PLL回路25は、前記デジタル部のクロックを発生する。PLL設定変更部24は、現在の通信状態が受信状態であり、チャネル周波数内にスプリアスが存在し、受信電力が閾値に満たない場合、クロックCKのジッタを増加させ、それ以外の場合、クロックCKのジッタを通常設定にする。

(もっと読む)

デジタル位相比較器およびこれを備えたデジタルPLL回路

【課題】デジタル位相比較器におけるスタートアップ時のキャリブレーションを不要とする。

【解決手段】基準信号を遅延させて遅延基準信号として出力し、遅延量に相当する時間差を有する遅延量信号を出力する手段と、遅延基準信号と発振器出力信号との時間差をデジタル値に変換し第1のデジタル値として出力する手段と、第1の時間量子化器で発生した時間残差を検出し、時間残差に応じた時間差を有する時間残差信号を出力する手段と、基準信号の状態に応じて時間残差信号を出力するか遅延量信号を出力するかを切り替える手段と、時間残差信号の時間差をデジタル値に変換して第2のデジタル値として出力し、遅延量信号の時間差をデジタル値に変換して第3のデジタル値として出力する手段と、第2のデジタル値および前記第3のデジタル値を用いて第1のデジタル値を補正することで小数位相を算出する手段と、を有する。

(もっと読む)

PLL回路

【課題】周波数やロックアップ時間が変動したり、PLL特性が劣化したりするのを抑えることのできるPLL回路を提供する。

【解決手段】演算器15a,15bは、出力信号の目標の周波数を示す目標周波数設定値が変化した時、フラクショナル分周器17に対して目標周波数設定値で示される周波数と異なる周波数を示す周波数設定値を複数回設定する。そして、演算器15a,15bが周波数設定値を複数回設定した後に、演算器15a,15bから出力される周波数設定値は、目標周波数設定値と同じ値になる。これにより、周波数の引き込み動作時に、アナログスイッチング素子を用いてループフィルタの切り替えを行う必要がないため、スイッチング切り替え時に発生するノイズや、切り替え前後のループフィルタに生じる電圧差によって、発振器にノイズが発生することがない。

(もっと読む)

21 - 40 / 335

[ Back to top ]