Fターム[5J106DD09]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | スイッチ (729) | セレクタ (399)

Fターム[5J106DD09]の下位に属するFターム

マルチプレクサ (64)

Fターム[5J106DD09]に分類される特許

61 - 80 / 335

半導体装置及びその測定方法

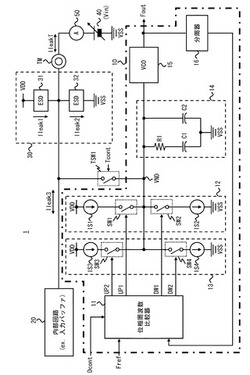

【課題】従来の測定方法では、測定電流の精度を十分に確保できない問題があった。

【解決手段】本発明の半導体装置の測定方法は、外部端子TMと、出力信号の位相及び周波数に応じてチャージポンプ回路12を制御する位相周波数比較器11と、周波数制御電圧生成ノードVNDに対する電流を出力するチャージポンプ回路12と、チャージポンプ回路12が出力する電流に応じて周波数制御電圧を周波数制御電圧生成ノードVNDに生成するループフィルタ14と、周波数制御電圧に応じて出力信号の周波数を制御する電圧制御発振器15と、を有する半導体装置の測定方法であって、外部端子TMを介してチャージポンプ回路12の出力電流を含む第1、第2の測定電流のいずれか一方を測定し、外部端子TMに流れるリーク電流を含む第3の測定電流を測定し、第1、第2の測定電流とリーク電流との差分に基づき流出電流IS1又は流入電流IS2の電流値を算出する。

(もっと読む)

クロックアンドデータリカバリ回路

【課題】ジッタトレランスの低下、引き込み時間の増大、引き込みが不能等の問題を解消するクロックアンドデータリカバリ回路を提供する。

【解決手段】多相の抽出クロック信号で入力データをサンプリングするデータサンプリング回路11からのサンプリングデータ信号群の比較結果に基づきクロック信号の位相を進める信号(UP1)又は位相を遅らせる信号(DOWN1)、エラー検出時エラー信号(ERR)を出力する位相検出器12と、UP1/DOWN1信号を積分する第1の積分器13と、第2の積分器14と、第1の積分器の出力値(PPM)に基づき所定のパターンを生成するパターン発生器15と、第2の積分器の出力とパターン発生器の出力を合成する混合器16と、入力クロックを入力し前記混合器の出力信号に基づき位相を可変させた前記多相の抽出クロックを生成する位相補間器17から構成される。

(もっと読む)

位相調整回路及び位相調整方法

【課題】消費電力を低減し、かつ回路面積も小さい位相調整回路を提供すること

【解決手段】位相調整回路100は、複数の遅延素子回路121〜124をリング状に結合したVCO120を有するPLL発振回路100を備える。また位相調整回路100は遅延素子回路を所望の遅延量に応じた数(125〜127)だけ有し、入力信号に前記所望の遅延量を与える位相遅延回路200、210を備える。PLL発振回路100は基準クロックの入力に応じた基準信号に、基準信号の所定周期分の遅延を与えた発振信号をVCO120において生成する。PLL発振回路100は、基準信号と、発振信号に応じた信号と、が略同位相となるように算出された遅延量に応じた遅延制御信号を遅延素子回路121〜124、及び遅延素子回路125〜127の各々に対して入力する。

(もっと読む)

半導体装置

【課題】位相同期回路の面積を低減しつつ特性を保持するために、プロセスマイグレーションに利点のあるデジタル補償回路を適用し、位相余裕を確保する半導体装置を提供する。

【解決手段】半導体装置のデジタル補償型位相同期回路200において、発振ノードに容量を具備し、印加電圧で連続的に制御される電圧制御型発振器104を含む位相同期回路100と、入力される位相差に応じて電圧制御型発振器104の発振ノードの容量を可変に制御するデジタル補償回路201とを有する。従来方式の印加電圧によって利得が決定される電圧制御型発振器104を、デジタル補償回路201の制御信号によって利得を離散的に変化させる。デジタル補償回路201は、電圧制御型発振器104の発振ノードに、位相進みに対して負荷を印加し、位相遅れに対して負荷を減らし、最適な位相余裕が確保できるように動的に利得を制御する。

(もっと読む)

クロック信号生成装置及び電子装置

【課題】目標周波数が変更されても、生成するクロック信号の周波数を短時間で目標周波数に一致させるクロック信号生成装置、及び、電子装置を提供することを目的とする。

【解決手段】第1制御部は、設定された目標周波数が第1の目標周波数から第2の目標周波数に変更されると、第1の所定のタイミングで、第1設定数として第3の数よりも小さい第5の数を前記第1カウンタに設定するとともに、第2設定数として第4の数よりも小さい第6の数を前記第2カウンタに設定し、第1の所定のタイミングの後の第2の所定のタイミングで、第3の数を前記第1カウンタに設定するとともに、前記第4の数を前記第2カウンタに設定する。

(もっと読む)

デジタル制御発振器

【課題】周波数制御により生じるノイズを低減すると共に、制御線を減少させて消費電力および面積を削減することが可能なデジタル制御発振器を提供する。

【解決手段】発振器制御ワードに応じた発振周波数の発振信号を出力するデジタル制御発振器であって、Nビットの前記発振器制御ワードを、上位N−A(但し、A≧1で、N>A)ビットと下位Aビットに分割し、前記上位N−AビットをN−AビットのBynary制御を行う第1のコードOTWbに、前記下位Aビットを2^(A+1)−2ビットのUnary制御を行う第2のコードOTWuに変換して出力する制御手段と、前記制御手段から出力される前記第1および前記第2のコードに応じた発振周波数の発振信号を出力する発振器24と、を備えている。

(もっと読む)

半導体集積回路

【課題】チップ面積の更なる縮小化を図ることができる半導体集積回路を提供する。

【解決手段】ディジタル制御発振器50−1〜50−nと、位相データ出力部100−1〜100−nと、積分処理部150と、フィルタ部151と、フィルタ部151からの時分割された出力信号に所定の係数を乗算した値を発振器制御値OTWとして出力する乗算器(第1の乗算器)40と、リファレンス周波数Frefに同期して、発振器制御値OTWを各ディジタル制御発振器50−1〜50−nに振り分ける出力セレクタ(制御値分離部)42と、を備える。

(もっと読む)

受信装置及びゲイン設定方法

【課題】受信特性を向上させることのできる受信装置を提供する。

【解決手段】受信装置は、受信データD1に基づいて抽出クロックCLKを生成するクロックデータリカバリ回路2と、受信データD1のジッタ量に応じて、上記クロックデータリカバリ回路2内のフィルタ回路11のゲインパラメータG1を設定するゲイン設定部3とを有する。

(もっと読む)

アナログ及びデジタルフィードバック制御を備えた位相ロック・ループ(PLL)

位相同期回路及びその制御方法

【課題】従来技術の位相同期回路では、入力クロックの切り替え時において、安定した出力クロックを生成することができないという問題があった。

【解決手段】本発明にかかる位相同期回路は、入力クロックを選択するセレクタ3と、入力クロックを分周する1/m分周器4と、フィードバッククロックを分周する1/n分周器5と、位相差検出器と、電圧保持回路30を有する電圧制御発振器10と、電圧保持回路31を有する電圧制御発振器11と、電圧制御発振器10,11のうちいずれかの出力を出力クロックとして出力するセレクタ13と、電圧制御発振器10,11のうちいずれかの出力をフィードバッククロックとして出力するセレクタ12と、備え、保持モードの電圧制御発振器が出力クロックfoutを生成し、通常モードの電圧制御発振器がフィードバッククロックを生成している場合に、入力クロックの切り替えが行われる。

(もっと読む)

PLL回路

【課題】ノイズフィルタ回路の特定を適切に自動設定可能なPLL回路を提供する。

【解決手段】PLL回路は、第1のクロック信号をフィルタ処理して第2のクロック信号を生成するフィルタ回路と、第2のクロック信号と第3のクロック信号との位相比較結果に応じた制御信号を生成する位相比較回路と、制御信号の値に応じた信号遅延をもたらす第1の遅延回路を少なくとも含み、信号遅延に応じて第3のクロック信号を発振する発振回路とを含み、フィルタ回路は、第1の遅延回路と同一構成であり制御信号の値に応じた信号遅延をもたらす第2の遅延回路を含み、第2の遅延回路により第1のクロック信号をフィルタ処理して第2のクロック信号を生成する。

(もっと読む)

半導体集積回路及びそれを用いた電子機器

【課題】低速ディジタル回路において発生するノイズがアナログ回路に与える影響を小さくし、回路ブロック毎のレイアウト変更を容易にする。

【解決手段】半導体集積回路は、(a)第1及び第2のVCOと、第1及び第2のVCOによって生成される信号を分周する第1及び第2の分周回路と、2つの分周信号の内の一方を選択する選択回路と、選択された分周信号に基づいて制御電圧を生成する制御電圧生成回路とを含むアナログ回路ブロックと、(b)変復調回路を含む第1のディジタル回路ブロックと、(c)制御回路を含む第2のディジタル回路ブロックとを備え、アナログ回路ブロックが、基板の第1及び第2の辺に沿って配置され、第2のディジタル回路ブロックが、基板の第3及び第4の辺に沿って配置され、第1のディジタル回路ブロックが、アナログ回路ブロックと第2のディジタル回路ブロックとの間に配置されている。

(もっと読む)

PLL回路

【課題】 位相ノイズを低減し、設計が容易なPLL回路を提供する。

【解決手段】 PLL3が、基準周波数とVC−TCXO4からの出力を入力し、ロック動作を行い、ロック状態となると、セレクタ6は基準周波数を分周する第1の分周器2の出力を選択し、PLL3が、基準周波数入力断又はロック外れを検出すると、アラーム信号をセレクタ6に出力し、セレクタ6が、PLL3からのアラーム信号が入力されると、第1の分周器2の出力から、VC−TCXO4の出力を分周する第2の分周器5の出力に切り替えて出力し、PLL7が、セレクタ6の出力とVCXO8の出力とを入力し、ロック動作を行うPLL回路である。

(もっと読む)

記憶装置およびDLL回路制御方法

【課題】セルフリフレッシュ動作後にDLL回路がロック動作を実行しない状況での記憶装置の評価を行うことが可能な記憶装置を提供する。

【解決手段】通常モードとテストモードとを有しセルフリフレッシュ動作を行う記憶装置は、DLL回路と制御部とを含む。DLL回路は、入力信号を受け付けると入力信号を遅延した遅延信号を出力し、また、入力信号と遅延信号との位相差が所定値になるように遅延信号の遅延量を設定するロック動作を行い、その後、位相差が所定値である状態を維持する。制御部は、通常モード下でセルフリフレッシュ動作が実行された後には、DLL回路にロック動作を実行させ、テストモード下でセルフリフレッシュ動作が実行された後には、DLL回路にロック動作を実行させない。

(もっと読む)

半導体集積回路

【課題】複数の無線通信チャンネルについて、PLL回路全体の動作特性に基づいて電圧制御発振器の精密なキャリブレーションを行う。

【解決手段】半導体集積回路は、高周波信号を生成する電圧制御発振器を含むPLL回路と、電圧制御発振器のトランジスタに選択的に負荷される複数のキャパシタと、複数の無線通信チャンネルについて電圧制御発振器の発振周波数を補正するためのキャパシタに関する情報を格納する格納部と、キャリブレーションモードにおいて、複数の無線通信チャンネルについてPLL回路のループ特性を測定することにより補正用キャパシタに関する情報を格納部に格納し、通常動作モードにおいて、選択された無線通信チャンネルに従って、格納部に格納されている情報を読み出すことにより補正用キャパシタを決定するキャリブレーション回路とを具備する。

(もっと読む)

PLLロック検出回路、及びPLLロック検出回路を有するPLLシンセサイザ回路

【課題】適切にPLL回路ロックがなされているか否かを検出する。

【解決手段】PLL回路ロックがなされているか否かを検出するPLLロック検出回路を構築する。ここにおいて、そのPLLロック検出回路は、基準発振器から供給される基準発振周波数を示す基準発振周波数信号と、前記基準発振周波数を分周して得られたリファレンス周波数を示し位相比較器に供給されるリファレンス周波数信号と、VCOから供給される電圧制御発振周波数を分周して得られた比較周波数を示し前記位相比較器に供給される比較周波数信号とを受ける、そして、前記リファレンス周波数信号と前記比較周波数信号とに基づいて、前記PLL回路ロックを示すロック検出信号を出力する。

(もっと読む)

スプレッドスペクトルクロック発生器及びそれを含む電子装置

【課題】新しい変調率及び変調周波数を有するスプレッドスペクトルクロック信号を生成することができるスプレッドスペクトルクロック発生器を提供する。

【解決手段】スプレッドスペクトルクロック発生器は、第1スプレッドスペクトルクロック信号を受信して第1スプレッドスペクトルクロック信号の平均周波数に対応する周波数信号を出力する発振回路と、周波数信号を受信して第2スプレッドスペクトルクロック信号を発生する位相固定ループと、第1及び第2スプレッドスペクトルクロック信号を受信して、第2スプレッドスペクトルクロック信号の平均周波数が第1スプレッドスペクトルクロック信号の平均周波数と近接するように位相固定ループを制御する制御回路を含む。このようなスプレッドスペクトルクロック発生器は、スプレッドスペクトルクロック信号を受信して、希望する変調率及び変調周波数を有する新しいスプレッドスペクトルクロック信号を発生する。

(もっと読む)

瞬時に同期を確立しかつ保持できる同期発振器

【課題】瞬時に同期を確立し、比較的に長時間、同期状態を高精度で保持することができる同期発振器を安価に実現する。

【解決手段】少なくとも、セットもしくはリセット付きカウンタ22と同期検出手段24とから構成され、前記同期検出手段24において、同期入力信号の立上り点、立下り点、もしくはゼロ交差点のタイミングを検出し、前記タイミングにおいて、前記カウンタ22をセットしあるいはリセットすることで、同期入力信号と瞬時に同期を確立し、前記同期入力信号が休止しあるいは停止した場合、あるいは取去られた後にも、比較的に長時間、同期状態を高精度で保持することができる。

(もっと読む)

半導体装置

【課題】出力ドライバのスイング能力を変化させた場合に生じるリードデータのスキューをキャンセルする。

【解決手段】リードデータDQを外部に出力する出力ドライバ90と、出力ドライバ90のスイング能力を設定するモードレジスタ53とを備える。出力ドライバ90によって駆動されるリードデータDQの遷移開始タイミングは、モードレジスタ53に設定された出力ドライバ90のスイング能力が相対的に大きく設定されている場合には相対的に早められ、モードレジスタ53に設定された出力ドライバ90のスイング能力が相対的に小さく設定されている場合には相対的に遅らせる。これにより、出力ドライバ90のスイング能力に関わらず、リードデータDQがしきい値レベルを超えるタイミングを所望のタイミングに一致させることが可能となる。

(もっと読む)

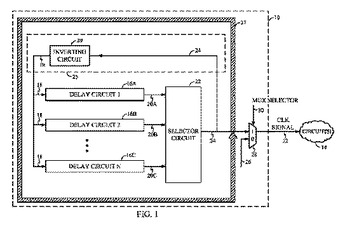

適応クロック発生器、システムおよび方法

機能回路のための、性能マージンを回避し、あるいは小さくするためのクロック信号を生成するために使用することができる適応クロック発生器、システムおよび関連する方法が開示される。特定の実施形態では、クロック発生器は、機能回路内の選択された遅延経路に関連する遅延回路に提供された遅延経路に従って、自律的に、かつ、適合的にクロック信号を生成する。クロック発生器には、入力信号を受け取るように適合され、かつ、出力信号を生成するために、受け取った入力信号を機能回路の遅延経路に関連する量だけ遅延させるように適合された遅延回路が含まれている。遅延回路には、上記出力信号に応答する帰還回路が結合されており、この帰還回路は、遅延回路に発振ループ構成で戻すための入力信号を生成するように適合されている。入力信号を使用して機能回路にクロック信号を提供することができる。  (もっと読む)

(もっと読む)

61 - 80 / 335

[ Back to top ]