Fターム[5J106DD09]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | スイッチ (729) | セレクタ (399)

Fターム[5J106DD09]の下位に属するFターム

マルチプレクサ (64)

Fターム[5J106DD09]に分類される特許

141 - 160 / 335

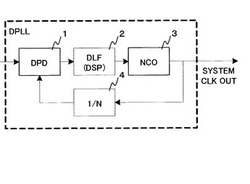

制御装置、クロック同期方法

【課題】DPLL回路において、入力クロックの瞬間的な位相跳びによる出力クロックの位相跳びの発生を抑制する。

【解決手段】出力クロックを入力クロックに同期させる制御を行う制御装置は、前記入力クロックと前記出力クロックとの位相差をカウントするカウント部と、前記カウント部がカウントした位相差のうち、所定範囲内の位相差を示すカウント値を抽出する抽出部と、抽出された前記所定範囲内の位相差を示すカウント値に基づいて位相差情報を生成する位相差情報生成部と、前記位相差情報生成部により生成された前記位相差情報に基づいて、生成する前記出力クロックの周波数を制御可能なクロック生成部と、を備える。

(もっと読む)

位相比較器、PLL回路、及び位相比較器の制御方法

【課題】電圧制御発振器VCOの出力信号と参照信号との位相差をデジタル信号として高精度に検知できる位相比較器、PLL回路、及び位相比較器の制御方法を提供する。

【解決手段】各々複数段縦列接続され、基準信号および対象信号が入力される遅延回路と、各々の段の遅延時間の差により、基準信号と対象信号との位相差を出力する保持回路と、その出力結果を元に、遅延素子の時間差及び大小を変更する論理回路とを備えた。

(もっと読む)

位相補間回路

【課題】線形領域での信号重ね合わせを行なうことなく所望の位相のクロック信号を生成可能な位相補間回路を提供する。

【解決手段】位相補間回路は、一定の周波数及び位相を有する基準タイミング信号のパルスの位相と同一の位相の第1のパルスと前記基準タイミング信号のパルスの位相からずれた位相の第2のパルスとを含むパルス列を生成するパルス列生成回路と、前記第1のパルスの位相と前記第2のパルスの位相との重み付け平均に応じた一定の位相位置にパルスを有する出力パルス信号を前記パルス列に基づいて生成するパルス位相平均化回路とを含み、前記重み付け平均の重みは、所定期間内において前記パルス列に含まれる前記第1のパルスの数と前記第2のパルスの数との比率に応じた重みである

(もっと読む)

半導体集積回路

【課題】リアルタイムクロック用の半導体集積回路の消費電力をさらに低減すると共に、生成されたクロック信号を周辺回路においても利用できるようにする。

【解決手段】この半導体集積回路は、外部から供給される電源電圧に基づいて、第1の電源電圧及び第2の電源電圧を生成する定電圧回路と、第2の電源電圧が供給され、発振動作を行うことにより原振クロック信号を生成する発振回路と、第2の電源電圧が供給され、原振クロック信号を分周することにより複数種類の分周クロック信号を生成する分周回路と、第1の電源電圧が供給され、分周回路によって生成される少なくとも1種類の分周クロック信号に基づいて計時情報を管理するロジック回路と、原振クロック信号と所定数の分周クロック信号との内の1つを選択するセレクタ回路と、選択されたクロック信号を出力端子に供給する出力回路とを具備する。

(もっと読む)

遅延クロック発生装置

【課題】多数段の遅延ステップで遅延時間を選択可能としながら、遅延ステップの直線性を確保し得る遅延クロック発生装置を提供する。

【解決手段】複数種類の遅延クロック信号を発生させる遅延クロック発生装置において、平行して配置された複数列の遅延素子列16a〜16dと、遅延素子列を構成する各遅延素子に設けられ、クロック信号CLKを往復方向に転送する往路側及び復路側転送線と、各遅延素子にそれぞれ設けられ、前後に連なる遅延素子の往路側転送線同士と復路側転送線同士を接続する第一の転送経路と、各遅延素子の往路側転送線と復路側転送線とを接続する第二の転送経路を選択する選択回路と、入力コードicodeに基づいて遅延素子列のいずれか一つの遅延素子でのみ選択回路で第二の転送経路を選択させるデコーダー12,13,14を備えた。

(もっと読む)

基準クロック周波数の決定および/またはループ発振器のロックを行うための方法、アルゴリズム、回路、およびシステム

【解決手段】 基準クロックの周波数を決定する装置、方法、システム、アルゴリズム、および回路を開示する。一実施形態によると、基準クロックの周波数を検出する回路であって、周波数が既知であり、精度は所定の値であるスリープクロックの所定の部分の間、基準クロックのサイクル数をカウントして、基準クロックサイクルカウント値を得るクロックカウンタと、基準クロックサイクルカウント値および既知であるスリープクロックの周波数に基づいて、基準クロックの周波数を推定する周波数推定部と、複数の許容周波数から、推定された基準クロックの周波数に最も近い周波数を選択する周波数選択部とを備える回路が提供される。 (もっと読む)

DLL回路及びその制御方法

【課題】冗長な回路、配線を不要とし、回路規模の増大を回避し、デューティを変更可能とするDLLを提供する。

【解決手段】外部信号の第1遷移(Rise)を可変に遅延させる第1可変遅延回路(10R)と、外部信号の第2遷移(Fall)を可変に遅延する第2可変遅延回路(10F)と、第1可変遅延回路(10R)の出力信号と第2可変遅延回路(10F)の出力信号とを合成する合成回路(13)と、合成回路(13)の出力信号のデューティの変更と検出を行うデューティ変更検出回路(21)と、デューティ変更検出回路(21)のデューティ検出結果(DCC)に従って第1可変遅延回路(10R)又は第2可変遅延回路(10F)の遅延を可変させる遅延制御回路(15R、15F)と、を備える。

(もっと読む)

遅延ロックループ回路

【課題】基準クロック信号の位相に対して、クロック信号の位相を制御する遅延ロックループ回路であって、回路規模の縮小化及び低消費電力化を図かったアナログDLL回路を提供する。

【解決手段】基準クロック信号の位相と、第1のクロック信号の位相とを比較し、比較結果に応じた信号を出力する位相比較器と、イニシャル信号の入力時において、位相比較器が出力する信号に応じた選択信号を発生する初期位相差検出器と、イニシャル信号の入力時において、初期位相差検出器からの選択信号に応じて、複数の位相が異なる第2のクロック信号の内から、基準クロック信号に最も近接した位相を有する第2のクロックを選択して、第3のクロック信号として出力する初期位相差設定回路と、第3のクロック信号に、位相比較器からの信号に応じた、位相遅延を付加した第1のクロック信号を出力する電圧制御可変遅延線とを備える遅延ロックループ回路を提供する。

(もっと読む)

信号の較正方法および装置

信号較正方式において、一連の複数の信号の間で所望の位相関係が維持される。たとえば、いくつかの態様では、高速度の基準クロック信号から発生したクロックツリーの所望の位相を、低速度の基準クロック信号と、クロックツリーの様々な位相に関連付けられた低速度のクロック信号との間の位相差を検出することにより、維持することが可能である。いくつかの態様では、クロックツリーの使用中に発生するフレーミングオフセットを検出することにより、クロックツリーの所望の位相を維持することが可能である。 (もっと読む)

DLL回路及びその制御方法

【課題】クロックのパルス幅が狭い場合、及び広い場合において、合成回路の誤動作を回避し、動作周波数の高速化に対応可能とするDLLの提供。

【解決手段】外部クロック(CK)の第1遷移(Rise)に対応して互いに異なる遅延時間の信号を出力し、CKの第2の遷移(Fall)に対応して互いに異なる遅延時間の信号を出力する第1の可変遅延回路20と、第1の可変遅延回路からの信号をそれぞれ受ける第2の可変遅延回路10R、10Fからの出力信号を合成して出力する第1の合成回路30とを備え、第2の可変遅延回路は第1の可変遅延回路からの信号からワンショットパルスを生成するワンショットパルス生成回路と、リセット端子を備えるラッチ回路と、ラッチ回路のセット出力の遷移エッジを受け、所定の比率で合成した信号を出力する第2の合成回路と、を備え、第2の合成回路の出力がラッチ回路のリセット端子に入力される。

(もっと読む)

周波数シンセサイザ

【課題】広帯域を細かく設定でき、周波数の引き込み範囲が広く、かつ消費電力の少ない周波数シンセサイザを提供する

【解決手段】電圧制御発振部1の出力周波数の正弦波信号を直交検波し、検波に用いた周波数信号の周波数との差分の周波数(速度)で回転するベクトルの位相差を取り出して出力周波数の調節に利用するPLLは、出力周波数調節用の第1の位相差検出部71と、周波数引き込み用の第2の位相差検出部74とを備え、前記第1の位相差検出部71の出力に係る信号をディジタル/アナログ変換した結果が予め定めたしきい値を越えたときに、前記第2の位相差検出部74の出力に係る信号をディジタル/アナログ変換する手段105から切り離すと共に、当該第2の位相差検出部74における消費電力を小さくする。

(もっと読む)

DLL回路

【課題】LSIを使用するユーザに制約を課すことなく、LSIを使用するユーザ毎に異なる様々なEMI防止機能の要求に対応するために、電磁放射が生じる周波数とその周波数における電磁放射強度を制御する。

【解決手段】DLL回路は、入力信号に基づいて同期基準信号を生成する入力回路101と、同期基準信号を遅延する第1遅延部102と、第1遅延部102によって遅延された同期基準信号の同期位置を調整し、同期対象信号を生成するタイミングオフセット回路103と、同期基準信号と同期対象信号との位相差を比較する位相比較回路105と、位相比較回路105の比較結果に基づいて第1遅延部102の出力信号を選択する第1制御回路106と、同期基準信号又は同期対象信号を遅延する第2遅延部104と、所定の設定情報を記憶する設定情報記憶回路108と、位相比較回路105の比較結果が所定の範囲内である場合に、設定情報記憶回路108に記憶された設定情報に基づいて第2遅延部104の出力信号を選択する第2制御回路107と、を備えている。

(もっと読む)

受信回路

【課題】入力データに位相を合わせたクロック信号を安定的かつ低消費電力で得る受信回路を提供する。

【解決手段】受信回路において、制御回路30、発振回路40、分周回路50、フリップフロップ回路、第1および第2の位相比較回路などを備え、発振回路40の発振周波数は、入力データに信号情報が有る時にはクロック信号と入力データの位相比較結果に基づいて制御し、入力データに信号情報が無い時にはクロック信号を分周して得たフィードバック信号と一定の周期で変化するリファレンス信号の位相比較結果に基づいて制御する。発振回路40は、2系統の制御信号によって発振周波数を制御でき、一方の系統の制御信号の変化に対しては徐々にかつ大きく発振周波数が変化し、他方の系統の制御信号の変化に対しては直ちにかつ小さく(少しだけ)発振周波数が変化するように構成する。

(もっと読む)

信号再生回路向け位相比較回路及び信号再生回路向け位相比較回路を備える光通信装置

【課題】 1/Nレート構成に対応可能な高精度な位相比較回路を得る。

【解決手段】それぞれ、N相クロック信号CLKの各クロック信号を、受信データ信号DINの立ち上がりに同期してトラックホールドするN個のトラックホールド回路を備える。これらのN個のトラックホールド回路の出力から、受信データ信号DINの立ち上がりエッジが、クロック信号CLKの立ち上がりエッジに位置しているクロック信号をトラックホールドしているもののみをセレクタで選択して、位相差信号として出力する。

(もっと読む)

位相同期回路及びその制御方法、通信装置

【課題】

安定した周波数の出力信号を出力できるようにした位相同期回路及びその制御方法、通信装置を提供する。

【解決手段】

位相同期回路は、入力される制御電圧に応じた周波数の信号を出力信号として出力する電圧制御発振回路と、入力信号と電圧制御発振回路の出力信号との位相を比較する比較手段と、位相の比較に基づく電圧を異なるタイミングでそれぞれ保持する2つ以上のサンプル/ホールド回路と、2つ以上のサンプル/ホールド回路のいずれかを選択し、該選択したサンプル/ホールド回路からの出力を制御電圧として電圧制御発振回路に入力する切換手段と、入力信号の異常を検出する異常検出手段とを具備し、切換手段は、異常検出手段による異常の検出結果に基づいて2つ以上のサンプル/ホールド回路のいずれかの出力を選択する。

(もっと読む)

半導体集積回路及びその制御方法

【課題】本発明は、安定ているクロックを生成するために、DLL回路のスマートパワーダウンモードを具現する半導体集積回路及びその制御方法を提供する。

【解決手段】本発明の半導体集積回路は、スマートパワーダウン信号がイネーブルされると、周期的にイネーブルされるパルス信号であるバッファイネーブル信号を生成するDLL制御手段;及び、バッファイネーブル信号に応じて外部クロックの位相を制御して、出力クロックを生成するDLL回路を含む。

(もっと読む)

DLL回路

【課題】広い周波数帯域で動作するDLL回路を提供する。

【解決手段】入力クロック信号CLKの周波数を検出する周波数検出回路12が設けられ、当該検出結果に応じたデータはレジスタ13に格納される。レジスタ13は当該検出結果に応じたモード切替信号MODEをVCDL回路11に出力する。入力クロック信号CLKの周波数が所定値より小さい場合は、各遅延素子の遅延量が大きくなり、入力クロック信号CLKの周波数が所定値以上の場合は、各遅延素子の遅延量が小さくなるように構成されている。具体的には、VCDL回路11において、各遅延素子の出力端子にスイッチと容量素子を付加し、モード切替信号MODEに応じてスイッチをオン・オフさせることで、容量素子を各遅延素子の出力端子に接続するか否かを切り替えるという構成が採用されている。

(もっと読む)

クロック・データ・リカバリ回路

【課題】

USB2.0規格などの高速シリアル通信に用いるクロック・データ・リカバリ回路に関し、受信データの取り込みエラーを防止し、かつLSI化に適した回路を提供する。

【解決手段】

周期T1のクロックをN分割したT2単位でずらしたN相のクロックを出力する手段6、シリアル転送された信号をT2毎にサンプリングしてT1毎にNビットパラレルデータに変換する手段4、その出力データをデジタル処理してNビットパラレルデータに変換する手段で、またデータ変化点を示すNビットパラレルデータに変換する手段8、変化点を示すデータを位相情報入力として前記デジタル処理されたデータのデータ変化点の略中間位置を示すデータを出力する手段10、その出力データが示したビット位置に対応する前記デジタル処理されたデータを復元データとする手段12を備える。前記デジタル処理は、移動平均処理、デューティずれ補正処理とすることができる。

(もっと読む)

デジタルDLL回路及び半導体装置

【課題】出力信号のジッターを低減可能としたデジタルDLL回路を提供する。

【解決手段】クロック信号CLKを1周期遅延させるための固定遅延素子の段数を選択する位相判定部1と、位相判定部1で選択した固定遅延素子の段数に基づいて、入力信号INを任意の位相量だけ遅延させて出力する固定遅延素子の段数を選択する位相調整部21とを備えたデジタルDLL回路において、位相調整部21は、選択信号に基づいて、複数段の固定遅延素子と、該固定遅延素子の1段当たりの遅延時間を1/2n刻みで調整する可変遅延部とで生成する遅延時間で、入力信号INを任意の位相量遅延させた出力信号OUTを生成する。

(もっと読む)

分周器

【課題】専用の発振器を用いないボーレート発生器のように分周する周波数の誤差を許容する分周器を簡素な構成かつ高精度で実現する。

【解決手段】分周器としてのボーレート発生器1は、所定の基準クロックRCLKを分周することにより、データをサンプリングするボーレートクロックBCLKを生成する。このボーレート発生器1は、m進/m−1進ダウンカウンタ2と、カウンタ切替制御部3とを備える。m進/m−1進ダウンカウンタ2は、異なる分周比を切り替えて基準クロックRCLKを分周する。カウンタ切替制御部3は、記ボーレートクロックBCLKの正規のボーレートクロックに対する1周期毎の誤差の累積値が所定範囲を超えると、前記累積値が減少するように、m進/m−1進ダウンカウンタ2の分周比を切り替える。

(もっと読む)

141 - 160 / 335

[ Back to top ]