Fターム[5J106DD09]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | スイッチ (729) | セレクタ (399)

Fターム[5J106DD09]の下位に属するFターム

マルチプレクサ (64)

Fターム[5J106DD09]に分類される特許

101 - 120 / 335

周波数逓倍遅延ロックループ

【課題】周波数逓倍回路を提供する。

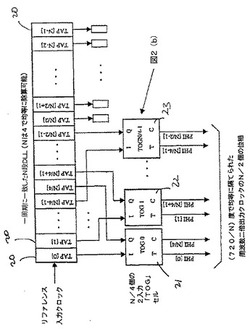

【解決手段】周波数逓倍回路(100)は、遅延ラインとクロック合成回路(TOG)を備える。遅延ラインは、その一端でリファレンスクロック(102)を受けて、一周期に一致した複数の遅延素子(101)からクロックタップ出力を発生させる。クロック合成回路(TOG)は、一対のタップ出力に応答して、各タップ出力から出力クロックパルスの立ち上がり及び立ち下がりエッジを発生させる。出力クロックの周期は入力クロックの周期よりも短い。遅延ラインは、遅延素子(101)の周期に一致するように遅延ロックループに含まれてもよい。所定数の遅延段タップ出力に接続された入力を有し、相補出力を供給する、複数の合成回路セル(TOG)が設けられる。セレクタ(106)は、位相検出器(112)からの選択制御信号に応答して、合成セルの1つに係る一対の相補出力のうちの一方から出力を選択する。

(もっと読む)

DLL回路及びこれを備える半導体装置

【課題】DLL回路のロックに要する時間を短縮する。

【解決手段】外部クロック信号CLKとレプリカクロック信号RCLKの位相差量を検出する位相差量検出回路100と、位相差量に基づいて外部クロック信号CLKを遅延させることにより内部クロック信号LCLKを生成する可変遅延回路21と、内部クロック信号LCLKを遅延させることによりレプリカクロック信号RCLKを生成するレプリカバッファ24とを備える。本発明によれば、外部クロック信号CLKに対してレプリカクロック信号RCLKの位相が進んでいるか或いは遅れているではなく、その位相差量に基づいて可変遅延回路21が制御されることから、位相差量が大きい場合であっても、高速にDLL回路をロックさせることが可能となる。

(もっと読む)

遅延信号生成回路、及び、遅延回路

【課題】入力された信号に所定の遅延時間を安定的に挿入し得る遅延信号生成回路及び遅延回路を提供する。

【解決手段】遅延信号生成回路は、供給される電源の電圧によって、その遅延時間が変化する、1又は複数の第1遅延回路と、前記第1遅延回路と同一の回路構成を有しており、供給される電源の電圧によって、その遅延時間が変化する第2遅延回路と、前記第1遅延回路と前記第2遅延回路に電源を供給する、制御電源回路とを有する、電源供給回路と、を備えるとともに、前記制御電源回路は、入力クロック信号と遅延クロック信号との間の位相差を検出し、前記位相差に基づいて、前記入力クロック信号と前記遅延クロック信号との間の位相差が解消されるように、前記第1遅延回路と前記第2遅延回路に供給する電源の電圧を制御する。

(もっと読む)

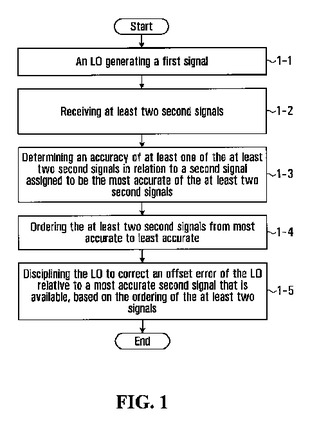

局部発振器を調整する装置及び方法

装置は、タイミング情報、周波数情報、位相情報及びそれらの組み合わせの内の少なくとも1つを有する第1信号を生成する局部発振器(LO)と、少なくとも2つの入力を有する優先制御部とを有し、入力の各々は、タイミング情報、周波数情報、位相情報及びそれらの組み合わせの内の少なくとも1つを有する第2信号をそれぞれ受信し、優先制御部は、少なくとも2つの第2信号の内の少なくとも1つの第2信号の精度を判定し、何れかの第2信号は少なくとも2つの第2信号の内で精度が最高であるように指定され、優先制御部は、最高精度から最低精度へ少なくとも2つの第2信号を順番に並べ、少なくとも2つの第2信号の順番に基づいて、装置に利用可能な最高精度の第2信号に対してLOのオフセットエラーを補正するように、LOが調整される。  (もっと読む)

(もっと読む)

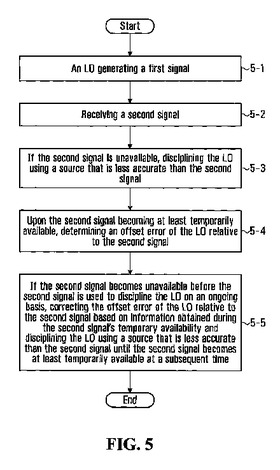

局部発振器を調整する装置及び方法

装置は、タイミング情報、周波数情報、位相情報及びそれらの組み合わせの内の少なくとも1つを有する第1信号を生成する局部発振器(LO)と、タイミング情報、周波数情報、位相情報及びそれらの組み合わせの内の少なくとも1つを有する第2信号を受信する入力を有するLOエラー補正部とを有し、第2信号はLOを調整するために使用され、LOエラー補正部は、第2信号がLOを調整するために利用可能でなくなった場合に、第2信号より精度が低いソースを用いてLOを調整し、第2信号が少なくとも一次的に利用可能になった場合に、第2信号に対するLOのオフセットエラーを判定し、当該装置が継続的にLOを調整するために第2信号を利用する前に、第2信号が利用可能でなくなった場合、第2信号が一次的に利用可能であった期間内に取得された情報に基づいて、第2信号に対するLOのオフセットエラーを補正し、第2信号が以後に少なくとも一次的に利用可能になるまで、第2信号よりも精度が低いソースを用いてLOを調整する。  (もっと読む)

(もっと読む)

ローカル信号生成回路

【課題】

周波数ホッピングを用いた通信を行うためのローカル信号生成回路が従来技術に開示されているが、実際に周波数ホッピングを用いたワイヤレスUSBの通信システムにおいては、ローカル信号の出力を開始してから出力が安定するまでに時間がかかり通信における規格を満たすことができないという課題が存在していた。

【解決手段】

第1の周波数で所定のバイアス電圧を中心に振動する第1のローカル信号を出力する第1の発振部と、前記第1の周波数より高い周波数である第2の周波数で前記バイアス電圧を中心に振動する第2のローカル信号を出力する第2の発振部と、前記第1および第2のローカル信号を入力すると共に前記第1のローカル信号および前記第2のローカル信号のそれぞれを選択的に出力し、前記第1のローカル信号および前記第2のローカル信号のそれぞれを出力しない期間においては前記バイアス電圧を出力する選択回路と、を有する。

(もっと読む)

クロック分配回路およびクロック分配方法

【課題】クロック分配網間のクロックスキューをより低減する。

【解決手段】リファレンスクロック信号11の位相を調整してクロック分配網に分配するPLL回路1、2と、クロック分配網における複数のフィードバック点PA1〜PAn、PB1〜PBnからそれぞれフィードバッククロック信号HA1〜HAn、HB1〜HBnを入力し、PLL回路1、2でリファレンスクロック信号11の位相比較対象とされる複数のフィードバッククロック信号から一つの信号を、複数のフィードバッククロック信号のそれぞれの遅延値に基づいて選択するフィードバッククロック信号選択回路9、16と、を複数のクロック分配網のそれぞれに対応して備える。

(もっと読む)

周波数同期装置、受信機および周波数同期方法

【課題】インパルス状の外乱が生じる環境でも、精度の良い周波数同期を確立することができる周波数同期装置を得ること。

【解決手段】再生周波数を受信信号に同期させる周波数同期制御を行う周波数同期装置であって、受信信号に基づいて周波数偏差を求める周波数偏差検出部2と、周波数偏差の時間変化量を算出する差分部3と、時間変化量に基づいて、前記周波数偏差を周波数制御値として用いるか否かを示す制御値選択信号を生成する観測部6と、制御値選択信号が周波数偏差を周波数制御値として用いないことを示す値であった場合には、過去の周波数制御値に基づいてその時点での周波数制御値の推定値である推定制御値を求め、求めた推定制御値を周波数制御値として選択するホールド部7と、を備える。

(もっと読む)

デジタルフェーズロックドループ回路

【課題】安定した位相同期ループを構成できない。

【解決手段】本発明は、第1、第2のクロック信号をカウントする第1、第2のカウンタと、第1のクロック信号を遅延させた第1、第2の遅延クロック信号を生成する遅延クロック生成回路と、第1のクロック信号及び第1、第2の遅延クロック信号のそれぞれで第2のカウンタのカウント値をサンプリングするサンプル回路と、第1、第2のクロック信号を所定の数で分周した第3のクロック信号との位相差と、サンプリングしたカウント値に応じ、そのサンプリングしたカウント値のうち1つを選択する選択回路と、第1のカウンタ及び選択回路が選択したカウント値に応じて第1、第3のクロックとの位相差を演算する位相誤差演算回路と、位相誤差演算回路の演算結果に応じて第2のクロックを出力するデジタル制御発振器とを有するデジタルフェーズロックドループ回路である。

(もっと読む)

デシリアライザ

【課題】PLL回路を用いずにクロックを同期させることを課題とする。

【解決手段】デシリアライザ部1は、PLL回路の代わりに、発振器2とクロック同期部10とを備える。クロック同期部10は、入力されたシリアルデータを段階的に遅延させることで異なる位相のデータを複数生成する。次に、クロック同期部10は、複数のシリアルデータそれぞれの位相と、発振器2によって発振されたクロックの位相とを比較する。そして、クロック同期部10は、比較結果に基づいて、発振器2によって発振されたクロックとの同期に適したシリアルデータを選択する。

(もっと読む)

衛星ナビゲーションシステムのためのマスタークロック生成装置

【課題】低廉な製作コスト及び部品コストで製造することができ、更に、マスタータイミング基準信号をより高精度で生成することのできる衛星ナビゲーションシステムのためのマスタークロック生成装置の提供。

【解決手段】複数の周波数信号入力部の各々に、原子時計信号から成る第1参照周波数信号と、原子時計信号から成る第2参照周波数信号との、いずれか一方を供給する。複数の周波数コンバータ(110、115、120、125)は、互いに同一周波数の中間周波数信号を出力する。スイッチングマトリクス130は、前記中間周波数信号のうちの1つを主クロックとして選択して送出すると共に、別の1つを副クロックとして選択して送出する。周波数信号生成器150は、前記主クロックから基準周波数信号を生成し、複数の周波数信号出力部へ送出する。位相メーター170は、前記主クロックと前記副クロックとの間の位相差を測定し、異常挙動を検出する。

(もっと読む)

クロック・データ再生回路及び再生方法並びに局側装置

【課題】バースト信号間の無信号区間に入ったとき、一時的に参照クロック信号と周波数が大きくずれるという現象の発生を防止することができるクロック・データ再生回路及び再生方法並びに当該再生回路を用いた局側装置を提供する。

【解決手段】周波数逓倍部110により、参照クロック信号の周波数をデータ信号相当の周波数に逓倍して逓倍クロック信号とする他、入力選択部111を用いて入力を選択する。すなわち、データ信号としてのバースト信号が入力されているときは、入力されたバースト信号と位相が同期するように再生クロック信号を生成し、バースト信号が入力されていないときは逓倍クロック信号と位相が同期するように再生クロック信号を生成する。

(もっと読む)

半導体装置

【課題】フラクショナルN−PLL回路における出力クロック信号でのスプリアスの発生を抑制する。

【解決手段】出力クロック信号を出力する電圧制御発振器と、出力クロック信号を分周して分周クロック信号を生成し、基準クロック信号と分周クロック信号とを比較し、比較結果に基づき出力信号を出力するN個の制御ユニットと、各制御ユニットからの出力信号を加算する加算器と、加算器の出力をフィルタ処理し電圧制御発振器に出力するローパスフィルタとを備え、分周クロック信号に同期して所定の順序で巡回させ供給するN個のデータからなる分周比に係る設定情報を、各制御ユニットに対して初期値を互いに異ならせて供給し分周動作及び比較動作を行わせるようにして、N個の制御ユニットにより移動平均フィルタを形成し量子化ノイズを低減し、出力クロック信号でのスプリアスの発生を抑制できるようにする。

(もっと読む)

デジタルPLL回路及び半導体集積回路

【課題】粗調整用と微調整用のコンデンサを切り替えて発振回路の発振周波数を調整する際に、粗調整区間に生じるサイクルスリップに起因して発振周波数可変範囲が狭くなるのを回避可能なデジタルPLL回路及び半導体集積回路を提供することである。

【解決手段】インダクタンス素子に並列接続される容量素子の数を変えて発振周波数が制御される発振回路4と、基準クロック及びその遅延クロックと発振回路出力とをデジタル位相比較し、その比較結果に基づいて容量素子の並列接続数を制御し、発振回路出力の位相を基準クロック位相に近づける制御をする位相比較部6とを具備し、容量素子は、インダクタンス素子に並列接続可能な所定容量の粗調整用コンデンサ43と、これに並列接続可能で粗調整用コンデンサの1/n容量を有し、粗調整時に所定数の微調整用コンデンサが1つの粗調整用として制御される複数の微調整用コンデンサ44を備える。

(もっと読む)

放射線硬化チャージポンプ・トポロジ

【課題】シングル・イベント・アップセット(SEUs)により影響されにくいチャージポンプ回路を提供する。

【解決手段】第1のチャージポンプ出力を備えた第1のチャージポンプ30と、第2のチャージポンプ出力を備えた第2のチャージポンプ32と、前記第1のチャージポンプ出力及び前記第2のチャージポンプ出力を入力するように受け取り、第1の一致信号を出力するように生成する第1の一致検出器34と、第1の一致信号に基づいて、前記第1のチャージポンプ出力、または、前記第2のチャージポンプ出力のいずれかを選択するためのアナログ2:1マルチプレクサ36とを有する。

(もっと読む)

位相調整装置及び無線受信装置

【課題】効率的に且つ比較的低消費電力で目的の信号との位相を調整するのに好適な位相調整装置及び無線受信装置を提供する。

【解決手段】位相調整装置100を、遅延量を可変可能なインバーター回路IV1〜IVNをループ構成に接続してなる遅延段回路10と、遅延段回路10の遅延量を一定に保持する位相同期用回路20と、遅延段回路10の各接続部に入力端子が電気的に接続された接続切替回路SW1〜SWMを含む接続切替回路群30と、切替制御回路40と、信号出力回路50とを含む構成とし、切替制御回路40は、遅延段回路10における各インバーター回路に対応する接続切替回路を1つずつ且つ周回して選択し、選択した接続切替回路SWからのみ遅延信号を出力するように制御すると共に、偶数番目に選択された接続切替回路SWからの遅延信号を反転して後段の回路に供給するように信号出力回路50を制御する。

(もっと読む)

チャージポンプ、周波数シンセサイザ、及び、制御方法

【課題】出力電圧が変化したときでも、電流値の変化を抑制できるチャージポンプを提供する。

【解決手段】電流源101は、出力端子157に向けて電流を流し、電流源102は、出力端子157から電流を引き抜く。電流調整回路108は、電流源101及び102の電流を制御する。電流調整回路108は、電流源102を所定の電流が流れるように制御しつつ電流源101を電流源102を流れる電流とバランスするように制御する第1のモードと、電流源101を所定の電流が流れるように制御しつつ電流源102を電流源101を流れる電流とバランスするように制御する第2のモードとを切り替え可能である。判定回路105は、出力端子157の電圧に応じて、第1のモードと第2のモードとを切り替える。

(もっと読む)

クロック生成回路

【課題】位相ロックの精度を向上する。

【解決手段】クロック生成回路は、出力クロックの周期または位相を段階的に遅延する第1の遅延回路および前記第1の遅延回路の遅延時間を設定し制御する第1のカウンタを有する逓倍回路と、前記逓倍回路内の第1の遅延回路から出力された前記出力クロックを入力し、前記出力クロックを所定時間遅延させる第2の遅延回路および前記第2の遅延回路の遅延時間を設定し制御する第2のカウンタを有する位相同期回路を備え、前記逓倍回路は、初期値が第1の値であり第1のカウンタのカウンタ値が一定時間以内で変化しない場合に第2の値が設定される第3のカウンタをさらに有し、前記第3のカウンタのカウンタ値が前記第1の値から前記第2の値に変化した時、前記第2の遅延回路の遅延時間が前記第1の遅延回路の遅延時間と同じかあるいは少し長い遅延時間となるように前記第2のカウンタのカウンタ値を設定する。

(もっと読む)

クロック供給装置

【課題】運用系および待機系システムクロックの位相を、バックボード間の配線遅延量、温度変化および電圧変動に起因するバッファ遅延の変化量を含め一致させたシステムクロック供給装置を提供する。

【解決手段】システムクロック1に位相同期した運用系および待機系システムクロック6を出力する冗長構成とされた運用系および待機系システムクロック供給部200と運用系および待機系システムクロックを装置内各部へ分配するためのバックボード8を有する。システムクロック1に位相同期したクロック22を生成するPLL210は、運用系システムクロックを基準とし、待機系システムクロックの位相を制御する位相差調整部211を含んだ構成とする。

(もっと読む)

データ再生回路

【課題】バースト光信号が入力された場合のロックアップ動作を高速に行うデータ再生回路を得ること。

【解決手段】本発明にかかるデータ再生回路は、VCO4で生成したクロックと入力データとを比較し、比較結果に基づいてVCO4への入力電圧を調整するPLL回路(周波数・位相比較器1,フィルタ処理回路2,VCO4)と、VCO4で生成されたクロックを利用して入力データを識別再生する識別回路6と、各子局装置からの送信スケジュールに基づいて、データ入力区間を特定する受信タイミング生成回路8と、を備え、PLL回路は、第1のデータ入力区間が終了後、その次の第2のデータ入力区間が開始するまでの区間では、第1のデータ入力区間に含まれるEOB区間でVCO4への入力としていた電圧信号を、VCO4へ継続して入力させる。

(もっと読む)

101 - 120 / 335

[ Back to top ]