Fターム[5J106DD09]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | スイッチ (729) | セレクタ (399)

Fターム[5J106DD09]の下位に属するFターム

マルチプレクサ (64)

Fターム[5J106DD09]に分類される特許

41 - 60 / 335

クロック発振回路及び半導体装置

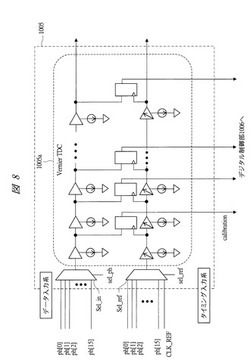

【課題】起動時にTDCにキャリブレーション処理を加えることで、時間分解能のばらつきが発生することを防ぎ、合わせて、遅延用の素子の冗長度を減らすことで回路規模の増大を防ぐ手段を提供する。

【解決手段】電源投入時等に多相発振器型TDCであるPDC_c及びバーニア型TDCであるPDC_fのキャリブレーションを実行する。キャリブレーション時にはPDC_fに入力するタイミング入力を参照クロックCLK_REFからDCCOの出力信号のうち一つを選択する。またデータは、先のDCCOの出力信号に隣接し、位相が進んだ出力信号とし、その間の遅延を導出する。これを全出力信号繰り返すことで、DCCOの出力信号1周期を導出する。

(もっと読む)

送信装置、受信装置及び伝送システム

【課題】簡易な構成によりクロックリカバリを実現し、伝送時のオーバーヘッドを削減する。

【解決手段】送信装置1−1は、制御用メタデータを生成し、制御用メタデータを定期的に受信装置2−1へ送信する。また、送信装置1−1は、コンポーネントの符号化を行い、自身のコンポーネントのクロックを用いてPCR、DTS及びCTSを生成し、または、他のコンポーネントのクロックを用いてDTS及びCTSを生成し、コンポーネントの符号データ等を受信装置2−1へ送信する。受信装置2−1は、制御用メタデータを定期的に受信すると共に、コンポーネントの符号データ等を受信する。そして、受信装置2−1は、制御用メタデータに従って、受信したPCRに基づいて自身のコンポーネントのクロックに対しクロックリカバリを行い、復号等を行う。また、受信装置2−1は、他のコンポーネントのクロックを流用して復号等を行う。

(もっと読む)

電子機器およびクロック補正方法

【課題】 RC発振器によりクロック信号を生成するシステムにおいて、クロック信号の周波数を大きく変動させずに補正して規定の範囲に保つことのできる電子機器およびクロック補正方法を提供することにある。

【解決手段】 RC発振器の抵抗または容量の設定を切り替えてクロック信号の周波数を複数段階に変更可能な周波数変更手段と、この複数段階の変更量を表わしたトリミングテーブルを記憶する記憶手段と、周波数変更手段の設定を切り替えてクロック信号の周波数を補正するクロック補正制御手段とを備えた電子機器およびそのクロック補正方法である。そして、クロック補正制御手段は、トリミングテーブルのデータに基づき、クロック信号の周波数を補正前の周波数から規定の周波数へ次第に近づいていくように周波数変更手段の設定を切り替えて(S7,S8)、クロック信号の周波数を補正する。

(もっと読む)

デジタルPLL回路、情報再生装置、ディスク再生装置および信号処理方法

【課題】複数の倍速に対応できることを前提に、再生性能を落とすことなくトータルの回路規模および消費電力が小さく、しかもループ遅延が小さい安定なPLLを提供する。

【解決手段】A/D変換器は入力チャネルレートに依存せず高速なサンプリングを行い、ダウンコンバータにより必要なチャネルレートに落とす。これにより倍速数に依存せずにAAFの特性を単一化できるためアナログ回路を小型化できる。また、デジタル位相追従部は補間型完全デジタル位相追従構成とすることでループ遅延を最小化できる。一方、CAV再生時には入力レートに応じてタウンコンバータのデシメーション比Mを変更することでデジタル回路の動作クロックが必要以上に上がることを押さえ消費電力増加を防ぐ。デシメーション比Mの切り替え時はデジタル回路内部遅延を考慮してデジタル位相追従部の内部周波数切り替えタイミングを遅らせることで位相周りのないシームレスな切り替えを実現する。

(もっと読む)

大きな温度変動に対する発信周波数の安定化方法

【課題】

超高温から極低温までの温度変動が極めて大きい環境に設置される無線機器に適用できる発信周波数の安定化方法を提供する。

【解決手段】

複数の発信回路を備え、筐体内の温度を測定する筐体内温度測定ステップと、測定した筐体内温度Tと予め定められた温度T0、T1、・、Tk、・Tnとの大小関係から測定した温度範囲を判定する温度範囲判定ステップと、 温度範囲判定ステップが判定した温度範囲に応じて複数の発信回路のいずれかを選択する回路選択ステップとを有し、筐体内温度TがTk−1≦T<Tkの範囲であった場合に、回路選択ステップは当該温度範囲において、発信器の発信周波数が希望の範囲に納まるように予め調整されている発信回路等を選択する。

(もっと読む)

クロック発生装置

【課題】広い温度範囲で高精度なクロック信号を出力可能な、安価でかつコンパクトなサイズのクロック発生装置を提供する。

【解決手段】クロック発生装置は、基準クロック信号を生成する基準クロック生成部11と、第1のクロック信号を生成する第1の発振器12と、前記第1のクロック信号を前記基準クロック信号と同周波数、同位相となるように補正した第2のクロック信号を生成する第1の精度保証部13と、温度検知部15と、第3のクロック信号を生成する第2の発振器17と、前記第3のクロック信号を前記基準クロック信号と同周波数、同位相となるように補正した第4のクロック信号を生成する第2の精度保証部18と、温度が第1の発振器12の保証温度範囲内の場合には前記第2のクロック信号、保証温度範囲外の場合には前記第4のクロック信号を出力するクロック切替部20と備える。

(もっと読む)

PLL周波数シンセサイザ

【課題】位相雑音特性の劣化を回避し消費電力を低減するデジタルPLL周波数シンセサイザを提供する。

【解決手段】デジタルPLL周波数シンセサイザ101において、ロック検出後に第1の発振信号位相情報から、前回の発振信号位相情報と位相差εとから推定部20にて推定した第2の発振信号位相情報に切り替えることにより、通常状態(ロック状態)において誤差を持つ危険を抱えた第1の発振信号位相情報を使用せず、また、従来のリクロックのための高速動作するラッチ回路も不要とする。これにより、位相雑音特性の劣化を回避しつつ、従来に比べて消費電力を低減する。

(もっと読む)

位相同期回路および無線受信装置

【課題】サブサンプリングPLLの利点を保持したまま、フラクショナル分周を実現する。

【解決手段】電圧制御発振器は、制御電圧に応じて周波数が制御される第1信号、および前記第1信号と逆相の第2信号を生成する。サブサンプリング位相比較器は、基準信号の周期毎に、前記第1信号および第2信号の電圧を標本化して、第1標本化電圧および第2標本化電圧を生成する。電流生成回路は、供給電圧に応じて第1電流信号を生成する第1のチャージポンプと、供給電圧に応じて前記第1電流信号と反対符号の第2電流信号を生成する第2のチャージポンプとを有する。セレクト制御手段は、前記第1および第2標本化電圧を前記第2および第1チャージポンプにまたはこれと反対に供給する第1、第2供給モードを選択的に実行する。ループフィルタは、前記第1、第2の電流信号の合成電流信号を平滑化して、前記電圧制御発振器に与える前記制御電圧を生成する。

(もっと読む)

クロック発生回路

【課題】 PLLを動作させた状態で、同期外れを起させず、入力クロックの切り替えおよびそれに伴う分周比の切り替えを行うことが可能なクロック発生回路を提供する。

【解決手段】 タイミング制御部8は、入力クロックを指定するクロック選択情報が切り替わった後、分周器1がリファレンスクロックCLKREFを出力するのに応じて、クロック選択指令SELCKを切り替える動作と、分周器1に1個のリファレンスクロックCLKREFを出力させるための入力クロックの個数Rと、分周器6に1個のフィードバッククロックCLKFBを出力させるための出力クロックCLKOの個数Fのうちの少なくとも一方の設定を切り替え、切り替え後の設定個数Rに対応した入力クロックの分周器1によるカウント動作および切り替え後の設定個数Fに対応した出力クロックの分周器6によるカウント動作の両方を開始させる。

(もっと読む)

クロックデータリカバリ回路

【課題】簡易な構成で、データおよびクロック間のタイミングスキューの制約をなくすとともに、データの周波数可変範囲を広くとることができるCDR回路を提供する。

【解決手段】CDR回路は、基準クロック信号を用いてクロック信号を所望の周波数にロックするLTモードと、クロック信号をデータ信号に位相同期させる通常動作モードとを有する。CDR回路は、VCOと、入力信号を平滑化して制御電圧を生成してVCOに出力するLPFと、LTモード時に、基準クロック信号とクロック信号との周波数比較を行ない、該比較結果に応じた信号をLPFに出力する周波数ループと、通常動作モード時に、データ信号とクロック信号との位相比較を行ない、該比較結果に応じた信号をLPFに出力する位相ループと、基準クロック信号の周波数カウント値に応じてVCOに設定する周波数レンジを調整する周波数検出回路とを備える。

(もっと読む)

半導体集積回路

【課題】チップサイズの大型化を防止することができる半導体集積回路。

【解決手段】同一のリセット信号が入力されることにより、互いに同期が取られる複数の送信ブロックを備える半導体集積回路。各送信ブロックは、基準クロック信号とフィードバッククロック信号との位相差に応じた制御電圧に基づいて周期Tの第1のクロック信号を発振する電圧制御発振器と、第1のクロック信号がN(Nは自然数)分周された第2のクロック信号が入力され、当該第2のクロック信号から、第1の送信用クロック信号と当該第1の送信用クロック信号よりも周波数の低い第2の送信用クロック信号とを生成し、リセット信号に応じて少なくとも第2の送信用クロック信号を出力するリセット機能付き分周器と、第1及び第2の送信用クロック信号が分配される複数の送信機と、を備える。

(もっと読む)

クロック供給装置およびクロック供給方法

【課題】発振器のウォームアップの完了を容易に判定できるようにする。

【解決手段】クロック供給装置1は、通信装置内の処理に用いられるクロック信号を供給する。発振器1aは、クロック信号を生成する。測定部1bは、通信装置に接続された伝送路から抽出されたリファレンスクロック信号を取得し、クロック信号とリファレンスクロック信号との周波数ずれを測定する。判定部1cは、周波数ずれの測定結果と電力供給の状況とに基づいて、発振器1aのウォームアップが完了したか否か判定する。

(もっと読む)

CDR回路、受信装置、および通信システム

【課題】簡易な回路構成で、高速かつジッタ入力に強く、信号エラーの発生を抑止することが可能なCDR回路、受信装置、および通信システムを提供する。

【解決手段】CDR回路310は、遅延素子312−1〜312−4を含み、定期的に信号遷移の挿入されたデータ入力をトリガとしてクロックを抽出する分周器320と、分周器で抽出されたクロックに同期して入力データ信号をラッチするラッチ315−1〜315−8とを有する。

(もっと読む)

周波数シンセサイザ装置及び変調周波数変位調整方法

【課題】2つの変調経路を有する周波数シンセサイザ装置において、DACから電圧制御発振器に出力される制御電圧の振幅を適切に調整することができる。

【解決手段】周波数シンセサイザ装置10は、入力電圧に応じた発振周波数で発振する電圧制御発振器14、電圧制御発振器14からの信号を分周するプログラマブル分周器20、分周信号と基準クロックとの位相差を電圧制御発振器14に出力する周波数位相比較器22、送信データに応じて目標周波数変位分周波数を変位させる場合の調整電圧を電圧制御発振器14に出力するDAC12、調整電圧の校正時に、電圧制御発振器14を基準電圧電源に接続するスイッチ32、任意の送信データをDAC12に出力して発振させた状態で分周信号の周波数をカウントしたカウント値に基づいて、目標周波数変位に対応する調整電圧に対応した調整データを設定する変調周波数変位校正回路30を備える。

(もっと読む)

位相同期ループ回路および位相同期ループ回路の制御方法

【課題】チップサイズの増大を抑え、広帯域の発振周波数帯域を有するPLL回路等を提供する。

【解決手段】VCO34は、制御電圧VTに応じた発振周波数fVCOを有する出力クロック信号CLKOを生成する。PLLブロック2は、制御電圧VTを生成する。ロック検出器24は、発振周波数fVCOが設定周波数fSにロックされているか否かを検出する。VT電圧検出部31は、バラクタVA1ないしVA3のうちの何れを選択するかを決定する。セレクタ部32は、出力クロック信号CLKOの粗調整段階においてはバラクタVA0を選択する。また、粗調整段階においてロック検出された旨をロック検出器24から受信することに応じて、微調整段階へ移行する。微調整段階においては、移行時点におけるVT電圧検出部31によって選択されていたバラクタの選択を維持する。

(もっと読む)

PLL回路

【課題】ロックアップタイムの高速化とリファレンスリークの低減化をとバランス良く達成する。

【解決手段】電圧制御発振器(104)の制御電圧VCONTをアナログ/デジタル変換して得られるデジタル信号(ADCO)を出力するアナログ/デジタル変換回路(106)と、基準クロック信号(FREF)と帰還クロック信号(FDIV)とがロックしたことを検出した時にロック検出信号(S201)を出力するロック検出部(201)と、ロック検出部からロック検出信号が入力された時にアナログ/デジタル変換回路から入力されたロック時デジタル信号を保持する保持部(107)と、保持部に保持されたロック時デジタル信号とアナログ/デジタル変換回路から出力されたデジタル信号との比較結果に基づいてチャージポンプ電流の電流量を段階的に減少させるチャージポンプ電流量制御信号(CPCONT)を生成するチャージポンプ制御部(108)と、を備えるPLL回路。

(もっと読む)

位相差検出回路、定遅延時間周波数分周回路、および位相同期回路

【課題】より高い周波数において、高い精度で出力信号の位相(タイミング)変動を抑えることのできる位相差検出回路、定遅延時間周波数分周回路、および位相同期回路を得る。

【解決手段】入力信号をN分周し、パルス幅が前記入力信号の周期のB倍となる出力信号を生成し、ここで、Nは、任意の整数であり、Bは0<B<Nを満たす整数ではない実数として規定される分数パルス幅出力分周器(1)と、入力信号と出力信号の排他的論理和信号を生成する演算回路(2)と、排他的論理和信号に対して、特定のよりも低い低域周波数成分の信号を通過させ、入力信号に対する出力信号の遅延時間に相当する値を位相差検出信号として出力する低域通過フィルタ(3)とを備える。

(もっと読む)

周波数シンセサイザ

【課題】

応答性が高く維持され、かつハードウェアの構成が簡略化されるにもかかわらず、各部の変動やバラツキに対して安定に適応できる周波数シンセサイザを提供する。

【解決手段】

位相同期ループが供給する制御情報に対応した所望の周波数で出力信号を生成する可変周波発振器を有し、前記所望の周波数となり得る目標周波数毎に、前期可変周波発振器に与えられるべき制御情報の初期値が予め登録されたテーブルと、前記所望の周波数が切り替えられたときに、前記位相同期ループの応答を規制し、かつ最新の所望の周波数に対応して前期テーブルに登録されている初期値を前記可変周波発振器に供給する初期値設定手段と、前記位相同期ループのロックアップを前記位相差に基づいて検出するロックアップ検出手段と、前記ロックアップが検出されたときに、前記応答の規制を解除し、かつ前記初期値設定手段による初期値の供給を規制する位相同期再開手段とを備える。

(もっと読む)

クロック発生回路

【課題】ロックアップタイムを短くすることのできるクロック発生回路を提供する。

【解決手段】クロック発生回路1は、基準クロックRCLKに基づいて、周波数を変調させた変調クロックSCLKを発生するスペクトラム拡散クロック発生回路10と、基準クロックRCLKと変調クロックSCLKとの位相の一致を検出したときにHレベルのロック信号LOCKを出力する位相比較器20とを含む。また、クロック発生回路1は、Hレベルのロック信号LOCKが出力されるまでは基準クロックRCLKを出力クロックCLKとして選択し、Hレベルのロック信号の出力に応答して変調クロックSCLKを選択するセレクタ50を含む。

(もっと読む)

PLL周波数シンセサイザ

【課題】改善された位相雑音特性を有するPLL周波数シンセサイザを提供する。

【解決手段】VCO20は、制御電圧VCNTに応じた周波数fVCOで発振する。周波数ミキサ22は、VCO20の出力信号SVCOとローカル周波数fLOを有するローカル信号SLOを周波数ミキシングする。第1フィルタ26は、ミキサ22によるミキシングにより得られる差周波信号SDIFFを抽出する。位相誤差検出部12は、第1フィルタ26により抽出された差周波信号SDIFFと基準周波数fREFを有する基準信号SREFの位相を比較し、位相差に応じた位相誤差信号VPEを生成する。ループフィルタ18は、位相誤差信号VPEをフィルタリングし、制御電圧VCNTを生成する。第2フィルタ28は、ミキサ22によるミキシングにより得られる和周波信号SSUMを抽出し、出力端子OUTから和周波信号SSUMを出力する。

(もっと読む)

41 - 60 / 335

[ Back to top ]