Fターム[5J106DD09]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | スイッチ (729) | セレクタ (399)

Fターム[5J106DD09]の下位に属するFターム

マルチプレクサ (64)

Fターム[5J106DD09]に分類される特許

201 - 220 / 335

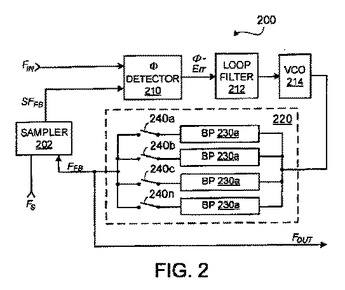

偽信号化された周波数上の位相ロック

位相ロックループ(200)は、サンプラー(202)、位相検出器(210)、ループフィルタ(212)、VCO(214)を含む。ループは、ループのフィードバックパス中に分割器を必要とすることなく周波数逓倍を達成する。VCO(214)は、サンプラーのナイキストレートより上で動作され、ループが偽信号化された信号上にロックすることを引き起こす。VCO出力周波数中のあらゆる変動(即ち、ジッターまたは位相ノイズ)は、周波数分割器に通常関連付けられる減衰無しで、1対1で位相検出器(210)にフィードバックされる。ループゲインは従って、高い閉ループ周波数逓倍を提供するループにおいてでも、高く保つことができる。一変形によると、高調波発生器(540)がVCOとサンプラーの間に置かれ、よってループがVCO周波数の高調波上にロックすることを引き起こす。開ループゲインと精度はよって更に向上される。  (もっと読む)

(もっと読む)

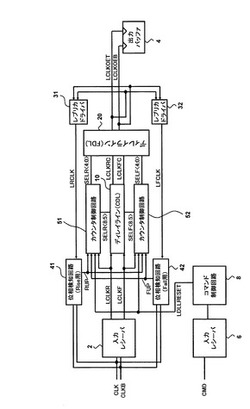

DLL回路及びこれを用いた半導体記憶装置、並びに、データ処理システム

【課題】FDLを調整するカウント信号のビット数を増加させても、高速に遅延量を確定させることが可能なDLL回路を提供する。

【解決手段】相対的に粗い調整ピッチでクロック信号を遅延させるディレイライン(CDL)10と、相対的に細かい調整ピッチでクロック信号を遅延させるディレイライン(FDL)20と、ディレイライン10,20の遅延量を制御する位相検知回路41,42及びカウンタ制御回路51,52とを備える。カウンタ制御回路51,52は、線形探索法によってディレイライン10を制御するとともに、二分探索法によってディレイライン20を制御する。これにより、ディレイライン20を調整するカウント信号のビット数を増加させても、高速に遅延量を確定させることが可能となる。

(もっと読む)

デジタル制御発振回路、周波数シンセサイザ、それを用いた無線通信機器及びその制御方法

【課題】周波数が直線的に変化する範囲が広く且つ占有面積が小さいデジタル発振回路を実現できるようにする。

【解決手段】デジタル制御発振回路10は、複数の第1の可変容量素子からなる第1の容量素子群14及び複数の第2の可変容量素子からなる第2の容量素子群14を含む可変容量部12を有し、可変容量部12の容量値に対応した発振周波数の信号を生成する発振部を備えている。第1の可変容量素子の第1の容量変化量は、第2の可変容量素子の第2の容量変化量に2以上の整数値を乗じた値であり、第2の可変容量素子の個数は、2以上の整数値から1を減じた値以上である

(もっと読む)

クロックデータ再生回路

【課題】高速シリアルデータ転送の受信回路において、低消費電力モードから通常モードに復帰する際の復帰時間を短縮する。

【解決手段】シリアルデータ転送路から転送される同期用クロックを含むシリアルデータから同期用クロック及びデータを再生するクロックデータ再生回路であって、シリアルデータ及び基準クロックを電力モードに応じて選択してクロックデータ再生回路に供給する選択回路を具備する。

(もっと読む)

可変タイミングメモリ

【課題】同期回路装置の設計に於いて、タイミング最適化の作業工程を削減化する。

【解決手段】同期回路装置10内の可変タイミングメモリ20のモジュールは、メモリアレイ21とその入出力メモリ制御回路22,23に加えて、クロック端子Tに入力したクロック信号CLKを遅延する信号線24と、クロック信号CLKをそのまま伝送する信号線25と、両信号線24,25を入力とするセレクタSL1と、メモリライト/リード信号が印加され且つセレクタSL1のセレクト端子と繋がったタイミングモード端子TMTとを有する。セレクタSL1は、メモリライト信号の受信に応じて信号線24を選択し、遅延されたクロック信号を入出力メモリ制御回路22,23に印加する。他方、メモリリード信号の受信に応じてセレクタSL1は信号線25を選択し、クロック信号CLKをそのまま入出力メモリ制御回路22,23に印加する。

(もっと読む)

周波数調整装置及びそれを含むDLL回路

【課題】半導体集積回路の電磁干渉を減少させる周波数調整装置及びそれを含むDLL回路を提供する。

【解決手段】本発明の周波数調整装置は、基準クロックに応答して1ビットずつレベル遷移する複数のビットの周波数制御信号を生成する周波数制御信号生成部と、及び前記複数のビットの周波数制御信号に応答して、入力される基準クロックの周波数を調整する周波数調整部とを含むことを特徴とする。また、他の発明の周波数調整装置は、基準クロックの周波数を複数の分周比に分周して複数のビットの周波数制御信号を生成する周波数制御信号生成部、及び複数のビットの周波数制御信号に応答して、入力される基準クロックの周波数を調整する周波数調整部とを含むことを特徴とする。

(もっと読む)

PLLとその駆動方法

【課題】ロックタイムを短縮することができ、ロック動作において電力を効率的に消費することができるPLL(Phase Locked Loop)を提供すること。

【解決手段】基準クロックとフィードバッククロックとの位相差を検出し、それに対応する検出信号を生成する位相検出手段と、前記検出信号に対応する電圧レベルを有する制御電圧を生成する制御電圧生成手段と、該制御電圧のレベルに対応する周波数を有する内部クロックを生成する電圧制御発振手段と、前記基準クロックの周波数に対応するスタートアップレベル多重化信号に応答して、前記電圧制御発振手段の起動前に制御電圧端を所定のスタートアップレベルに駆動するスタートアップ駆動手段とを備えるPLLを提供する。

(もっと読む)

PLL回路

【課題】目標周波数の変更に応じて、制御電圧が所定の許容範囲内に収まるようにVCO特性が切り替えられるものであって、かかる切替を極力早いタイミングで実行し得るPLL回路を提供する。

【解決手段】複数のVCO特性に切替可能である電圧制御発振部と、位相比較器と、制御電圧と所定の許容範囲との比較結果に応じてVCO特性の切替を行うVCO切替部と、を備え、現時点で目標周波数に設定されている周波数のクロックを出力するPLL回路であって、VCO切替部は、サンプリングされた電圧が許容範囲内に収まっているか否かを検出するとともに、該検出結果に応じて、前記VCO特性の切替えを行うものであり、このサンプリングのタイミングは、目標周波数が切り替えられた時から、予め定められた時間である第1時間が経過したタイミングとされているPLL回路とする。

(もっと読む)

DLL回路

【課題】DLL回路を備えたLSIの電磁放射強度を低減し、電磁放射ノイズの電子機器への影響を低減する。

【解決手段】DLL回路は、入力信号に基づいて同期基準信号を生成する入力回路101と、同期基準信号を遅延する第1遅延部102と、前記第1遅延部102によって遅延された同期基準信号の同期位置を調整し、同期対象信号を生成するタイミングオフセット回路103と、 前記同期基準信号と前記同期対象信号との位相差を比較する位相比較回路105と、前記位相比較回路105の比較結果に基づいて前記第1遅延部102の出力信号を選択する第1制御回路106と、前記同期基準信号又は前記同期対象信号を遅延する第2遅延部104と、前記位相比較回路105の比較結果が所定の範囲内である場合に、前記第2遅延部104の出力信号を選択する第2制御回路107と、を備え、前記位相比較回路105は、前記同期基準信号と前記同期対象信号のうち前記第2遅延部104によって遅延された信号と他方の信号との位相差を比較する。

(もっと読む)

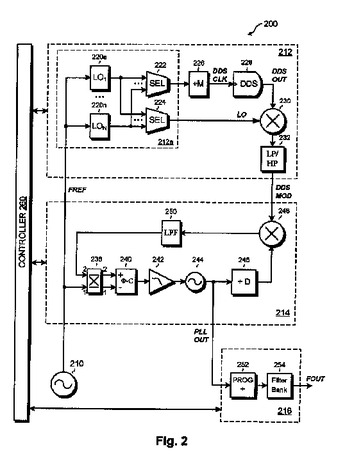

コスト的に有効な低ノイズの単一ループシンセサイザー

低コストで低位相ノイズのマイクロ波シンセサイザーは、DDS変調回路と位相ロックループを含む。DDS変調回路はDDSの出力を高周波数に変調する。位相ロックループはDDS出力をダウンコンバートし、ダウンコンバート信号を比較的低周波数の固定されたリファレンスにロックする。  (もっと読む)

(もっと読む)

CDR回路

【課題】異なる複数のビットレートの入力データを再生できるようにしたCDR回路を提供する。

【解決手段】参照クロックCKの周波数に対応した制御信号Vrにより第2の電圧制御発振器3の発振周波数が決定されるPLL回路と、制御信号Vrにより第2の電圧制御発振器3の発振周波数と同じ周波数で再生クロックCLK1を発振し且つ入力データのタイミングに合わせて該再生クロックCLK1の発振位相が調整される第1の電圧制御発振器1と、入力データを再生クロックCLK1によりリタイミングするフリップフロップ回路2とを備えるCDR回路において、PLL回路に、分周比の異なる2個の分周器7A,7Bと、該分周器7A,7Bの内の1つを選択するセレクタ8とを備えさせる。

(もっと読む)

PLL回路および再生装置

【課題】データ信号からクロックを復調する際に、周波数ロックがはずれることを防ぎ、再生装置の再生品質を高める。

【解決手段】PLL回路200は位相追従ループと周波数追従ループを備える。周波数追従ループは、周波数比較器202とローパスフィルタLPF225とを備える。周波数比較器202は、復調クロックCLKとデータ信号S1との周波数差を検出し、検出結果に応じた周波数誤差信号を出力する。LPF225は、周波数誤差信号に応じて充放電するコンデンサ226の充放電により周波数誤差信号を平滑して周波数制御電圧信号FVCを得る。第1の制御部240と第2の制御部250は、周波数ロック状態において、周波数比較器202からLPF225への出力が遮断されるオフ期間と遮断されないオン期間が交互に繰り返されるように制御し、オフ期間においてリーク電流に起因するFVCの変動を補正する。

(もっと読む)

タイミングクロック生成装置、データ処理装置及びタイミングクロック生成方法

【課題】 好適なタイミングでデータを読み込むことができるクロックを簡単に生成することができるタイミングクロック生成装置を提供する。

【解決手段】 基準となるシステムクロックをデータの入力タイミングに同期させる第1PLL回路21と、システムクロックの周波数を所定倍に逓倍した逓倍クロックを生成する第2PLL回路23及び2分周回路24と、逓倍クロックの遷移タイミングのうち、データの取込みに使用するタイミングを選択する制御部5と、選択された遷移タイミングに同期し、システムクロックと同一周波数を有するデータ取込み用クロックを生成する位相調整・分周回路26と、を有している。

(もっと読む)

シンボル同期回路

【課題】同期回路が1系統で、温度変化等によるクロック位相ずれの増大を防止できるシンボル同期回路を提供すること。

【解決手段】シンボル同期回路は、戻し段数決定部104を有し、可変遅延器101から左端信号109及び右端信号110を取り出す。左端信号109と右端信号110は、クロック信号107をそれぞれ異なる遅延段数により遅延させた信号である。遅延段数とは、クロック信号107を遅らせるために通過させた遅延素子の個数を意味する。戻し段数決定部104は、左端信号109と右端信号110の位相差がクロック周期の自然数倍の時間に最も近くなるときの、左端信号109と右端信号110のそれぞれの遅延段数の差を、戻し段数として算出する。巡回制御部103は、戻し段数決定部104から指示される段数に基づいて戻し処理を行なう。

(もっと読む)

クロックリカバリ回路

【課題】シリアル伝送されるデータにノイズが混入しても、そのノイズの影響を少なくすることができるクロックリカバリ回路を提供する。

【解決手段】基準クロックから多相クロック生成部5で生成された多位相クロックのうち、入力されたシリアルデータの変化点の中間(真中)に立ち上がりがあるクロックを選択して出力するクロックリカバリ回路1において、入力データのエッジを検出した後に、所定以下の信号幅のノイズ成分を除去するノイズキャンセル部3を設け、ノイズ成分によるクロックの切替えが起らないようにしてクロック選択部4へ出力する。

(もっと読む)

スペクトラム拡散クロックジェネレータ

【課題】 PVT変動に起因して周波数変調プロファイルが変化することを防止することができるスペクトラム拡散クロックジェネレータを提供する。

【解決手段】 入力クロックCLKINと出力クロックCLKOUTの位相を位相比較記30で比較し、その比較結果信号POに基づいて制御回路20で新たな遅延パターンを算出し、その新たな遅延パターンに従って1クロックパルス毎に遅延セル11_0,11_1,11_2,11_3,…,11_N−2,11_N−1,11_Nの段数を切替信号S[0],S[1],S[2],S[3],…,S[N−2],S[N−1],S[N]により切り替えながら入力クロックCLKINを入力させて周波数変調を行なう。

(もっと読む)

無線受信回路および入力妨害波低減回路

【課題】広い周波数領域に渡って妨害波を低減できる入力妨害波低減回路の小型化、およびそのような入力妨害波低減回路を備える無線受信回路の小型化を図る。

【解決手段】受信信号は、トランジスタQ1のゲートに与えられる。トランジスタQ1はトランジスタQA〜QDに接続され、トランジスタQ1、QA〜QDにより4個の増幅器が構成される。トランジスタQA〜QDには、それぞれ調整回路13A〜13Dが接続されている。調整回路13A〜13Dは、LC共振回路であり、その共振周波数は調整信号および微調整信号により調整される。選択信号は、4個の増幅器の中から使用すべき増幅器を選択する。選択された増幅器の利得周波数は、対応する調整回路(13A〜13D)の共振周波数に応じて決まる。選択された増幅器により増幅された信号が出力される。

(もっと読む)

位相補間器

【課題】プロセス条件、電源電圧、温度の変動によらず、微小な位相をプログラマブルに調整できる位相補間器を提供する。

【解決手段】PLL回路のフィードバック信号(FBCLK)に非等間隔なクロックを入力し、PLL回路が本来備える位相合せ機能により、基準信号REFCLKとフィードバック信号FBCLK間に微小な位相差を与え、かつ、アップ、ダウン電流が等しいチャージポンプ(CP)回路を用いてプロセス条件、電源電圧、温度依存性が無い位相差を実現する。

(もっと読む)

クロック発生装置

【課題】PLL回路を使用し、より幅広い環境変動に適応して周波数を一定値にロックすることのできるクロック発生装置を得る。

【解決手段】クロック発生装置200は、基本的に同一構成で共にLC型VCOを備えた第1および第2のPLL回路201、202を備えている。マスタ側の第1のPLL回路201の第1のVCO2241に加わる第1の制御電圧2281は基準電圧検出回路212で3つの固定値と比較され、その結果に応じて第2のPLL回路202の容量スイッチ247、257の値を調整しておいて、出力セレクタ207で第1のPLL回路201から第2のPLL回路202にクロックの選択を切り替える。

(もっと読む)

クロック制御回路、集積回路装置及び電子機器

【課題】ノイズフィルタでは完全には除去することができないようなノイズがクロック信号に発生した場合でも、このクロック信号で動作する回路の誤動作を防止することができるクロック制御回路を提供すること。

【解決手段】クロック制御回路10は、発振クロック22の電圧が所定の範囲にあるか否かを判断し、発振クロック22の電圧が所定の範囲にない時はノイズ検出信号128を生成するノイズ検出回路120と、ノイズ検出信号128に基づいて、少なくとも所定の期間、クロック出力停止信号138を生成するクロック出力停止信号生成回路130と、発振クロックを所定の時間遅延させた遅延クロック信号148を生成する遅延クロック生成回路140と、クロック出力停止信号138が存在する期間は、遅延クロック信号148の外部への出力を停止するように制御するクロック出力停止制御回路150と、を含む。

(もっと読む)

201 - 220 / 335

[ Back to top ]