Fターム[5J106GG17]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 制御対象 (2,074) | 定電圧回路、定電流回路 (29)

Fターム[5J106GG17]に分類される特許

1 - 20 / 29

PLL回路および半導体装置

【課題】 PLL回路の発振精度の低下を抑制しつつ、ロックアップタイムを短縮する。

【解決手段】 PLL回路は、制御電圧に応じた周波数の出力信号を生成する電圧制御発振器と、出力信号を分周する分周器と、基準信号と分周された出力信号との位相差を検出し、位相差に応じて第1検出信号および第2検出信号を生成する位相比較器と、第1検出信号に基づいてオン/オフが制御される第1スイッチおよび第2検出信号に基づいてオン/オフが制御される第2スイッチを含み、制御電圧を調整するチャージポンプ回路と、チャージポンプ回路により充放電される容量素子を含み、チャージポンプ回路の出力を平滑化して制御電圧を生成するローパスフィルタと、電圧制御発振器に初期電圧を与える初期設定期間に、第1スイッチおよび第2スイッチの少なくとも一方をオンし、容量素子の充放電を制御することにより、制御電圧を初期電圧に設定する電圧供給部とを有している。

(もっと読む)

クロック発生器、電子機器、及びクロックを発生するための制御方法

【課題】周波数変調機能をオフした際のロックアップタイムを短縮することが可能なクロック発生器、及びクロック発生器の制御方法、並びに電子機器を提供すること。

【解決手段】周波数変調機能を有するクロック発生器で、リファレンスクロックを元にフィードバック制御を加えて、位相の同期した出力クロックを出力する位相同期ループと、出力クロックの周波数を変動させる変調制御回路と、を備え、変調制御回路は、周波数変調機能がオフされた際に、出力クロックの周波数を所望の周波数へ収束させるタイミングを速くする構成とする。

(もっと読む)

差動論理回路、分周回路、及び周波数シンセサイザ

【課題】動作電流を変えても直流出力電圧の変わらない差動論理回路及び分周回路、さらには、周波数シンセサイザにおける動作電流の調整方法を提供する。

【解決手段】複数対の差動論理信号を入力し論理演算を行ってその結果を一対の差動信号出力端子から出力する差動論理部と、差動論理部に電流を供給する電流源回路であって前記電流の大きさが制御可能な電流源回路と、差動信号出力端子に接続された負荷回路と、負荷回路に接続され、一対の差動信号出力端子の直流出力電圧が一定の電圧になるように負荷回路の負荷を制御する負荷制御回路と、を備える。

(もっと読む)

タイミング・モジュールのホールドオーバのための内蔵自己検査のシステム及び方法

【課題】本発明の実施例は、局所発振器を有する装置において使用される方法を含む。

【解決手段】方法は、外部レファレンス信号によって統制される局所発振器について外部レファレンス信号にロックされている間に、外部レファレンス信号の関数であり、発振器におけるドリフトを統制するために使用される関数である補正信号に少なくとも部分的に基づいて数学的モデル毎の予測補正信号を求めるよう発振器の少なくとも2つの数学的モデルを訓練する工程を含む。方法は更に、外部レファレンス信号が利用可能でなく、発振器におけるドリフトを統制するために別の補正信号を使用する場合に最小の時間誤差を少なくとも2つの数学的モデルのうちの数学的モデルも含む。方法は、訓練に使用される期間に加えた検査持続時間の必要なしに、選択された数学的モデルを使用することが可能であるように、補正信号のサンプリングされたバージョンを使用して、選択された数学的モデルを検査する工程を更に含む。

(もっと読む)

電圧制御型発振回路及び電圧変換回路

【課題】複雑な定電流源を使用せずに簡単な回路構成で制御電圧がゲートしきい値電圧以下でも制御電流を流すことができる電圧変換回路及び電圧制御型発振回路を提供すること。

【解決手段】電圧−電圧変換回路101は、制御電圧VINをゲート端子に受けるn型MOSトランジスタN110と、基準電圧VRをゲート端子に受けるn型MOSトランジスタN111と、n型MOSトランジスタN110,N111の共通ドレイン端子をドレイン端子に接続し、ソース端子を高電位電源VDDに接続するp型MOSトランジスタP110と、n型MOSトランジスタN110,N111の共通ソース端子と接地GND間に接続される抵抗体R100とを備える。電圧電流変換回路100は、さらに生成された制御電流に対応する動作電流が流されて電流値に応じた周波数で発振するリングオシレータ201と、基準電圧VRを印加するバイアス電圧発生回路301とを備える。

(もっと読む)

PLL方式発振回路、ポーラ送信回路及び通信機器

【課題】VCO101の変調感度のばらつきを低減し、高速、高精度に所望の出力振幅を得ることができるPLL方式発振回路を提供する。

【解決手段】振幅検出器103は、VCO101の出力振幅を検出する。振幅制御部105は、振幅検出器103が検出したVCO101の出力振幅が所望の振幅になるように可変電流源109の電流値を制御する。LPF108は、振幅制御部105と可変電流源109との間に接続される。スイッチ107は、LPF108を振幅制御部105と可変電流源109との間に接続するか否かを切り替える。振幅制御部105は、LPF108又は切り替えスイッチ107のいずれか一方を介して、可変電流源109と接続される。

(もっと読む)

DLL回路及びこれを用いた半導体記憶装置、並びに、データ処理システム

【課題】FDLを調整するカウント信号のビット数を増加させても、高速に遅延量を確定させることが可能なDLL回路を提供する。

【解決手段】相対的に粗い調整ピッチでクロック信号を遅延させるディレイライン(CDL)10と、相対的に細かい調整ピッチでクロック信号を遅延させるディレイライン(FDL)20と、ディレイライン10,20の遅延量を制御する位相検知回路41,42及びカウンタ制御回路51,52とを備える。カウンタ制御回路51,52は、線形探索法によってディレイライン10を制御するとともに、二分探索法によってディレイライン20を制御する。これにより、ディレイライン20を調整するカウント信号のビット数を増加させても、高速に遅延量を確定させることが可能となる。

(もっと読む)

位相ロック回路

【課題】位相ロック回路において、電圧制御発振回路や分周回路の性能が設計時よりばらついた場合であっても、電圧制御発振回路が出力する高速クロックを分周回路で良好に分周できるようにして、不良品を低減する。

【解決手段】第1の分周回路4に加えて、この分周回路4よりも動作速度の遅い第2の分周回路5を備える。前記2つの分周回路4、5で分周されたクロックの周波数同士を周波数比較回路6で比較し、第2の分周回路5の分周クロックの周波数よりも第1の分周回路4の分周クロックの周波数の方が速い場合には、VCO発振抑制回路7が電圧制御発振回路3出力クロックFoutの発振周波数を抑制する。

(もっと読む)

PLL回路、およびそれを備えた無線装置

【課題】低消費電力で、広い発振周波数範囲に対応したPLL回路を提供する。

【解決手段】電圧制御発振器10と、電圧制御発振器10の発振信号を分周し発振分周信号を出力する分周器30と、分周器30の発振分周信号と基準信号の位相差を出力する第1の位相比較器40と、第1の位相比較器40の出力信号を電圧制御発振器10の制御用信号に変換するチャージポンプ60と、チャージポンプ60の出力信号のうちDC成分を通過させ、電圧制御発振器10に電圧を出力するフィルタと、分周器30の発振分周信号と基準信号との位相差を時間平均する第2の位相比較器90と、第2の位相比較器90において時間平均された位相差に基づいて、分周器10の動作電流を制御する電流制御回路100とを備えたものである。

(もっと読む)

リアルタイムクロック装置および該リアルタイムクロック装置を用いた半導体装置ならびに電子機器

【課題】低消費電流および安定動作を実現することができるリアルタイムクロック装置および該リアルタイムクロック装置を用いた半導体装置ならびに電子機器を提供すること。

【解決手段】水晶発振回路11と、該水晶発振回路11の出力を分周する計時回路(高速部)13と、計時回路(高速部)13の出力を分周する計時回路(低速部)14と、外部との間で信号のやり取りをするインターフェース回路15からなり、水晶発振回路11は第一の電圧VR1で駆動され、計時回路の少なくとも一部分(高速部)13は第二の電圧VR2で駆動され、計時回路の残りの部分およびインターフェース回路15は第三の電圧VDDで駆動され、第一の電圧VR1<第二の電圧VR2<第三の電圧VDDの大小関係を有する。第一の電圧VR1と第二の電圧VR2は第三の電圧VDDから生成される。

(もっと読む)

キャリブレーション装置、試験装置、キャリブレーション方法、帯域測定装置、及び帯域測定方法

【課題】PLL回路に対して、予め定められたループ帯域を精度よく設定できるキャリブレーション装置を提供する。

【解決手段】PLL回路の電圧制御発振器に入力される制御電圧に、ループ帯域のカットオフ周波数の周波数成分を含むキャリブレーション信号を重畳する信号重畳部と、電圧制御発振器が出力する発振信号のカットオフ周波数の周波数成分を測定する測定部と、キャリブレーション信号のカットオフ周波数成分の強度と、測定部が測定した周波数成分の強度とを比較する演算部と、演算部における比較結果に基づいて、PLL回路に設けられたチャージポンプのゲインを調整する調整部とを備えるキャリブレーション装置を提供する。

(もっと読む)

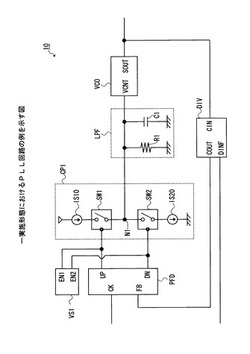

周波数シンセサイザ、および周波数シンセサイザの発振制御方法

【課題】 ロック状態を維持したまま発振周波数帯域の切り替え動作が可能な周波数シンセサイザを、小規模であって低消費電流な回路構成で実現する周波数シンセサイザ、および周波数シンセサイザの発振制御方法を提供すること

【解決手段】 発振周波数帯域の切り替えが可能な発振制御回路2を備える周波数シンセサイザ1は、発振周波数帯域の違いによる発振制御回路2へのバイアス信号IBの差を、差分バイアス信号ΔIBとして出力する差分バイアス部5と、発振周波数foが発振周波数帯域fbの限界値を越えて遷移したことを検出する帯域限界検出部3と、帯域限界検出部3による検出に応じて、発振周波数帯域fbの切り替えのために差分バイアス部5の動作が切り替えられる過渡期間において、差分バイアス部5に対して、出力されるバイアス信号IBを漸次遷移する制御を行なう過渡制御部4とを備えている。

(もっと読む)

位相同期ループ回路、半導体集積回路、および、受信装置

【課題】使用する電圧制御発振器の選択、および、その発振周波数範囲の設定をより効率的に行うことができる位相同期ループ回路を実現する。

【解決手段】位相同期ループ回路100の制御部103は、位相同期ループ回路100に接続する電圧制御発振器として、複数の電圧制御発振器VCO1〜VCOnのうちから、選局周波数を含む主発振周波数範囲をもつ電圧制御発振器を選択し、その後、選択された電圧制御発振器の発振周波数範囲を、選局周波数を含む副発振周波数範囲に設定する。

(もっと読む)

半導体集積回路

【課題】複数のシリアル伝送チャネルで使用するクロックの同期をとる際に、PLL回路から各CDR回路に供給されるクロック配線のレイアウト上の制約を無くし、ジッタの発生の少ない半導体集積回路を提供する。

【解決手段】半導体集積回路は、位相周波数比較回路とチャージポンプとループフィルタと発振回路とを有し、リファレンスクロックに同期した発振出力信号を生成するPLL回路と、発振出力信号とシリアルデータとの位相を調整する複数のCDR回路とを備え、PLL回路はループフィルタから出力された発振回路の発振周波数を制御する制御電圧をディジタルコードに変換し、このディジタルコードをこれら複数のCDR回路に分配する。

(もっと読む)

送信装置

【課題】送信状態に応じて所望のC/NとなるようにVCOの動作電流を制御することで低消費電力化を実現する。

【解決手段】PLL112が、VCO109の発振信号118Sと基準信号115Sとを比較してVCO109の発振周波数を所望の周波数に制御し、VCO109の出力信号を分周器105〜108で分周した後、変調回路101〜104が、分周された信号を変調信号に変換して送信している。このとき、動作電流制御部111が、変調回路101〜104から送信される変調信号の送信状態(つまり、送信電力、送信周波数、送信周波数の帯域など)に応じてVCO109に流れる動作電流を制御している。つまり、動作電流制御部111は、VCO109のC/Nが最適になるようVCO109の動作電流を制御して消費電流を低減している。

(もっと読む)

電源補償電圧および電流源

【課題】電源補償電圧または電流を供給する装置および方法を提供する。

【解決手段】電源補償電流および電圧源は、バンドギャップ基準電圧およびスケールされた電源電圧に接続された差動増幅器106を利用する。電源が変動すると、差動増幅器が安定した補償出力を調整する。出力は補償電圧でも電流でもよい。さらに、差動増幅器から複数の電流および電圧が参照されてもよい。安定した補償出力は、外部回路のための基準バイアスとして供給されてもよい。さらに、補償出力は、電圧制御発振器に供給されてもよい。電源補償電圧および電流源は、電源電圧が第1および第2の抵抗器102に跨って分配される、基準ノード122で第2の抵抗器と直列に接続された第1の抵抗器と、電圧基準電源104と、第1および第2の電圧入力および補償出力を有し、前記第1の入力が前記基準ノードに接続され、前記第2の入力が前記電圧基準電源に接続される差動増幅器と、を備える。

(もっと読む)

ルビジウムランプ励振回路

【課題】ランプ励振器でルビジウムランプを点灯するためのスパーク発生回路にはトランスなど大型部品が含まれ、原子発ランプ励振器の小型化、低価格化が困難である。また、ランプ励振器の発振回路におけるブロッキング振動がランプ励振器の動作を不安定にする。

【解決手段】ランプ励振器100のルビジウムランプLP1に巻かれた励振コイルL1のHot Endの面と前記ルビジウムランプLP1の発光面とが一致するように、且つ、励振コイルL1の巻き線を発光部の全域に亘るように巻き、さらにその巻き線はチップ部LP1aには施さないように構成するとともに、前記ランプ励振器のLC発振回路13に供給する前記ルビジウムランプLP1点灯後の直流電源電圧を、ランプ点灯検出回路の検出信号に基づいてリレーRL1の接点を開放して抵抗R5を介することによって、点灯させるための直流電源電圧Vccより低減して供給するように構成する。

(もっと読む)

位相同期ループ回路及びそのセルフバイアス方法

【課題】工程変化に鈍感なセルフバイアス位相同期ループ回路及びそのセルフバイアス方法を提供する。

【解決手段】第1演算増幅器は、ループフィルタキャパシタの電圧を増幅して出力し、レギュレータとして機能する第2演算増幅器は、第1演算増幅器の出力電圧をさらに増幅して出力する。第2演算増幅器の出力電圧は、電圧制御発振器の制御電圧として使われる。バイアス回路は、第2演算増幅器の出力電圧に応答して、NMOSトランジスタによって第1バイアス電流を発生し、PMOSトランジスタによって第2バイアス電流を発生し、第1バイアス電流と第2バイアス電流とを加算して第3バイアス電流を発生する。そして、第1バイアス電流は、主電荷ポンプ回路及び補助電荷ポンプ回路のバイアス電流として提供され、第3バイアス電流は、第1演算増幅器のバイアス電流として提供される。

(もっと読む)

周波数シンセサイザおよび無線通信システム

【課題】低消費電力の周波数シンセサイザおよび無線通信システムを提供すること。

【解決手段】制御回路を設けて、チャージポンプが作動する可能性のある時間をFref信号a、Load信号b、ロック検出信号c、基準信号dの中から所望の信号を用いて判断し、その時間のみチャージポンプに定電流もしくは定電圧を供給する電源回路を作動させ、それ以外の時間では電源回路を停止させるよう構成し、また、ロック後に外的および内的要因で電圧制御発振器の発振周波数が変動し、電源回路が停止している時間中にチャージポンプを作動させる信号が入力された場合、電源回路をある一定の時間だけ連続的に作動させるよう構成する。

(もっと読む)

PLL回路及びそれを備えた半導体装置

【課題】PLL回路に信号が供給されてから任意の周波数を生成するまでの時間を短縮することを目的とする。そして、安定した動作が実現できるPLL回路及びそれを搭載した半導体装置を提供することを目的とする。

【解決手段】PLL回路は、位相比較器11、ループフィルタ(LF)12、電圧制御発振器(VCO)13及び分周器14を有している。位相比較器11は、外部から入力される信号Fsと分周器14から入力される信号Fo/Nとの位相を比較する。ループフィルタ12は、位相比較器11から供給される信号から交流成分を取り除いた信号Vinを生成する。電圧制御発振器13は、ループ・フィルタ12から入力される信号Vinに基づき信号Foを出力する。分周器14は、電圧制御発振器13から出力される信号Foを、N分の1に分周した信号Fo/Nに変換して位相比較器11に出力する。

(もっと読む)

1 - 20 / 29

[ Back to top ]