Fターム[5J106HH01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 制御量 (1,632) | 周波数 (367)

Fターム[5J106HH01]に分類される特許

361 - 367 / 367

移動体通信システムにおける移動局の基地局との周波数同期のための方法及び装置

移動体通信システムにおいて移動局を基地局に同期させる方法において、基準周波数発振器が再調整される。簡単な構成の安価な基準周波数発振器の使用を可能とするため、移動局の温度変化及びその位置の変化に起因する周波数変化が個別に判定/又は予測される。周波数変化が大きいときに、移動局は、周波数変化が小さいときよりも頻繁に基地局と同期化される。  (もっと読む)

(もっと読む)

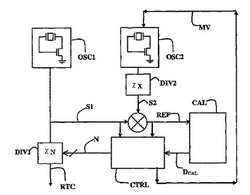

タイムベース用のレイアウト

【課題】シリコン共振器におけるように必ずしも温度安定性を必要としない周波数を有し、しかも周囲の熱的条件に係わらずに正確で低コストのタイムベースを得るために使用されることのできる共振器に基づいたレイアウトを提供すること

【解決手段】二つの発振器を含むタイムベースであって、その一つは、他方よりも低い周波数を有し、後者は断続的にスタンバイモードにセットされ、二つの発振器間の周波数差により第1安定時間基準(REF)、最も低い周波数を有する発振器の周波数を分周することにより得られる第2永久的時間基準(RTC)、及び、第1安定時間基準(REF)により決定される時間間隔の間に第1発振器(OSC1)により計数されるパルスに依存する除算因子を発生する。

(もっと読む)

半導体集積回路

【課題】制御電圧対発振周波数特性が調整可能なVCOを含む半導体集積回路を提供する。

【解決手段】この半導体集積回路は、リング状に直列に接続された複数のインバータと、バイアス電圧VBP1に従って電源電位VDDから複数のインバータに向けてそれぞれ電源電流を流す第1群のPチャネルトランジスタQP11等と、バイアス電圧VBN1に従って複数のインバータから電源電位VSSに向けてそれぞれ電源電流を流す第1群のNチャネルトランジスタQN11等と、バイアス電圧VBP2に従って電源電位VDDから複数のインバータに向けてそれぞれ電源電流を流す第2群のPチャネルトランジスタQP21等と、バイアス電圧VBN2に従って複数のインバータから電源電位VSSに向けてそれぞれ電源電流を流す第2群のNチャネルトランジスタQN21等とを具備する。

(もっと読む)

半導体集積回路

【課題】 高い周波数範囲と低い周波数範囲との広い範囲においてそれぞれ良好な特性を得ることの可能なPLL回路を提供する。

【解決手段】 制御電圧Vcに応じた周波数で発振動作する電圧制御発振器31を有し、発振信号を分周した比較信号φcompと基準クロックφinとの位相比較を行って、該位相比較の結果を制御電圧Vcにフィードバックさせることで基準クロックφinと発振信号φoutとを同期させるPLL回路において、電圧制御発振器31に、制御電圧Vcを制御電流Icに変換する電圧電流変換回路311と、制御電圧にほとんど依存しない補助電流Isを制御電流Icに付加する補助電流付加回路314と、制御電流Icの大きさに応じた周波数で発振動作する周波数可変発振器162と、制御電圧Vcの値に基づき補助電流付加回路314の動作状態のオン・オフを切り換える制御手段32とを設けた。

(もっと読む)

電圧制御発振器の自走周波数の自動調整機能を有する位相ロックループ回路

【課題】 高度の安定性を有する基準クロック信号を発生するための回路を必要とせず、従って、動作安定性がそのような回路の安定性によって影響されることのない、電圧制御発振器(VCO)の自走周波数の自動調整機能を有するPLL回路を提供する。

【解決手段】 PLL回路20では、位相比較器26の比較結果信号が所定レベルにある期間中にVCO22が出力するパルス信号のパルス数をカウントし、そのカウント値に基づいて、マイクロコンピュータ32がディジタルデータを更新する。DAC36がそのディジタルデータに対応したアナログ信号を発生する。このアナログ信号と、位相比較器の比較結果信号をローパスフィルタ28で平滑化した信号とを、結合器30で加え合わせ、その加え合わせた信号をVCOの周波数制御信号とすることで、VCOの自走周波数が自動調整されるようにした。

(もっと読む)

PLL回路

【課題】 従来よりも回路規模の小さい簡単な回路構成で、VCOのゲインを高くせずに広い出力周波数帯域を有することによって外来ノイズの影響を受けにくいPLL回路を得る。

【解決手段】 所望の出力周波数Foの信号を第1VCO14から出力する主PLL回路部2と、該主PLL回路部2の第1VCO14の発振周波数を制御する第1制御電圧VCOIN1及び第2制御電圧VCOIN2の内、第2制御電圧VCOIN2を出力周波数Foに応じて自動調整する副PLL回路部3といった2つのPLL回路を備えると共に、副PLL回路部3の発振周波数を設定する第2プログラマブルカウンタ21の分周比を、第1プログラマブルカウンタ11に設定された分周比に応じて設定するようにした。

(もっと読む)

発振器及びそれを用いた位相同期ループ回路

制御信号に信号を加えることによって周波数を制御することが可能な変調機能を備えた発振器(1083)、及びそれを用いたPLL回路(108A)において、発振器は、インバータ又はバッファ及び制御信号により遅延値が制御されるカスケード接続された複数の遅延段(201〜203)を有し、反転位相により閉ループを形成するリング発振器(200)からなり、複数の遅延段の一部において制御信号に変調信号を加えることにより発振周波数を変調する変調機能を備える。 (もっと読む)

361 - 367 / 367

[ Back to top ]