Fターム[5J106HH01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 制御量 (1,632) | 周波数 (367)

Fターム[5J106HH01]に分類される特許

201 - 220 / 367

クロックデータ再生回路

【課題】高速シリアルデータ転送の受信回路において、低消費電力モードから通常モードに復帰する際の復帰時間を短縮する。

【解決手段】シリアルデータ転送路から転送される同期用クロックを含むシリアルデータから同期用クロック及びデータを再生するクロックデータ再生回路であって、シリアルデータ及び基準クロックを電力モードに応じて選択してクロックデータ再生回路に供給する選択回路を具備する。

(もっと読む)

デジタル周波数検出器及びこれを用いたデジタルPLL

【課題】デジタルPLLや周波数シンセサイザなどに使用されるデジタル周波数検出器及びこれを用いたデジタルPLLを提供する。

【解決手段】本デジタル周波数検出器は、第1周波数のハイレベル区間に動作する第1リングオシレータを利用して、第1周波数をデジタル形式の第1周波数情報として出力する第1変換部と、第2周波数のハイレベル区間に動作する第2リングオシレータを利用して、第2周波数をデジタル形式の第2周波数情報として出力する第2変換部と、第1周波数情報及び第2周波数情報の比を演算し、第1周波数に対するデジタル周波数を出力する演算部と、を含む。

(もっと読む)

電圧制御発振器及びこれを用いた位相同期回路

【課題】インバータセルを構成するMOSトランジスタが飽和領域のみならず、線形領域で動作する場合にも位相雑音を低減する。

【解決手段】ダミーインバータセル110からの信号と、基準信号との電位差を増幅した増幅信号を出力する演算増幅器120と;第2MOSトランジスタ102に接続され、増幅信号を受ける第1MOSトランジスタ101と、インバータ入力部及びインバータ出力部として機能する第2MOSトランジスタ102及び第3MOSトランジスタ103と、第3MOSトランジスタ103に接続され、発振信号の周波数を制御するための制御信号を受ける第4MOSトランジスタ104とを含むインバータセル100を環状に接続したリング・オシレータと;インバータセル100と同一の構造を備え、インバータ出力部がインバータ入力部に短絡されたダミーインバータ110と;を具備する。

(もっと読む)

発振周波数制御方法及び発振器

【課題】温度によって変化する発振周波数を、応答性良く、正確に、所定の周波数に調整することができる発振周波数の制御方法及び発振器を提供する。

【解決手段】本発明の発振周波数制御方法は、発振周波数及び出力信号の振幅が温度に依存して変化し、所定の発振周波数制御信号を用いて発振周波数の変更が可能な発振器の発振周波数制御方法であって、振幅を測定する工程と、振幅に基づき発振周波数制御信号を制御し、発振周波数を変更する工程を備える。また、本発明の発振器は、発振周波数及び出力信号の振幅が温度に依存して変化し、所定の発振周波数制御信号を用いて発振周波数の変更が可能な発振器であって、振幅を測定する振幅測定部と、振幅に基づき発振周波数制御信号を制御し、発振周波数を変更する温度補償部を備える。

(もっと読む)

位相ロック回路

【課題】位相ロック回路において、電圧制御発振回路や分周回路の性能が設計時よりばらついた場合であっても、電圧制御発振回路が出力する高速クロックを分周回路で良好に分周できるようにして、不良品を低減する。

【解決手段】第1の分周回路4に加えて、この分周回路4よりも動作速度の遅い第2の分周回路5を備える。前記2つの分周回路4、5で分周されたクロックの周波数同士を周波数比較回路6で比較し、第2の分周回路5の分周クロックの周波数よりも第1の分周回路4の分周クロックの周波数の方が速い場合には、VCO発振抑制回路7が電圧制御発振回路3出力クロックFoutの発振周波数を抑制する。

(もっと読む)

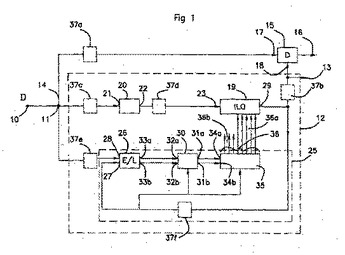

外部制御を必要としないデジタル位相ロックによるクロック抽出装置

本発明は、注入ロック発振器(19)と、デジタル位相検出器(26)を有する位相制御ループ(25)とを備えた、ベースバンドシリアル信号からクロックを抽出する装置に関する。発振器(19)はその周波数の値を制御するデジタル制御入力部(24)を備え、位相制御ループ(25)は、デジタル位相検出器(26)から供給されるデジタル信号の相対値を累算し、発振器(19)用のデジタル形態の制御信号を渡す、カウント回路(30、35)を備える。  (もっと読む)

(もっと読む)

搬送波同期回路および搬送波同期方法

【課題】局部発振器の周波数ドリフトが大きい場合、及び、周波数同期部の周波数検出精度があまり高くない場合においても、伝送品質を劣化させることなく、高速かつ安定的に搬送波との同期を確立する。

【解決手段】位相同期部52は、周波数同期部51による周波数同期処理後の残留周波数誤差Δf'を検出し、周波数同期部51に帰還させる。周波数同期部51は、収束判定回路82からの収束ステートを監視し、残留周波数誤差Δf'が収束したタイミングにおいて、位相同期部52からの残留周波数誤差Δf'に対する周波数引き込みを行う。本発明は、例えば、無線デジタル通信などの搬送波同期回路に適用できる。

(もっと読む)

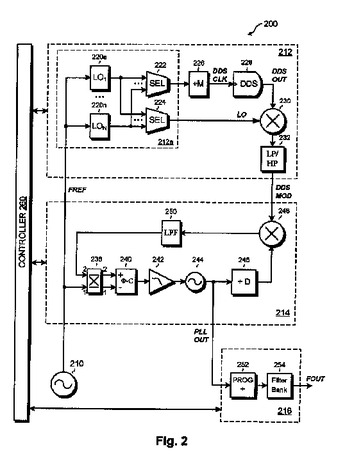

コスト的に有効な低ノイズの単一ループシンセサイザー

低コストで低位相ノイズのマイクロ波シンセサイザーは、DDS変調回路と位相ロックループを含む。DDS変調回路はDDSの出力を高周波数に変調する。位相ロックループはDDS出力をダウンコンバートし、ダウンコンバート信号を比較的低周波数の固定されたリファレンスにロックする。  (もっと読む)

(もっと読む)

CDR回路

【課題】異なる複数のビットレートの入力データを再生できるようにしたCDR回路を提供する。

【解決手段】参照クロックCKの周波数に対応した制御信号Vrにより第2の電圧制御発振器3の発振周波数が決定されるPLL回路と、制御信号Vrにより第2の電圧制御発振器3の発振周波数と同じ周波数で再生クロックCLK1を発振し且つ入力データのタイミングに合わせて該再生クロックCLK1の発振位相が調整される第1の電圧制御発振器1と、入力データを再生クロックCLK1によりリタイミングするフリップフロップ回路2とを備えるCDR回路において、PLL回路に、分周比の異なる2個の分周器7A,7Bと、該分周器7A,7Bの内の1つを選択するセレクタ8とを備えさせる。

(もっと読む)

周波数シンセサイザ及びこれを用いた無線通信装置

【課題】インダクタの使用による面積増大や、製造ばらつきによる歩留まり低下を防ぎつつ、動作周波数範囲を拡大する。

【解決手段】制御電圧によって制御される周波数で発振して発振信号を出力する電圧制御発振器106と;発振信号を分周して第1の分周信号を出力する、自走周波数が制御可能なプリスケーラ107と;第1の分周信号を分周して第2の分周信号を出力するプログラマブル・ディバイダ102と;第2の分周信号の位相と基準クロック信号の位相を比較して位相差に対応する信号を出力する位相比較器108を含み、位相差に対応して制御電圧を生成する制御電圧生成部と;第2の分周信号の周波数と基準クロック信号の周波数を比較して周波数差に対応した信号を出力する周波数比較器103と;周波数差に対応した信号に従って周波数差を最小化するように自走周波数を制御する制御部109と;を具備する。

(もっと読む)

データ通信システムの高速パワーアップ

データ通信システムは、第1のクロック発生回路を有する送信機と、第2のクロック発生回路を有する受信機とを具えている。第1及び第2のクロック発生回路のうちの少なくとも一方の特定のクロック発生回路が順次のデータバースト間でパワーダウンされるようになっている。このデータ通信システムは、前記特定のクロック発生回路がパワーダウンした際にこのデータ通信システムを実用使用状態に起動するのを促進させる。このデータ通信システムは、起動時に前記特定のクロック発生回路の動作量を予め決定した値にプリセットする。  (もっと読む)

(もっと読む)

無線受信回路および入力妨害波低減回路

【課題】広い周波数領域に渡って妨害波を低減できる入力妨害波低減回路の小型化、およびそのような入力妨害波低減回路を備える無線受信回路の小型化を図る。

【解決手段】受信信号は、トランジスタQ1のゲートに与えられる。トランジスタQ1はトランジスタQA〜QDに接続され、トランジスタQ1、QA〜QDにより4個の増幅器が構成される。トランジスタQA〜QDには、それぞれ調整回路13A〜13Dが接続されている。調整回路13A〜13Dは、LC共振回路であり、その共振周波数は調整信号および微調整信号により調整される。選択信号は、4個の増幅器の中から使用すべき増幅器を選択する。選択された増幅器の利得周波数は、対応する調整回路(13A〜13D)の共振周波数に応じて決まる。選択された増幅器により増幅された信号が出力される。

(もっと読む)

クロック発生装置

【課題】PLL回路を使用し、より幅広い環境変動に適応して周波数を一定値にロックすることのできるクロック発生装置を得る。

【解決手段】クロック発生装置200は、基本的に同一構成で共にLC型VCOを備えた第1および第2のPLL回路201、202を備えている。マスタ側の第1のPLL回路201の第1のVCO2241に加わる第1の制御電圧2281は基準電圧検出回路212で3つの固定値と比較され、その結果に応じて第2のPLL回路202の容量スイッチ247、257の値を調整しておいて、出力セレクタ207で第1のPLL回路201から第2のPLL回路202にクロックの選択を切り替える。

(もっと読む)

シリアルインターフェース回路

【課題】 回路規模を小さく抑えたまま、動作確認テストを確実に行なうことができるシリアルインターフェース回路を提供する。

【解決手段】 テストコントローラ13から擬似ランダムデータを送信用PLL回路12に出力して、送信用PLL回路12でランダムなジッタを含んだクロックを生成し、シリアライザ11でこのクロックを用いてパラレルの送信データTransmitDataをシリアル送信データSOに変換し、シリアルループバック回路30およびマルチプレクサ24を経由してクロック・データリカバリ回路22に入力する。クロック・データリカバリ回路22では、そのシリアル送信データSOを、受信用PLL回路21からのいずれかのクロックで取り込み、デシリアライザ23でパラレルデータRecoveredDataを生成する。

(もっと読む)

移動無線機

【課題】基地局を介した通信と、基地局を介さずに直接、他の移動無線機と通信をおこなう二つのモードにより通信する移動無線機において、直接通信のときであっても、環境の温度変化や発信器の経年変化によらず、安定して送信周波数を生成する

【解決手段】基地局の圏内で通信では、AFC部は、受信周波数に基づいて、電圧制御発信器に印加する電圧制御値を調整する。中央処理装置は、その電圧制御値と温度センサーによって検知される温度を対にしてメモリに記憶する。基地局の圏外で他の無線機と通信するときには、中央処理装置は、メモリに記憶された電圧制御値と温度センサーのデータと、現在検知されている温度により、最適な電圧制御値を計算し、その電圧制御値に従って電圧制御発信器に制御電圧を印加して、基準周波数を生成し、それによる送信周波数により、他の移動無線機と通信する。

(もっと読む)

PLL回路

【課題】入力信号の断、回復状態でも出力の周波数変動を抑制し、周波数精度を維持するPLL回路の提供。

【解決手段】入力を所望周波数に分周する第1分周手段3と、電圧制御発振器7出力を所望周波数に分周する第2分周手段8と、前記第1分周手段3出力と前記第2分周手段出力8間の第1位相比較手段4と、前記第1分周手段3出力と前記第2分周手段8出力の反転の一方の第1選択手段11と、前記第2分周手段8出力と前記第1選択手段11出力間の第2位相比較手段12と、前記第1位相比較手段4出力と、前記第2位相比較手段12出力の一方の第2選択手段6と、入力信号監視手段9と、前記入力信号監視手段9からの監視結果に対して一定時間のタイミングを生成するタイミング生成手段10と、を備え、前記第1選択手段11及び前記第2選択手段6は、前記タイミング生成手段10からの信号状態に従って選択する。

(もっと読む)

デジタル制御発振器、このデジタル制御発振器を備えた位相同期ループ及び通信機

【課題】スプリアスが生じにくい。

【解決手段】ADCから入力されたnビットのデジタル信号は、mビットが整数部41、且つ、n−mビットがデジタル制御値時間変化部43に入力される。そして、デジタル制御値時間変化部43から時間的に変化するデジタル制御値が小数部42に入力される。デジタル制御発振器4は、整数部41によってステップ周波数刻みで発振周波数を変化させる。また、小数部42によってステップ周波数よりも小さな周波数刻みで発振周波数を変化させる。このとき、小数部42によって変化させることができる周波数は、ステップ周波数よりも大きい。

(もっと読む)

カウンタ信号生成装置、クロック信号再構成装置及び通信装置

【課題】IPタイプなどのパケット交換ネットワークに接続されるリモート通信装置におけるPLLのロック又は同期を高速化する。

【解決手段】クロック信号を表すカウンタ信号を生成する装置であって、リファレンスクロック周波数に従ってクロック信号を提供するクロック手段と、提供クロック信号の個数を表す周期的なランプの信号を提供するカウンタと、カウンタ信号を構成するため、選択されたサンプリング周波数によりランプ信号をサンプリングするサンプラとを有し、クロック手段は、リファレンスクロック周波数と異なる少なくとも1つの他の周波数のクロック信号を提供するよう構成し、さらに受信したコマンドに従って提供可能なクロック周波数の1つを選択し、選択されたクロック周波数とリファレンスクロック周波数との間のレシオの値と乗算されたリファレンスサンプリング周波数に等しいサンプリング周波数を規定する制御手段を有する装置を提供する。

(もっと読む)

PLLシンセサイザ

【課題】 高速起動性、低消費電力性、定常状態における低スプリアス性を同時に満足し、かつ性能を左右するパラメータを最適化する。

【解決手段】 分数分周モードと整数分周モードとを切り換える構成であり、PLL起動時から収束に至るまでの収束時間Tacq を設定し、その収束時間Tacq が、制動係数ζ、固有周波数ωn 、初期周波数差Ω0 に対して、

Tacq =Ω02/(2ζωn3) …(a)

で表されるときに、制動係数ζを0.5 ≦ζ≦1とし、PLL起動時に固有周波数ωn が (a)式を満たすように分数分周モードの分周比を設定し、収束したと見なすタイミングTs(=Tacq)で、ループフィルタを切り換えることなく、整数分周モードの分周比に切り換える構成である。

(もっと読む)

PLL制御システム

【課題】VCOのバンド毎にチャージポンプ電流を設定しても、ループ帯域のばらつきを抑圧することができるPLL制御システムを提供する。

【解決手段】PLL制御システムにおいて、TCXO8と、分周器B8と、複数のバンドを有するVCO4と、分周器A5と、分周器A5と分周器B8の2つの分周信号を比較する位相比較器6と、VCO4への電圧を出力するループフィルタ2と、位相比較器6の比較信号に応じてループフィルタ2へ電流を供給するチャージポンプ回路3と、ループフィルタ2に対してプリチャージするプリチャージ回路1と、制御部9とを備え、制御部9は、プリチャージ回路1によるプリチャージを、複数のバンドに対応して予め設定された離散的な情報に基づいて離散的に制御する。

(もっと読む)

201 - 220 / 367

[ Back to top ]