Fターム[5J106HH01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 制御量 (1,632) | 周波数 (367)

Fターム[5J106HH01]に分類される特許

141 - 160 / 367

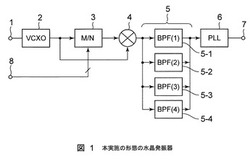

水晶発振回路

【課題】 複数の異なる周波数信号を出力可能で、消費電力を低減し、構造が簡易で小型化できる水晶発振回路を提供する。

【解決手段】 電圧制御水晶発振器(VCXO)2からの出力を分周比に応じて分周器3で分周し、分周された信号とVCXO2から出力された信号を合成器4で合成し、予め分周比に応じて通過帯域が定められた複数のBPF5に出力し、該当するBPFのみが特定の周波数帯域の信号を通過させ、PLL6で位相制御が為されて、所望の周波数信号を出力する水晶発振回路である。

(もっと読む)

周波数補正システム及び受信機

【課題】製品コストの増大を抑え、水晶発振器の動作のばらつきを防止することが可能な周波数補正システム及び受信機を提供することを目的とする。

【解決手段】誤差読出しタイミング制御部31で設定される読出しタイミングに基づいて、復調部設定レジスタ26から周波数誤差ΔIFをΔIF抽出部34に読み込み、記憶部32に記憶される現在受信中の受信信号の周波数RF及び周波数誤差ΔIFなどに基づいて、水晶発振器6の経年変化による水晶発振器6の発振信号の周波数誤差Δfを算出し、周波数誤差Δfが閾値以上であると判断した場合、現在受信している受信信号のチャンネルに対応する周波数誤差ΔIFを記憶部33から読み出し、その周波数誤差ΔIFに基づいて、チューナ設定レジスタ16及び復調部設定レジスタ26に現在書き込まれている設定値R、Nを更新する。

(もっと読む)

原子発振器

【課題】ガスセルを効率よく均一に加熱することにより低消費エネルギーで高精度な基準周波数を得ることが可能な原子発振器を提供する。

【解決手段】原子発振器の物理部としての物理パッケージ1は、ガスセル10と、赤外線ヒータ55と、ガスセル10および赤外線ヒータ55を包囲するように設けられた断面略楕円形状の包囲体90とにより構成されている。包囲体90は、楕円柱状の保持部材92と、この保持部材92の側面に設けられた赤外線反射膜95とからなる。保持部材92の断面形状である楕円の軌道上に形成された赤外線反射膜95の任意の点を反射点とした2焦点にガスセル10と赤外線ヒータ55とが配置されて保持されている。ガスセル10内には、アルカリ金属を気化させた多数の金属原子が、CO2などの赤外活性振動モードを有する分子を含む多数の緩衝ガスの分子とともに封入されている。

(もっと読む)

クロック及びデータ復元回路

【課題】入力データ論理判定用クロックとして、周波数の安定したクロックを得ることができ、しかも、消費電力を低減することができるCDR回路を提供する。

【解決手段】入力データの論理判定に使用する内部クロックRCKの発生源として電圧制御発振器15を設ける。電圧制御発振器15は、CMOSインバータをリング接続して構成し、常に電流を消費することがないものとする。両エッジ検出部13は、PLL12内の電圧制御発振器21の出力クロックVCO_CKの遷移タイミングを検出し、電圧制御発振器15の発振周波数がPLL12内の電圧制御発振器21の発振周波数と同一となるように電圧制御発振器15を制御する。

(もっと読む)

受信側デバイスの出力クロック周波数の補正回路

データ(16)およびタイムスタンプ要素(18)を受信する受信側デバイス(13)の出力クロックの周波数を補正するための出力クロック補正回路(14)は、出力クロックフィードバックループ(20)、FIFOバッファ(22)およびタイムスタンプアジャスタ(24)を含む。出力クロックフィードバックループ(20)は、タイムスタンプ要素(18)に基づいて出力クロックの位相および/または周波数を調節する。FIFOバッファ(22)は、一時的にデータを格納する。タイムスタンプアジャスタ(24)は、FIFOバッファの状態に基づいてタイムスタンプ要素を選択的に調節する。一実施形態では、前記状態が、FIFOバッファ内の実データレベルに少なくとも部分的に基づくものとなる。別の実施形態では、FIFOバッファ(22)が目標データレベル範囲を有し、FIFOバッファ内の実データレベルがこの範囲外となったときに、タイムスタンプ要素が調節される。 (もっと読む)

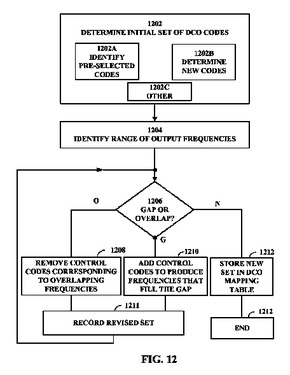

デジタル制御発振器のためのダイナミック較正技法

デジタル制御発振器(DCO)を較正するための技法を開示する。本開示の一態様では、DCOを動作させるための制御コードの初期セットを判断する。初期セットから生成された出力周波数レンジを識別する。周波数レンジにおけるギャップまたはオーバーラップインスタンスを識別する。オーバーラップの場合、修正されたセットを確立するためにオーバーラップインスタンスに対応する制御コードを初期セットから除去する。ギャップの場合、ギャップを充填する周波数値を生成するために、制御コードを初期セットに追加する。同じことを実行するための装置も開示する。  (もっと読む)

(もっと読む)

デジタル制御発振器及びこれを用いた位相同期回路

【課題】発振周波数を線形に近くかつきめ細やかに制御可能なデジタル制御発振器を提供する。

【解決手段】正相発振信号を出力する正端子213と、逆相発振信号を出力する負端子214と、センタータップ210とを有し、正端子とセンタータップとの間の任意の位置に第1の接点211を備え、負端子とセンタータップとの間の第1の接点に対応する位置に第2の接点212を備える差動インダクタ200と、正端子と負端子との間に接続され、第1のデジタル制御コードによってキャパシタンスを2値に変化させる第1の可変キャパシタを複数含む第1の可変キャパシタバンク220と、第1の接点と第2の接点との間に接続され、第2のデジタル制御コードによってキャパシタンスを2値に変化させる第2の可変キャパシタを複数含む第2の可変キャパシタバンク240と、正端子と負端子との間に接続される負性抵抗230とを具備する

(もっと読む)

周波数変調機能付きクロック生成回路

【課題】良好なスペクトラム拡散効果を有し、ノイズの発生が少なく周辺回路や電子部品の誤動作を低減することができる周波数変調機能付きクロック生成回路を提供する。

【解決手段】クロック生成回路1は、帰還用分周器17を有し、周波数変調されたクロックを出力するPLL回路10と、帰還用分周器17から所定の周波数のみ取り出しPLL回路10に入力するバンドパスフィルタ20と、三角波を生成する三角波生成回路40とを有し、バンドパスフィルタ20は、サイン波生成器としても機能し、所定のタイミングでサイン波を生成して三角波と合成して帰還用分周器17の分周比を変化させる。

(もっと読む)

電圧制御発振装置

【課題】高いC/N及び周波数安定度を確保できると共に、周波数可変幅を広くしても帯域外の不要信号の漏れ出しを抑制でき、かつ同時にインピーダンスマッチングもとることができるようにすること。

【解決手段】この電圧制御発振装置は、制御電圧信号に応じて発振周波数が制御される電圧制御発振回路1と、電圧制御発振回路に供給する制御電圧信号を生成するPLL回路2と、電圧制御発振回路1の出力する発振信号を逓倍する逓倍回路3と、逓倍回路3の出力する逓倍信号のうち所定逓倍数の信号を通過させる通過帯域と逓倍回路3に入力した発振信号と同一周波数をトラップするトラップ周波数とが設定された帯域通過フィルタ兼トラップ回路4とを備える。制御電圧信号を分岐して段間結合兼トラップ回路15へ入力し、発振周波数に同期させて段間結合兼トラップ回路15の通過帯域及びトラップ周波数を可変させると共に段間結合量を調整する。

(もっと読む)

PLL回路

【課題】ディジタル回路で構成されるADPLLにおいて、位相差0近傍における位相差検出を改善することができる技術を提供する。

【解決手段】基準信号VREFフィードバック信号VDIVとの位相及び周波数を比較するPFDと、PFDの出力をディジタル値に変換するTDCと、TDCの出力から高周波雑音成分を除去するDLFと、DLFの出力に基づいて制御されるDCOと、DCOの出力を分周しフィードバック信号VDIVを出力するDIVによりフィードバックループが構成される。フィードバックループのいずれかの箇所にオフセット値が加算され、フィードバック信号VDIVの位相が制御され、ロック時にもTDCに0ではない値が入力される。

(もっと読む)

VCOのキャパシタバンクのトリミングとキャリブレーション

技法は、電圧制御発振器(VCO)で使用されるキャパシタバンクに関連するキャパシタンスをトリミングするために開示される。実施例では、キャパシタンスはそれぞれ複数の構成要素のキャパシタンスへサブ分割される。実施例では、キャパシタンスはそれぞれ複数の構成要素のキャパシタンスへサブ分割される。構成要素のキャパシタンスは、キャパシタバンクのステップのサイズをトリミングするために選択的にイネーブルされ、またはディスイネーブルされ得る。さらなる技法は、キャパシタバンクについてステップのサイズの誤差を最小化するためにトリミング可能なキャパシタンスをキャリブレートするために開示される。  (もっと読む)

(もっと読む)

オーディオ参照クロックを生成可能な受信装置

【課題】PLL回路に入力されるリファレンス周波数を高くすることができる受信装置を提供する。

【解決手段】受信装置1は、ピクセルクロックを1/CTSで分周して、第1の信号として出力する第1の分周器11と、商CTSquoの値に対応する周期をN−CTSremに対応する回数分第1の信号の周期内に含み、かつ、CTSquo+1に対応する周期をCTSremに対応する回数分第1の信号の周期内に含む第2の信号を、ピクセルクロックの周期を制御することによって出力する周期制御部21と、周期制御部21から出力される第2の信号によって得られるリファレンス信号に基づいて、所望の周波数にロックされた信号を出力するPLL回路31とを備える。周期制御部21は、CTSremの和を随時計算し、当該和がしきい値N−1をオーバーフローするときに応じて、第2の信号の周期を制御する。

(もっと読む)

無線装置

【課題】本発明は、基準発振部から出力される基準信号を用いて、演算部の設定で無線通信の送受信周波数を生成する無線通信機器において、基準発振部の温度特性を補正するためのデータを効率的かつ、高精度な補正を実現する構成を提供することを目的とする。

【解決手段】本発明の無線通信機器300は、送信処理を行う際に、温度検出部305で基準発振部303の雰囲気温度を検出し、該当の温度に対する第1補正データを外部記憶部304より読み出した上で、演算設定部311で、内部記憶部312に記憶されている第2補正データ、基準チャネル設定データを用い送信周波数を演算し、高周波部301から、あらかじめ決められたデータを変調し送信をおこなう。

(もっと読む)

デジタル位相ロックループ(DPLL)における電力消費を制御するシステム及び方法

【解決手段】相異なる周波数クロックの組から選択された参照クロックを生成するように適合されたプログラマブル周波数デバイスを備えた装置であって、プログラマブル周波数デバイスは更に、相異なる周波数クロック間での切り替えの際に、参照クロックのトリガエッジの同じ時間的関係を維持するように適合される。装置は更に、入力信号と出力信号との間の所定の位相関係を確立するために選択された参照クロックを使用する、デジタルPLL(DPLL)のような位相ロックループを備える。相異なる周波数クロック間の切り替えの際に参照信号の同じ時間的関係を実質的に維持することで、参照クロックが変化しても、位相ロックループ(PLL)の連続且つ有効な動作は、大きくはディスターブされない。これは、装置の電力消費を制御するために使用され得る。 (もっと読む)

パルス発生回路及びパルス発生回路を備えた電子機器

【課題】PVTに依存せずに安定した周波数を出力する。

【解決手段】出力する第1の出力信号Vf1の周波数を第1の制御電圧VC1で制御する第1の電圧制御発振器11と、第1の出力信号Vf1及び基準信号CLKに基づき第1の出力信号Vf1の周波数を一定に維持する第1の制御電圧VC1を生成する制御電圧生成部13と、を含む位相同期回路10と、出力する第2の出力信号Vf2の周波数を第2の制御電圧VC2で制御する第2の電圧制御発振器20と、第1の制御電圧VC1に基づき第2の出力信号Vf2の周波数を一定に維持する第2の制御電圧VC2を生成する制御電圧変換部30と、を含むパルス発生回路1。

(もっと読む)

温度補償のための補助バラクタ

電圧制御発振器(VCO)周波数に対する温度変化の影響を補償するための技法が、開示される。一実施形態においては、補助バラクタが、VCOのLCタンクに結合される。補助バラクタは、温度に伴ってVCO周波数の全体の変化を最小にする、温度依存制御電圧(Vaux)によって制御されるキャパシタンスを有する。デジタル手段とアナログ手段とを使用して制御電圧を生成するための技法が、さらに開示される。補助バラクタ(Caux)は、LCタンクの電圧制御キャパシタ(C)と直列に、または並列にのいずれかで結合されることができる。一実施形態においては、制御電圧は、絶対温度に比例した第1の電流と、温度にわたって一定の第2の電流、例えば、バンドギャップ電流、との間の差を得ることによって生成される。  (もっと読む)

(もっと読む)

電圧制御型可変周波数発振回路および信号処理回路

【課題】可変容量素子の容量可変域に応じた広い周波数可変域を確保することができる電圧制御型可変周波数発振回路を提供する。

【解決手段】コイルL1,L2および可変容量素子111,112を有する共振回路101と、負性抵抗回路102とを含む発振回路部103を備える電圧制御型可変周波数発振回路である。発振回路部103と電源電位VDDとの間に第1の抵抗301を設ける。また、発振回路部と接地電位端との間には第2の抵抗302を接続するとよい。

(もっと読む)

クロック発生機能付き装置、基準周波数等設定方法、および基準周波数等調整方法

【課題】クロックに関する設定を簡単に行う。

【解決手段】VCXOと、基準周波数とこの基準周波数のクロックをVCXOに発生させる電圧のレベルである基準レベルとを記憶するメモリと、必要な周波数のクロックを、メモリに記憶されている基準周波数および基準レベルを基準に求められる電圧をVCXOに与えて発生させるD/Aコンバータ制御部およびD/Aコンバータと、を有する装置において、下記の処理を行う。試験時レベルを適宜変化させながら、各試験時レベルに応じた電圧をVCXOに与えて試験用クロックを発生させる。試験用クロックを周波数カウンタに出力する。試験用クロックの周波数と目標周波数との差が所定の範囲内であることが周波数カウンタによって確認できたら、メモリに、この試験用クロックがVCXOによって発生された際の試験時レベルを基準レベルとして記憶させ、この試験用クロックの周波数を基準周波数として記憶させる。

(もっと読む)

半導体集積回路装置、及び、クロックデータ復元方法

【課題】 インターポレータ方式のクロックデータ復元回路において、インターポレータ回路の広帯域化を行わず、マルチレートに対応したクロックデータ復元回路を実現する。

【解決の手段】 インターポレータ回路の生成クロックを分周し、リカバリクロックを生成する。また、インターポレータ回路が生成するクロックの位相を制御するポインタは分周前のクロックを使い、その他の回路は分周後のリカバリクロックを使い動作する。

(もっと読む)

発振装置

【課題】通信機などが必要とする発振装置の発振周波数範囲の広帯域化が、簡単な構成で精度よく行えるようにする。

【解決手段】8GHzから12GHzなどの第1の周波数帯域幅の可変範囲を持つ低位相雑音な発振手段と、発振手段の発振出力を分周する周波数分周器とを備える。発振手段が出力する発振信号の周波数と、周波数分周器で分周する分周比を制御して、周波数分周器の出力周波数を、発振手段の発振周波数以下の周波数で、第1の周波数帯域幅と同じかそれ以上の周波数帯域幅で可変設定される所望の周波数とする制御を行う。

(もっと読む)

141 - 160 / 367

[ Back to top ]