Fターム[5J106HH01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 制御量 (1,632) | 周波数 (367)

Fターム[5J106HH01]に分類される特許

81 - 100 / 367

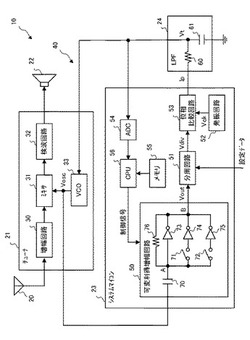

位相同期回路

【課題】ノイズが混入した場合であっても、所望の周波数で発振信号を生成することが可能な位相同期回路を提供する。

【解決手段】位相同期回路は、低域通過フィルタからの出力電圧に応じて発振回路から出力される発振信号を、制御信号に基づいた利得で増幅する可変利得増幅回路と、可変利得増幅回路からの増幅信号の位相に応じた第1の位相と、増幅信号の基準となる基準信号の第2の位相とを比較して、第1の位相と第2の位相とを一致させるための比較信号を低域通過フィルタに出力する位相比較回路と、出力電圧に基づいて、第1の位相と第2の位相とが一致しているか否かを検出する検出回路と、検出回路の検出結果に基づいて、第1の位相と第2の位相とが一致している場合、利得が所定の値となるような制御信号を生成し、第1の位相と第2の位相とが一致していない場合、利得を所定の値より増加させるような制御信号を生成する制御信号生成回路と、を備える。

(もっと読む)

通信装置

【課題】飛翔体に搭載され衛星と通信を行う通信装置において、飛翔体からの送信信号の周波数がドップラー効果により大きく変動した場合であっても、送信信号を所定の規定周波数で衛星が受信できるようにする。

【解決手段】飛翔体に搭載され衛星20と通信を行う通信装置10であって、衛星20に対し送信信号を送信する送信部5と、衛星20に対する飛翔体の相対位置、姿勢、速度に基づいて、ドップラー効果による送信信号の周波数変動量を求める周波数変動量取得部14と、衛星20から見た送信信号の周波数が規定周波数となるように、周波数変動量に基づいて、送信信号の周波数を調整する送信信号調整部13と、を備える。

(もっと読む)

クロック信号分配装置

【課題】高品質のクロック信号を分配することができるクロック信号分配装置を提供することを課題とする。

【解決手段】第1のインダクタ及び第1の容量に応じた周波数で共振して信号を発振する複数のLC共振発振器(302,303)と、第2のインダクタ及び第2の容量に応じた周波数で共振し、入力クロック信号に同期した信号を発振する注入同期型LC共振発振器(301)と、前記複数のLC共振発振器及び前記注入同期型LC共振発振器の発振ノードを接続する伝送線路(311,312)とを有することを特徴とするクロック信号分配装置が提供される。

(もっと読む)

発振器及び位相同期回路

【課題】十分に高い周波数帯域において、広帯域にわたって柔軟に発振周波数を調整すること。

【解決手段】信号線131は、電源から直流電圧Vdcが印加されると、電源に接続された始端を節とし、終端を腹とする4分の3波長の定在波を発生させる。ストリップ132−1〜132−nは、それぞれスイッチ133−1〜133−nを介してグランド層に接続されている。スイッチ133−1〜133−nは、切替制御部140による制御に従って、それぞれストリップ132−1〜132−nとグランド層との接続及び非接続を切り替える。スイッチ133−1〜133−nの接続及び非接続を切り替えることにより、擬似的に信号線131とグランド層の間の距離が調節され、伝送線路部130における実効誘電率が変化して、定在波の周波数を調整することができる。

(もっと読む)

OFDMAシステムのための2重周波数追跡ループ

無線デバイスによって受信された信号の搬送周波数とこのデバイスにとってローカルな基準信号との間の周波数誤差を修正するための方法および装置。ある幾つかの態様ではこのような方法は一般に、基準周波数を生成するLOと無線周波数(RF)位相ロックループ(PLL)とディジタルローテータとを有する受信機において信号を受信することと、上記受信された信号の搬送周波数と上記LO基準周波数との間の周波数差を推定することと、上記推定された周波数差を上記RF PLLと上記ディジタルローテータとに適用することと、を含む。  (もっと読む)

(もっと読む)

クロックデータ再生回路

【課題】VCOの発振周波数のばらつきを補償し、低ジッタで電源電圧・温度変動耐性が大きいクロックデータ再生回路を提供する。

【解決手段】再生クロックを出力する第1の発振回路と、第1の発振回路と同一周波数のクロックを出力する第2の発振回路と、第2の発振回路が出力するクロックと参照クロックを周波数比較し、その周波数誤差に応じた周波数制御信号Aで第1〜第2の発振回路の発振周波数を制御するPLL手段とを備えたクロックデータ再生回路において、第1〜第2の発振回路の回路間ばらつきによる発振周波数のずれを調整する回路間ばらつき調整信号Cを入力する端子と、周波数制御信号Aと回路間ばらつき調整信号Cを加算する加算器とを備え、第1〜第2の発振回路はそれぞれ1つの制御端子を備え、第2の発振回路の制御端子に周波数制御信号Aを入力し、第1の発振回路の制御端子に加算器の出力信号を入力する構成とする。

(もっと読む)

クロックデータ再生回路

【課題】プロセスばらつきによる発信周波数ずれを調整する。

【解決手段】入力データと周波数および位相が同期した再生クロックを出力する発振回路と、発振回路が出力する再生クロックと参照クロックを周波数比較し、その周波数誤差に応じた周波数制御信号Aで発振回路の発振周波数を制御するPLL手段とを備えたクロックデータ再生回路において、発振回路のプロセスばらつきによる発振周波数のずれを調整するプロセスばらつき調整信号Bを入力する端子を備え、発振回路は2つの制御端子を備え、その一方の制御端子に周波数制御信号Aを入力し、他方の制御端子にプロセスばらつき調整信号Bを入力する構成である。

(もっと読む)

スペクトラム拡散クロック生成器及び半導体装置

【課題】回路規模の大きなDACやアナログ変調回路を用いずに理想的な周波数特性を得ることが可能なスペクトラム拡散クロック生成器及びスペクトラム拡散クロック生成器を備えた半導体装置を提供する。

【解決手段】動作クロックを生成する電圧制御発振器と、動作クロックの位相と基準クロックの位相とを比較し比較結果により電圧制御発振器の発振の基準となる電圧を生成する帰還制御部と、動作クロックの周波数に変動を与える成分をデルタシグマ変調したパルス信号として生成する変調パルス生成部と、パルス信号の振幅を設定するレベル設定部と、帰還制御部が生成した電圧とレベル設定部によって振幅が設定されたパルス信号とを加算する加算部と、加算部の出力信号を濾波して電圧制御発振器に与える制御電圧を生成する低域パスフィルタと、を備える。

(もっと読む)

クロックデータ再生回路

【課題】複数のVCO間の発振周波数のばらつきを補償し、低ジッタで大きな電源電圧・温度変動耐性を実現する。

【解決手段】第1の発振回路および第2の発振回路と、第2の発振回路が出力するクロックと参照クロックを周波数比較し、その周波数誤差に応じた周波数制御信号Aで第2の発振回路および第1の発振回路の発振周波数を制御するPLL手段とを備えたクロックデータ再生回路において、第1〜第2の発振回路の回路間ばらつきによる発振周波数のずれを調整する回路間ばらつき調整信号Ca,Cbを入力する端子を備え、第1〜第2の発振回路はそれぞれ2つの制御端子を備え、それぞれの一方の制御端子に周波数制御信号Aを入力し、第1の発振回路の他方の制御端子に回路間ばらつき調整信号Caを入力し、第2の発振回路の他方の制御端子に回路間ばらつき調整信号Cbを入力する構成。

(もっと読む)

発振器

【課題】 位相雑音特性を劣化させることなく可変周波数帯域の広帯域化を図ることができる発振器を提供する。

【解決手段】 可変周波数帯域の異なる複数の電圧制御発振器(15a、15b)と、複数の電圧制御発振器からの出力のいずれかを選択出力する切替器16と、パラメータに基づいて発振器出力が所定の周波数となるよう制御するデジタルPLL回路13とを備え、制御部18が、各電圧制御発振器に対応して、良好な位相雑音特性が得られるループゲイン及びダンピングファクタを記憶しておき、外部から周波数の値が入力されると、入力された周波数の値に応じて電圧制御発振器を選択し、当該電圧制御発振器からの出力を選択出力するよう切替器16を切り替え、当該電圧制御発振器に対応して記憶されているループゲイン及びダンピングファクタをパラメータとしてデジタルPLL回路13に設定する発振器としている。

(もっと読む)

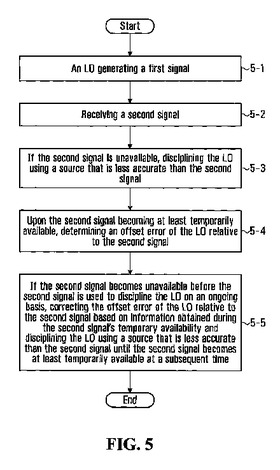

局部発振器を調整する装置及び方法

装置は、タイミング情報、周波数情報、位相情報及びそれらの組み合わせの内の少なくとも1つを有する第1信号を生成する局部発振器(LO)と、タイミング情報、周波数情報、位相情報及びそれらの組み合わせの内の少なくとも1つを有する第2信号を受信する入力を有するLOエラー補正部とを有し、第2信号はLOを調整するために使用され、LOエラー補正部は、第2信号がLOを調整するために利用可能でなくなった場合に、第2信号より精度が低いソースを用いてLOを調整し、第2信号が少なくとも一次的に利用可能になった場合に、第2信号に対するLOのオフセットエラーを判定し、当該装置が継続的にLOを調整するために第2信号を利用する前に、第2信号が利用可能でなくなった場合、第2信号が一次的に利用可能であった期間内に取得された情報に基づいて、第2信号に対するLOのオフセットエラーを補正し、第2信号が以後に少なくとも一次的に利用可能になるまで、第2信号よりも精度が低いソースを用いてLOを調整する。  (もっと読む)

(もっと読む)

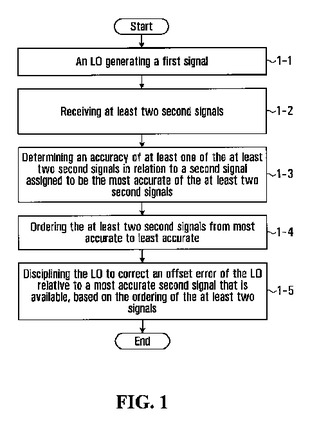

局部発振器を調整する装置及び方法

装置は、タイミング情報、周波数情報、位相情報及びそれらの組み合わせの内の少なくとも1つを有する第1信号を生成する局部発振器(LO)と、少なくとも2つの入力を有する優先制御部とを有し、入力の各々は、タイミング情報、周波数情報、位相情報及びそれらの組み合わせの内の少なくとも1つを有する第2信号をそれぞれ受信し、優先制御部は、少なくとも2つの第2信号の内の少なくとも1つの第2信号の精度を判定し、何れかの第2信号は少なくとも2つの第2信号の内で精度が最高であるように指定され、優先制御部は、最高精度から最低精度へ少なくとも2つの第2信号を順番に並べ、少なくとも2つの第2信号の順番に基づいて、装置に利用可能な最高精度の第2信号に対してLOのオフセットエラーを補正するように、LOが調整される。  (もっと読む)

(もっと読む)

周波数発生のための装置及び方法

広帯域周波数発生器は、フリップチップパッケージ内の同一のダイに配置された異なる周波数帯域のための2つ以上の発振器を有する。2つの発振器の誘導子間の結合は、一方の誘導子がダイに配置され、他方の誘導子がパッケージに配置され、これら誘導子がハンダバンプの直径によって離されることで、減少させられる。弱結合されたこれら誘導子では、一方の発振器の帯域を増加させるために他方の発振器のLCタンク回路の操作をしたり、その逆を行ったりできる。一方の発振器の振動の好ましくないモードを防ぐことは、他方の発振器の粗同調バンクの全容量といった大容量を他方の発振器のLCタンク回路に与えることによって達成され得る。好ましくないモードを防ぐことは、他方の発振器のLCタンクのQファクタを減少させ、タンク回路内の損失を増加させることによっても達成され得る。 (もっと読む)

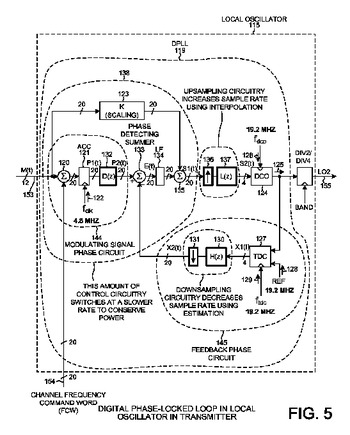

異なるサンプルレートで動作する部分を有するデジタル位相同期ループ

デジタル位相同期ループ(DPLL)は、DCO出力信号及び基準クロックを受信し及びデジタル値の第1のストリームを出力する時間−デジタル変換器(TDC)を含む。TDCを高レートでクロックすることによって量子化雑音が低減される。ダウンサンプリング回路は、第1のストリームを第2のストリームに変換する。第2のストリームは、DPLLの制御部が電力消費量を低減させるためにより低いレートで切り替わることができるようにDPLLの位相検出加算器に供給される。従って、DPLLは、マルチレートDPLLと呼ばれる。制御部によって出力されたデジタルチューニングワードの第3のストリームは、DCOをより高いレートでクロックし、それによってデジタルイメージを低減させることができるようにDCOに供給される前にアップサンプリングされる。受信機用途においては、アップサンプリングは行われず、DCOはより低いレートでクロックされ、それによって電力消費量をさらに低減させる。  (もっと読む)

(もっと読む)

電圧制御発振器

【課題】発振周波数のばらつきを抑えることができる電圧制御発振器を提供する。

【解決手段】本発明による電圧制御発振器は、直列に接続されたN(Nは2以上の整数)個の反転差動増幅器(9)を備えている。N個の反転差動増幅器(9)の各々は、所定の電圧値の定電圧(Vcn1)と制御電圧(Vcnt)とに応じて動作する。N個の反転差動増幅器(9)の各々の動作電流は、定電圧(Vcn1)に応じた電流と、制御電圧(Vcnt)に応じた電流とを加算した電流の値で直接定まる。

(もっと読む)

周波数同期装置、受信機および周波数同期方法

【課題】インパルス状の外乱が生じる環境でも、精度の良い周波数同期を確立することができる周波数同期装置を得ること。

【解決手段】再生周波数を受信信号に同期させる周波数同期制御を行う周波数同期装置であって、受信信号に基づいて周波数偏差を求める周波数偏差検出部2と、周波数偏差の時間変化量を算出する差分部3と、時間変化量に基づいて、前記周波数偏差を周波数制御値として用いるか否かを示す制御値選択信号を生成する観測部6と、制御値選択信号が周波数偏差を周波数制御値として用いないことを示す値であった場合には、過去の周波数制御値に基づいてその時点での周波数制御値の推定値である推定制御値を求め、求めた推定制御値を周波数制御値として選択するホールド部7と、を備える。

(もっと読む)

基準周波数発生装置

【課題】リファレンス信号が取得できなくなっても長時間にわたって高精度な基準周波数信号を出力可能で、使用温度範囲が広く、安価な基準周波数発生装置を提供する。

【解決手段】基準周波数発生装置11は、GPS受信機21と、PLL回路31と、検出器28と、記憶部29と、制御部22と、を備える。PLL回路31は、GPS受信機21からのリファレンス信号に基づいて得られた同期制御信号に基づき、デジタル制御発振器26を制御する。記憶部29には、同期制御信号の制御値と、そのときの電圧値及び温度と、の対応関係が記憶されている。リファレンス信号が得られない場合、制御部22は、前記対応関係と、検出器28が検出した電圧及び温度と、に基づいて自走制御信号を決定し、デジタル制御発振器26を制御する。

(もっと読む)

温特補正機能付き発振回路およびその製造方法

【課題】 発振周波数を補正するためのメモリなどが不要な温特補正機能付き発振回路およびその製造方法を実現する。

【解決手段】 温特補正機能付き発振回路10は、第1の発振回路21と、第2の発振回路22と、第1の発振回路21が発生する発振周波数を理想の発振周波数に近い発振周波数に補正するための補正回路50とを備える。補正回路50は、第1の発振回路21の発振周波数f1と、第2の発振回路22の発振周波数f2との差分(f1−f2)を検出し、その検出した差分に補正係数αを乗じ(α・(f1−f2))、その補正された差分を第1の発振回路21の発振周波数に加算し(f1+α・(f1−f2))、それを出力する動作を行う。

(もっと読む)

クロックデータ再生回路

【課題】複数のVCO間の発振周波数のばらつきを補償し、ジッタを低減する。

【解決手段】第1の発振回路および第2の発振回路はそれぞれ2つの周波数制御端子を備え、それぞれの一方の周波数制御端子に周波数制御信号Aを入力する構成であり、第2の発振回路の他方の周波数制御端子に固定の周波数制御信号Bを与え、第1の発振回路および第2の発振回路の各発振周波数を比較し、その周波数誤差に応じた周波数制御信号Cを第1の発振回路の他方の周波数制御端子に与えるばらつき補償回路を備える。

(もっと読む)

通信装置及びクロック補正方法

【課題】GPS信号を正常に受信できない期間においても、ダブルオーブン型のOCXOを用いることなく、精度の高いクロック信号を用いて動作できる通信装置を提供する。

【解決手段】無線基地局は、水晶発振器11が発生させる発振パルス信号Pxoからクロック信号CLKを生成する生成部13と、GPS受信機12が受信するGPS信号から得られる基準パルス信号Prefを用いてクロック信号CLKの周波数誤差を補正する誤差補正部15と、温度を計測する温度センサ14と、誤差補正部15が補正した周波数誤差を示す誤差補正値を、誤差補正部15が補正を行った際の温度と対応付けて記憶する補正値記憶部16とを備える。基準パルス信号Prefが得られなくなった場合、誤差補正部15は、温度センサ14が計測する温度に対応する誤差補正値を補正値記憶部16から取得し、取得した誤差補正値を用いて周波数誤差を補正する。

(もっと読む)

81 - 100 / 367

[ Back to top ]